摘 要:本文介绍了一种基于FPGA的线阵CCD数据采集系统的实现方法。该系统在Altera的Cyclone EP1C6Q240C8上实现,使用SoPC Builder开发组件定制CPU软核处理器和系统所需的IP模块,CPU软核处理器作为微控制器实现逻辑控制和数据采集功能,用硬件描述语言编程实现CCD驱动电路的设计。

关键词:CCD;数据采集;Nios II

引言

CCD(Charge Coupled Devices,电荷耦合器件)具有光电转换、信息存储等功能,而且集成度高、动态范围大、线性好、信噪比高,在很多领域都得到了广泛应用。CCD有面阵和线阵之分,面阵CCD主要用于摄像、图像处理、数据存储和机器人视觉等领域;线阵CCD的应用也很广泛,像光谱分析、测径,测量微小位移等。

本文介绍了一种在FPGA片内利用SoPC技术实现的线阵CCD数据采集系统,系统中的CCD选用东芝公司的TCD103D,这是2592像元的二相线阵CCD;ADC选用TLC876,精度为10位,转换速率20MSPS。整个系统在一片FPGA(EP1C6Q240C8)上完成,在Quartus II软件中用硬件描述语言实现CCD的驱动电路和A/D采样控制器的设计。使用SoPC Builder定制了一个32位软核处理器作为微控制器,协调CCD驱动电路、A/D采样控制电路之间的工作时序,完成数据采集、存储等功能。系统分3部分:硬件电路、驱动电路和数据采集部分。

系统硬件设计

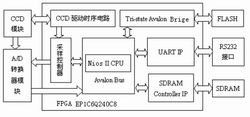

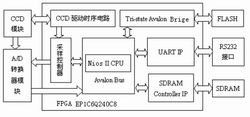

硬件平台结构见图1。系统中的UART和SDRAM Controller是SoPC Builder内建的IP核库中的IP模块,通过Avalon Bus和Nios II CPU相连。SoPC Builder能自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调Avalon Bus上各功能模块的工作。Nios II CPU是系统的核心,协调CCD驱动电路、A/D采样控制电路之间的工作时序,完成数据采集、存储和数据传输。SDRAM作为数据缓存器,软件程序和配置文件存储在外扩的Flash中。系统通过RS-232接口和计算机相连,接收计算机的控制命令。CCD工作时要求驱动脉冲的幅值在11V以上(典型值为12V),因此,CCD模块包含一个电平转换电路,将FPGA输出的电平转换成12V。

驱动电路设计

FPGA具有集成度高、速度快、可靠性好及硬件电路易于编程等特点,非常适合驱动电路的设计。CCD驱动电路和A/D采样控制电路在Quartus II软件中编程实现,产生CCD和ADC所需的工作时序。

[b]CCD驱动电路设计

[/b] TCD103D是一种高灵敏度、低暗电流、2592像元的二相线阵CCD图像传感器。分辨率为11mm,它在4路驱动信号作用下输出OS和DOS信号。正常工作时先输出64个哑元信号,然后连续输出S1"S2592有效像素单元信号。S2592信号输出后,又输出28个哑元信号,以后便是空驱动。DOS是补偿输出信号。4路驱动信号分别是转移信号SH、两相时钟信号Φ1、Φ2 和复位信号RS。SH 的周期就是器件的光积分时间。

系统硬件设计

硬件平台结构见图1。系统中的UART和SDRAM Controller是SoPC Builder内建的IP核库中的IP模块,通过Avalon Bus和Nios II CPU相连。SoPC Builder能自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调Avalon Bus上各功能模块的工作。Nios II CPU是系统的核心,协调CCD驱动电路、A/D采样控制电路之间的工作时序,完成数据采集、存储和数据传输。SDRAM作为数据缓存器,软件程序和配置文件存储在外扩的Flash中。系统通过RS-232接口和计算机相连,接收计算机的控制命令。CCD工作时要求驱动脉冲的幅值在11V以上(典型值为12V),因此,CCD模块包含一个电平转换电路,将FPGA输出的电平转换成12V。

驱动电路设计

FPGA具有集成度高、速度快、可靠性好及硬件电路易于编程等特点,非常适合驱动电路的设计。CCD驱动电路和A/D采样控制电路在Quartus II软件中编程实现,产生CCD和ADC所需的工作时序。

[b]CCD驱动电路设计

[/b] TCD103D是一种高灵敏度、低暗电流、2592像元的二相线阵CCD图像传感器。分辨率为11mm,它在4路驱动信号作用下输出OS和DOS信号。正常工作时先输出64个哑元信号,然后连续输出S1"S2592有效像素单元信号。S2592信号输出后,又输出28个哑元信号,以后便是空驱动。DOS是补偿输出信号。4路驱动信号分别是转移信号SH、两相时钟信号Φ1、Φ2 和复位信号RS。SH 的周期就是器件的光积分时间。

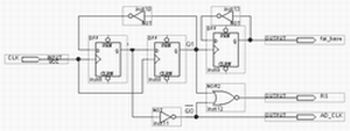

[b]复位脉冲RS的产生

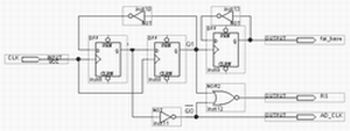

[/b] RS 是使输出扩散二极管复位的复位管控制脉冲,复位一次输出一个信号,脉冲占空比为1:3,典型频率为1MHz。RS 由U1单元产生。如图2所示,单元内两个D触发器构成一个环形计数器,CLK 为4MHz 的时钟脉冲,经分频输出两个1MHz、相差90%26;#176;的方波脉冲和,将这两路脉冲经或非门输出,即可形成RS脉冲。除RS脉冲外,U1单元还产生fai_base脉冲和AD_CLK脉冲。前者频率为0.5MHz,占空比为1:1,用于产生时钟脉冲信号。AD_CLK是ADC的采样时钟信号,频率为1MHz。

[b]复位脉冲RS的产生

[/b] RS 是使输出扩散二极管复位的复位管控制脉冲,复位一次输出一个信号,脉冲占空比为1:3,典型频率为1MHz。RS 由U1单元产生。如图2所示,单元内两个D触发器构成一个环形计数器,CLK 为4MHz 的时钟脉冲,经分频输出两个1MHz、相差90%26;#176;的方波脉冲和,将这两路脉冲经或非门输出,即可形成RS脉冲。除RS脉冲外,U1单元还产生fai_base脉冲和AD_CLK脉冲。前者频率为0.5MHz,占空比为1:1,用于产生时钟脉冲信号。AD_CLK是ADC的采样时钟信号,频率为1MHz。

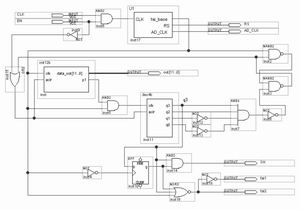

[b]时钟脉冲Φ1和Φ2的产生

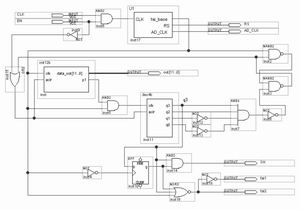

[/b] 时钟脉冲Φ1、Φ2的典型频率为0.5MHz,相位相差180%26;#176;,为避免MOS电容中的信号电荷包向上/下2列模拟移位寄存器的电极转移不完全的情况发生,要求Φ1、Φ2在并行转移时有一个大于SH=1持续时间的宽脉冲。在图3所示的电路中(图中Φ1、Φ2分别用fai1、fai2表示),cnt12b是一个异步清零的加法计数器,当计数值至少大于1341(计数值由光积分时间决定),p1输出高电平,开启dec4b。dec4b是一个异步清零的减法计数器,输出为1100时,立即产生异步清零信号,将两个计数器全部清零,同时生成Φ1、Φ2所需的宽脉冲。

[b]

转移脉冲SH的产生

[/b] SH是使MOS 电容中的信号电荷转移到移位寄存器中的转移栅控制脉冲。如图3所示,dec4b的q3产生的宽脉冲经过一个下降沿触发的DFF,波形滞后q3半个CLK周期,两个信号作与运算,即产生SH脉冲。

EN是驱动电路的使能信号,EN为高电平时,电路工作。

[b]时钟脉冲Φ1和Φ2的产生

[/b] 时钟脉冲Φ1、Φ2的典型频率为0.5MHz,相位相差180%26;#176;,为避免MOS电容中的信号电荷包向上/下2列模拟移位寄存器的电极转移不完全的情况发生,要求Φ1、Φ2在并行转移时有一个大于SH=1持续时间的宽脉冲。在图3所示的电路中(图中Φ1、Φ2分别用fai1、fai2表示),cnt12b是一个异步清零的加法计数器,当计数值至少大于1341(计数值由光积分时间决定),p1输出高电平,开启dec4b。dec4b是一个异步清零的减法计数器,输出为1100时,立即产生异步清零信号,将两个计数器全部清零,同时生成Φ1、Φ2所需的宽脉冲。

[b]

转移脉冲SH的产生

[/b] SH是使MOS 电容中的信号电荷转移到移位寄存器中的转移栅控制脉冲。如图3所示,dec4b的q3产生的宽脉冲经过一个下降沿触发的DFF,波形滞后q3半个CLK周期,两个信号作与运算,即产生SH脉冲。

EN是驱动电路的使能信号,EN为高电平时,电路工作。

[b]A/D采样控制时序的产生

[/b] TLC876以多级流水线结构原理设计而成,在每一个采样时钟的上升沿都启动一次采样,完成一次采样,但从模拟值采样到10位数字量输出有5个时钟周期的延迟。

采样时钟AD_CLK由U1单元产生,频率为1MHz。采样控制电路的作用是协调CCD和TLC876之间的工作时序。CCD正常工作时前后各有64和28个哑元信号,这 92 个哑元信号在 A/D 转换时不需要采样。但是,因为输出信号有5个周期的延迟,实际应采2597个点。采样控制单元的主要功能是:使能信号ENABLE有效后,模块等待当前的积分周期结束,并在下一个积分周期开始时对前64个哑元信号进行计数,等64个信号全部移出后启动采样时钟,ADC在AD_CLK控制下连续对信号进行采样和输出。

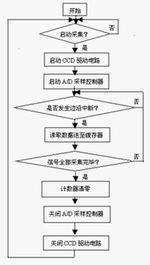

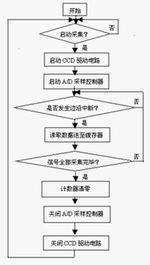

[b]数据采集系统设计

[/b] Nios II CPU是系统的核心,协调各模块之间的工作,实现数据采集功能。当计算机发出控制信号时,微处理器启动CCD驱动电路和A/D采样控制电路,CCD在驱动时序控制下将堆积的电荷导出并开始新的积分周期。A/D采样控制电路等待当前积分周期结束后产生TLC876的采样时钟AD_CLK。AD_CLK和Nios II CPU的一个I/O相连,该I/O口定制时设置成边沿中断。因此,在每个AD_CLK的上升沿启动一次采样的同时产生一次中断,通知CPU读取转换好的数据。CPU将读取的数据暂存在SDRAM中,一次数据采集完成后,由微处理器将采样控制器中的计数器清零并关闭采样控制单元和CCD驱动电路。这部分采用C语言在Nios II的集成开发环境(IDE)中实现。软件流程如图4所示。

结语

本文提出了一种基于FPGA的线阵CCD数据采集系统的实现方法。该系统在Altera公司的Cyclone FPGA上实现,使用SoPC Builder开发组件定制系统所需的IP模块,具有开发周期短、集成度高等特点。软硬件均采用编程实现,设计灵活,在实际应用中收到很好的效果。

参考文献:

1 饶程,袁祥辉.积分时间和频率同时可调的线阵CCD驱动. 医疗卫生装备.2005年第10 期.

2 仁爱锋,初秀琴等.基于FPGA的嵌入式系统设计.西安:西安电子科技大学出版社,2004

3 TOSHIBA. TCD103D Datasheet

[b]A/D采样控制时序的产生

[/b] TLC876以多级流水线结构原理设计而成,在每一个采样时钟的上升沿都启动一次采样,完成一次采样,但从模拟值采样到10位数字量输出有5个时钟周期的延迟。

采样时钟AD_CLK由U1单元产生,频率为1MHz。采样控制电路的作用是协调CCD和TLC876之间的工作时序。CCD正常工作时前后各有64和28个哑元信号,这 92 个哑元信号在 A/D 转换时不需要采样。但是,因为输出信号有5个周期的延迟,实际应采2597个点。采样控制单元的主要功能是:使能信号ENABLE有效后,模块等待当前的积分周期结束,并在下一个积分周期开始时对前64个哑元信号进行计数,等64个信号全部移出后启动采样时钟,ADC在AD_CLK控制下连续对信号进行采样和输出。

[b]数据采集系统设计

[/b] Nios II CPU是系统的核心,协调各模块之间的工作,实现数据采集功能。当计算机发出控制信号时,微处理器启动CCD驱动电路和A/D采样控制电路,CCD在驱动时序控制下将堆积的电荷导出并开始新的积分周期。A/D采样控制电路等待当前积分周期结束后产生TLC876的采样时钟AD_CLK。AD_CLK和Nios II CPU的一个I/O相连,该I/O口定制时设置成边沿中断。因此,在每个AD_CLK的上升沿启动一次采样的同时产生一次中断,通知CPU读取转换好的数据。CPU将读取的数据暂存在SDRAM中,一次数据采集完成后,由微处理器将采样控制器中的计数器清零并关闭采样控制单元和CCD驱动电路。这部分采用C语言在Nios II的集成开发环境(IDE)中实现。软件流程如图4所示。

结语

本文提出了一种基于FPGA的线阵CCD数据采集系统的实现方法。该系统在Altera公司的Cyclone FPGA上实现,使用SoPC Builder开发组件定制系统所需的IP模块,具有开发周期短、集成度高等特点。软硬件均采用编程实现,设计灵活,在实际应用中收到很好的效果。

参考文献:

1 饶程,袁祥辉.积分时间和频率同时可调的线阵CCD驱动. 医疗卫生装备.2005年第10 期.

2 仁爱锋,初秀琴等.基于FPGA的嵌入式系统设计.西安:西安电子科技大学出版社,2004

3 TOSHIBA. TCD103D Datasheet

编辑: 引用地址:基于FPGA的线阵CCD数据采集系统

系统硬件设计

硬件平台结构见图1。系统中的UART和SDRAM Controller是SoPC Builder内建的IP核库中的IP模块,通过Avalon Bus和Nios II CPU相连。SoPC Builder能自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调Avalon Bus上各功能模块的工作。Nios II CPU是系统的核心,协调CCD驱动电路、A/D采样控制电路之间的工作时序,完成数据采集、存储和数据传输。SDRAM作为数据缓存器,软件程序和配置文件存储在外扩的Flash中。系统通过RS-232接口和计算机相连,接收计算机的控制命令。CCD工作时要求驱动脉冲的幅值在11V以上(典型值为12V),因此,CCD模块包含一个电平转换电路,将FPGA输出的电平转换成12V。

驱动电路设计

FPGA具有集成度高、速度快、可靠性好及硬件电路易于编程等特点,非常适合驱动电路的设计。CCD驱动电路和A/D采样控制电路在Quartus II软件中编程实现,产生CCD和ADC所需的工作时序。

[b]CCD驱动电路设计

[/b] TCD103D是一种高灵敏度、低暗电流、2592像元的二相线阵CCD图像传感器。分辨率为11mm,它在4路驱动信号作用下输出OS和DOS信号。正常工作时先输出64个哑元信号,然后连续输出S1"S2592有效像素单元信号。S2592信号输出后,又输出28个哑元信号,以后便是空驱动。DOS是补偿输出信号。4路驱动信号分别是转移信号SH、两相时钟信号Φ1、Φ2 和复位信号RS。SH 的周期就是器件的光积分时间。

系统硬件设计

硬件平台结构见图1。系统中的UART和SDRAM Controller是SoPC Builder内建的IP核库中的IP模块,通过Avalon Bus和Nios II CPU相连。SoPC Builder能自动产生每个模块的HDL文件,同时自动产生一些必要的仲裁逻辑来协调Avalon Bus上各功能模块的工作。Nios II CPU是系统的核心,协调CCD驱动电路、A/D采样控制电路之间的工作时序,完成数据采集、存储和数据传输。SDRAM作为数据缓存器,软件程序和配置文件存储在外扩的Flash中。系统通过RS-232接口和计算机相连,接收计算机的控制命令。CCD工作时要求驱动脉冲的幅值在11V以上(典型值为12V),因此,CCD模块包含一个电平转换电路,将FPGA输出的电平转换成12V。

驱动电路设计

FPGA具有集成度高、速度快、可靠性好及硬件电路易于编程等特点,非常适合驱动电路的设计。CCD驱动电路和A/D采样控制电路在Quartus II软件中编程实现,产生CCD和ADC所需的工作时序。

[b]CCD驱动电路设计

[/b] TCD103D是一种高灵敏度、低暗电流、2592像元的二相线阵CCD图像传感器。分辨率为11mm,它在4路驱动信号作用下输出OS和DOS信号。正常工作时先输出64个哑元信号,然后连续输出S1"S2592有效像素单元信号。S2592信号输出后,又输出28个哑元信号,以后便是空驱动。DOS是补偿输出信号。4路驱动信号分别是转移信号SH、两相时钟信号Φ1、Φ2 和复位信号RS。SH 的周期就是器件的光积分时间。

[b]复位脉冲RS的产生

[/b] RS 是使输出扩散二极管复位的复位管控制脉冲,复位一次输出一个信号,脉冲占空比为1:3,典型频率为1MHz。RS 由U1单元产生。如图2所示,单元内两个D触发器构成一个环形计数器,CLK 为4MHz 的时钟脉冲,经分频输出两个1MHz、相差90%26;#176;的方波脉冲和,将这两路脉冲经或非门输出,即可形成RS脉冲。除RS脉冲外,U1单元还产生fai_base脉冲和AD_CLK脉冲。前者频率为0.5MHz,占空比为1:1,用于产生时钟脉冲信号。AD_CLK是ADC的采样时钟信号,频率为1MHz。

[b]复位脉冲RS的产生

[/b] RS 是使输出扩散二极管复位的复位管控制脉冲,复位一次输出一个信号,脉冲占空比为1:3,典型频率为1MHz。RS 由U1单元产生。如图2所示,单元内两个D触发器构成一个环形计数器,CLK 为4MHz 的时钟脉冲,经分频输出两个1MHz、相差90%26;#176;的方波脉冲和,将这两路脉冲经或非门输出,即可形成RS脉冲。除RS脉冲外,U1单元还产生fai_base脉冲和AD_CLK脉冲。前者频率为0.5MHz,占空比为1:1,用于产生时钟脉冲信号。AD_CLK是ADC的采样时钟信号,频率为1MHz。

[b]时钟脉冲Φ1和Φ2的产生

[/b] 时钟脉冲Φ1、Φ2的典型频率为0.5MHz,相位相差180%26;#176;,为避免MOS电容中的信号电荷包向上/下2列模拟移位寄存器的电极转移不完全的情况发生,要求Φ1、Φ2在并行转移时有一个大于SH=1持续时间的宽脉冲。在图3所示的电路中(图中Φ1、Φ2分别用fai1、fai2表示),cnt12b是一个异步清零的加法计数器,当计数值至少大于1341(计数值由光积分时间决定),p1输出高电平,开启dec4b。dec4b是一个异步清零的减法计数器,输出为1100时,立即产生异步清零信号,将两个计数器全部清零,同时生成Φ1、Φ2所需的宽脉冲。

[b]

转移脉冲SH的产生

[/b] SH是使MOS 电容中的信号电荷转移到移位寄存器中的转移栅控制脉冲。如图3所示,dec4b的q3产生的宽脉冲经过一个下降沿触发的DFF,波形滞后q3半个CLK周期,两个信号作与运算,即产生SH脉冲。

EN是驱动电路的使能信号,EN为高电平时,电路工作。

[b]时钟脉冲Φ1和Φ2的产生

[/b] 时钟脉冲Φ1、Φ2的典型频率为0.5MHz,相位相差180%26;#176;,为避免MOS电容中的信号电荷包向上/下2列模拟移位寄存器的电极转移不完全的情况发生,要求Φ1、Φ2在并行转移时有一个大于SH=1持续时间的宽脉冲。在图3所示的电路中(图中Φ1、Φ2分别用fai1、fai2表示),cnt12b是一个异步清零的加法计数器,当计数值至少大于1341(计数值由光积分时间决定),p1输出高电平,开启dec4b。dec4b是一个异步清零的减法计数器,输出为1100时,立即产生异步清零信号,将两个计数器全部清零,同时生成Φ1、Φ2所需的宽脉冲。

[b]

转移脉冲SH的产生

[/b] SH是使MOS 电容中的信号电荷转移到移位寄存器中的转移栅控制脉冲。如图3所示,dec4b的q3产生的宽脉冲经过一个下降沿触发的DFF,波形滞后q3半个CLK周期,两个信号作与运算,即产生SH脉冲。

EN是驱动电路的使能信号,EN为高电平时,电路工作。

[b]A/D采样控制时序的产生

[/b] TLC876以多级流水线结构原理设计而成,在每一个采样时钟的上升沿都启动一次采样,完成一次采样,但从模拟值采样到10位数字量输出有5个时钟周期的延迟。

采样时钟AD_CLK由U1单元产生,频率为1MHz。采样控制电路的作用是协调CCD和TLC876之间的工作时序。CCD正常工作时前后各有64和28个哑元信号,这 92 个哑元信号在 A/D 转换时不需要采样。但是,因为输出信号有5个周期的延迟,实际应采2597个点。采样控制单元的主要功能是:使能信号ENABLE有效后,模块等待当前的积分周期结束,并在下一个积分周期开始时对前64个哑元信号进行计数,等64个信号全部移出后启动采样时钟,ADC在AD_CLK控制下连续对信号进行采样和输出。

[b]数据采集系统设计

[/b] Nios II CPU是系统的核心,协调各模块之间的工作,实现数据采集功能。当计算机发出控制信号时,微处理器启动CCD驱动电路和A/D采样控制电路,CCD在驱动时序控制下将堆积的电荷导出并开始新的积分周期。A/D采样控制电路等待当前积分周期结束后产生TLC876的采样时钟AD_CLK。AD_CLK和Nios II CPU的一个I/O相连,该I/O口定制时设置成边沿中断。因此,在每个AD_CLK的上升沿启动一次采样的同时产生一次中断,通知CPU读取转换好的数据。CPU将读取的数据暂存在SDRAM中,一次数据采集完成后,由微处理器将采样控制器中的计数器清零并关闭采样控制单元和CCD驱动电路。这部分采用C语言在Nios II的集成开发环境(IDE)中实现。软件流程如图4所示。

结语

本文提出了一种基于FPGA的线阵CCD数据采集系统的实现方法。该系统在Altera公司的Cyclone FPGA上实现,使用SoPC Builder开发组件定制系统所需的IP模块,具有开发周期短、集成度高等特点。软硬件均采用编程实现,设计灵活,在实际应用中收到很好的效果。

参考文献:

1 饶程,袁祥辉.积分时间和频率同时可调的线阵CCD驱动. 医疗卫生装备.2005年第10 期.

2 仁爱锋,初秀琴等.基于FPGA的嵌入式系统设计.西安:西安电子科技大学出版社,2004

3 TOSHIBA. TCD103D Datasheet

[b]A/D采样控制时序的产生

[/b] TLC876以多级流水线结构原理设计而成,在每一个采样时钟的上升沿都启动一次采样,完成一次采样,但从模拟值采样到10位数字量输出有5个时钟周期的延迟。

采样时钟AD_CLK由U1单元产生,频率为1MHz。采样控制电路的作用是协调CCD和TLC876之间的工作时序。CCD正常工作时前后各有64和28个哑元信号,这 92 个哑元信号在 A/D 转换时不需要采样。但是,因为输出信号有5个周期的延迟,实际应采2597个点。采样控制单元的主要功能是:使能信号ENABLE有效后,模块等待当前的积分周期结束,并在下一个积分周期开始时对前64个哑元信号进行计数,等64个信号全部移出后启动采样时钟,ADC在AD_CLK控制下连续对信号进行采样和输出。

[b]数据采集系统设计

[/b] Nios II CPU是系统的核心,协调各模块之间的工作,实现数据采集功能。当计算机发出控制信号时,微处理器启动CCD驱动电路和A/D采样控制电路,CCD在驱动时序控制下将堆积的电荷导出并开始新的积分周期。A/D采样控制电路等待当前积分周期结束后产生TLC876的采样时钟AD_CLK。AD_CLK和Nios II CPU的一个I/O相连,该I/O口定制时设置成边沿中断。因此,在每个AD_CLK的上升沿启动一次采样的同时产生一次中断,通知CPU读取转换好的数据。CPU将读取的数据暂存在SDRAM中,一次数据采集完成后,由微处理器将采样控制器中的计数器清零并关闭采样控制单元和CCD驱动电路。这部分采用C语言在Nios II的集成开发环境(IDE)中实现。软件流程如图4所示。

结语

本文提出了一种基于FPGA的线阵CCD数据采集系统的实现方法。该系统在Altera公司的Cyclone FPGA上实现,使用SoPC Builder开发组件定制系统所需的IP模块,具有开发周期短、集成度高等特点。软硬件均采用编程实现,设计灵活,在实际应用中收到很好的效果。

参考文献:

1 饶程,袁祥辉.积分时间和频率同时可调的线阵CCD驱动. 医疗卫生装备.2005年第10 期.

2 仁爱锋,初秀琴等.基于FPGA的嵌入式系统设计.西安:西安电子科技大学出版社,2004

3 TOSHIBA. TCD103D Datasheet

上一篇:基于RISC技术的8位微控制器设计

下一篇:在CPLD管理下实现高效多串口中断源

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TC52N3644ECTRT

TC52N3644ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号