ARM芯片是目前在嵌入式系统中应用比较广泛的一种芯片,由于可以运行操作系统,以及拥有包括LCD、串口通讯、网络通讯、存储芯片等大量外围接口芯片的支持,使得ARM广泛应用于检测、通讯、控制等领域。

本文以ARM 920T核的S3C24449芯片作为微控制器,在TQ2440开发板进行串口扩展,利用开发板上的系统总线接口和通用输入输出接口分别与扩展串口相连,达到同时与多台串口设备并行通信的目标。

1 硬件介绍

1.1 异步通信芯片——TL16C554A

TL16C554A含有4路异步通信单元(Asynchronous Communications Element ACE),每路ACE均可接收外围设备的串行数据,并将其转换为并行数据供CPU使用,也可将CPU的并行数据转换为串行数据发送到外围设备。

TL16C554A引脚如图1所示。各主要引脚的功能说明如下:A0—A2用于选择片内寄存器;D0—D7进行数据传输;IOR和IOW进行读写;CSA,CSB,CSC,CSD用于选定具体串口;XTAL1,XTAL2可接晶振或外部时钟信号;INTA,INTB,INTC,INTD为4个独立外部中断信号;RXA,RXB,RXC,RXD:串行接收数据;TXA,TXB,TXC,TXD:串行发送数据。

1.2 系统总线接口、GPIO接口

TQ2440开发板以S3C2440芯片作为控制器,主频400MHz,外扩64 M内存,256 M闪存,并集成了多种接口,本设计中使用开发板上的系统总线接口与GPIO(通用输入输出接口)和TL16c554A相连。[page]

1.2.1 系统总线接口

本开发板上的系统总线接口中共包含8根地址线(A0~A6,A24),16根数据线(DATA0~DATA15),4个中断,4个片选等信号,该总线接口集成了IDE所需的所有引出点,方便用户扩展,接口电路如图2所示。

1.2.2 GPIO接口

GPIO是通用输入输出口的简称,本开发板带有一个40Pin 2.0 mm间距的GPIO接口,如图3所示。不仅包含很多富余的GPIO引脚,还包含了一些其他CPU引脚,如AIN0~AIN3,CLKOUT等。如SPI接口、I2C接口、LED1~LED4(实际就是GPB5~GPB8),它们其实也是GPIO,不过是以特殊功能接口来标称定义的,这些都可以通过相应的CPU寄存器来设置更改它们的用途。

2 硬件设计

在硬件设计中,将TQ2440开发板扩展口的地址线ADDR0,ADDR1,ADDR2与16C554A的A0,A1,A2直接相连,TL16C554A芯片A0,A1,A2的不同的组合代表芯片内不同的寄存器。

在与TL16C554A的连接中,由于TL16C554A只有8位,只需TL16C554A的D0~D7和开发板的DATA0~DATA7相连。读写信号直接相连(开发板的nOE、nWE分别与串口的IOE、IOW直连)。由于16C554芯片启动要有一定的宽度的脉冲,可以从GPA 12输出一定的宽度的脉冲来完成。

每片16C554A可以将数据总线上的数据和4个串行端口的数据进行相互的转化,两片16C554A芯片共有8个串行口,通过3根地址线ADDR4,ADDR5,ADDR24经过74LS138选择8个串口中的任意一个。

[page]

因为方案采用中断方式,所以将NSEL置高位,即允许芯片中断。16C554A有INTA、INTB、INTC、IN TD4个中断线,第一片扩展串口与系统总线的EINT1,EINT2,EINT5,EINT6相连,第二片扩展串口与GPIO中的EINT11,EINT13,EINT15,EIN39中断相连,使得任一片芯片的任意的端口都能产生中断。

S3C2440的A0,A1,A2,A4,A5,A24通过不同组合可以选择8个不同的端口。nGCS5与74LS138译码器片选脚相连,根据S3C2440对地址空间的定义,这样就确定了第一片16C554A扩展芯片4个端口的访问地址为0X28000000,0X28000010,0X28000020,0X28000030,第二片16C554A扩展芯片4个端口的访问地址为0X29000000,0X29000010,0X29000020,0X29000030,根据端口基地址就可以确定片内的各个寄存器地址。具体连接如图4所示。

3 驱动程序移植

软件设计主要是为设备编写驱动程序。设备驱动是介于硬件和操作系统之间的软件接口,主要功能包括:探测和初始化设备;从设备接收数据并提交给内核;从内核接收数据送到设备;检测和处理设备错误。

串口驱动程序从上到下分为4层:终端设备层、行规程、串口抽象层、串口芯片层。其中,串口芯片层与具体的芯片相关,主要是向串口抽象层提供串口芯片所用的资源,还进行一些与芯片相关的设置。

TL16C554A扩展串口芯片属于标准串口,内核的串口驱动程序对它支持它的驱动程序就是Linux内核代码中的driver/seria/8250.c.入口函数是serial8250_init,它用于向串口抽象层提供注册串口的物理信息。串口的物理信息主要有两类:访问地址和中断号。所以只要设置好这两类物理信息,就可以驱动扩展串口了,图5为驱动程序移植流程。

3.1 构建扩展串口的数据结构

串口的物理信息存储在内核源程序arch/arm/plats3c24xx/common-smdk.c中,所以主要工作是在commonsmdk.c源文件中增加三段代码:

1)增加头文件

源程序中要包含头文件linux/serial_8250.h,用于告诉编译器使用8250.c作为扩展串口的源程序;

[page]

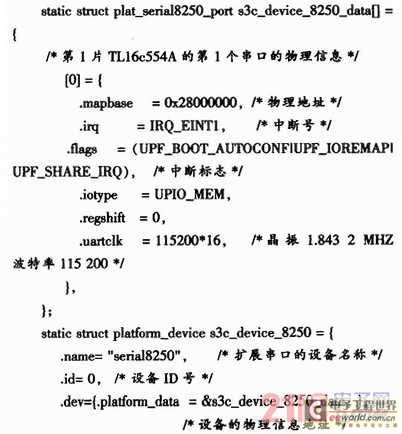

2)增加串口的物理信息在common-smdk.c文件中增加8个元素的structplat_serial8250_port结构数组,并加入数据项,如每个串口使用的物理地址和中断号等信息,使系统启动后能找到串口。下面以第1片TL16c554A的第1个串口CSA为例说明如何在源程序中添加数据结构:

3)加入内核设备列表中

把串口设备(s3c_deviee_8250代表TL16c550A芯片)加入到内核的platform_device结构中

static struct platform_device_initdata*smdk_devs[]={ &s3c_device_8250,};

3.2 增加开发板代码使串口可用

主要修改drivers/serial/8250.c文件,使BANK5以8位的位宽访问TL16c554A芯片,并指定芯片的中断触发方式。

1)增加头文件asm/areh-s3c2410/regs-mem.h,定位TL16c554A所在的地址空间;

2)设置存储控制器的BANK5的位宽(8位)

在serial8250_init(void)初始化函数中把存储控制器的位宽寄存器设为0X22011110;

3)指定中断触发方式

因为TL160554A的中断信号INTA、INTB、INTC、INTD为高电平有效,所以需将INTA、INTB、INTC、INTD上升沿触发,在调用中断函数req-uest_irq前应设置中断标志为IRQF_TRIGGER_RISING。

3. 3 增加内核配置项

在内核源代码的driver/serial/Kconfig中增加config条目CONFIG_SERIAL_EXTEND_S3C24XX,内核编译时选定该选项可以把驱动程序编译进系统中。

4 测试扩展串口

测试的工作包括编译内核、在根文件系统中增加设备文件、修改系统初始化脚本、测试扩展串口几个步骤。图6为串口测试流程图。

1)配置、编译内核

配置内核时增加配置选项CONFIG_SERIAL_EXTEND_S3C24XX,执行“make uImage”命令,编译内核。

2)修改根文件系统

在Linux系统中通过设备文件来访问具体的物理设备,故使用mknod命令,增加ttyS0,ttyS1,…,ttyS7设备文件,分别对应两片TL16c554A的8个串口。命令格式如下:

# mknod/dev/ttyS0 c 4 64

3)修改配置文件

在/etc/inittab配置文件中添加ttyS0::askfirat:-/bin/sh

4)测试

把第一个串口与主机相连,设置U-Boot的启动参数为:noinitrd root=/dev/mtdblock2 init=/linuxrc console=ttyS0,重新启动开发板,就能在超级终端下看到linux系统启动信息了。

5 结束语

本文提供了在原有TQ2440开发板中扩展8个串口,采用中断服务的方案,提高了ARM9系统运行效率。在此基础上可以进一步扩大,将串口扩展到12个、16个或者更多。

上一篇:Samsung S3C2440平台上的Vxworks BSP移植

下一篇:基于S3C2440A的Windows CE系统快速启动方案

推荐阅读最新更新时间:2024-03-16 13:04

设计资源 培训 开发板 精华推荐

- ASML在2024 年投资者日会议上就市场机遇提供最新看法

- AMD将裁员4%,以在人工智能芯片领域争取更强的市场地位

- Arm:以高效计算平台为核心,内外协力共筑可持续未来

- NEC收获新超算订单:英特尔CPU+AMD加速器+英伟达交换机

- 高通推出其首款 RISC-V 架构可编程连接模组 QCC74xM,支持 Wi-Fi 6 等协议

- 消息称内存原厂考虑 HBM4 采用无助焊剂键合,进一步降低层间间隙

- 随时随地享受大屏幕游戏:让便携式 4K 超高清 240Hz 游戏投影仪成为现实

- 高信噪比MEMS麦克风驱动人工智能交互

- 里程碑式进展!思特威CMOS图像传感器芯片单月出货超1亿颗!

- 下一代汽车微控制器:意法半导体技术解析

轻松玩转STM32Cube(第2版) (杨百军)

轻松玩转STM32Cube(第2版) (杨百军) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号