0引言

我们在进行嵌入式系统设计的过程中,根据需求,要设计出特定的嵌入式应用系统,而嵌入式应用系统的设计包含硬件系统设计和软件系统设计两个部分,并且这两部分设计是互相关联、密不可分的,嵌入式应用系统的设计经常需要在硬件和软件设计之间进行权衡与折中。因此,这就要求嵌入式系统设计者具有较深厚的硬件和软件基础,并具有熟练应用的能力。在整个设计过程中,硬件设计是系统设计的基础和核心,而各功能部件在整个设计中的调试又是该环节的重点和难点。本文详细介绍嵌入式系统Flash存储器的接口电路的调试。

1 Flash存储器接口电路的引脚信号及各项特性

1.1 Flash存储器接口电路的特点

Flash存储器是一种可在系统(In-System)中进行电擦写,掉电后信息不会丢失的存储器。它具有低功耗、大容量、擦写速度快、可整片或分扇区在系统编程(烧写)、擦除等特点,并且可由内部嵌入算法完成对芯片的操作,因而在各种嵌入式系统中得到了广泛的应用。作为一种非易失性存储器,Flash在系统中通常用于存放程序代码、常量表以及一些在系统掉电后需要保存的用户数据等。常用的Flash为8位或16位数据宽度,编程电压为单3.3V。主要有ATMEL、AMD、HYUNDAI等生产厂商,他们生产的同型器件一般具有相同的电气特性和封装形式,可通用。

1.2以HY57V641620为例的SDRAM接口电路的基本特性

本文以Flash存储器HY29LV160为例,简要描述一下Flash存储器的基本特性:

HY29LV160的单片存储容量为16M位(2M字节),工作电压为2.7V~3.6V,采用48脚TSOP封装或48脚FBGA封装,16位数据宽度,可以以8位(字节模式)或16位(字模式)数据宽度的方式工作。

HY29LV160仅需单3V电压即可完成在系统的编程与擦除操作,通过对其内部的命令寄存器写入标准的命令序列,可对Flash进行编程(烧写)、整片擦除、按扇区擦除以及其它操作。

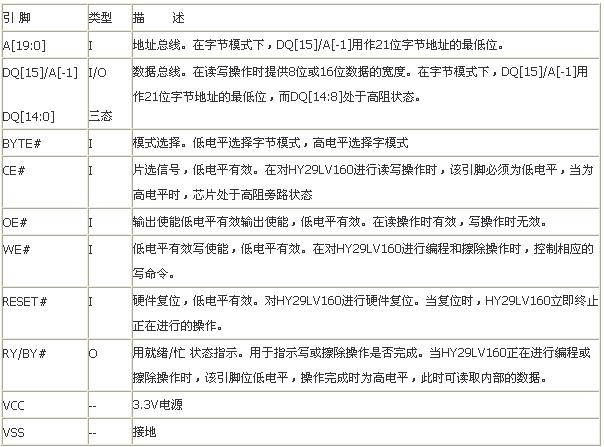

HY29LV160的逻辑框图、引脚分布及信号描述分别如图1和表1所示:

图1 HY29LV160引脚分布(TSOP48封装)

表1 HY29LV160的引脚信号描述

1.3 以HY29LV160为例的Flash接口电路的使用方法

下面,我们使用HY29LV160来构建存储系统。由于ARM微处理器的体系结构支持8位/16位/32位的存储器系统,对应的可以构建8位、16位、32位的Flash存储器系统。32位的存储器系统具有较高的性能,而16位的存储器系统则在成本及功耗方面占有优势,而8位的存储器系统现在已经很少使用。下面主要介绍16位和32位的Flash存储器系统的构建。

1.3.1.16位的FLASH存储器系统

在大多数的系统中,选用一片16位的Flash存储器芯片(常见单片容量有1 MB 、2MB 、4MB 、8MB 等)构建16位Flash的存储系统已经足够,在此采用一片HY29LV160构建16位的Flash存储器系统,其存储容量为2MB。Flash存储器在系统中通常用于存放程序代码,系统上电或复位后从此处获取指令并开始执行,因此,应将存有程序代码的Flash存储器配置到ROM/SRAM/FLASH Bank0,即将S3C4510B的nRCS<0>(Pin75)接至HY29LV160的CE#端。[page]

HY29LV160的RESET#端接系统复位信号;

OE#端接S3C4510B的nOE(Pin72);

WE#端S3C4510B的nWBE<0>(Pin100);

BYTE#上拉,使HY29LV160工作在字模式(16位数据宽度);

RY/BY#指示HY29LV160编程或擦除操作的工作状态,但其工作状态也可通过查询片内的相关寄存器来判断,因此可将该引脚悬空;

地址总线[A19~A0]与S3C4510B的地址总线[ADDR19~ADDR0]相连;

16位数据总线[DQ15~DQ0]与S3C4510B的低16位数据总线[XDATA15~XDATA0]相连。

注意此时应将S3C4510B的B0SIZE[1:0]置为“10”,选择ROM/SRAM/FLASH Bank0为16位工作方式。

1.3.2. 32位的FLASH存储器系统

作为一款32位的微处理器,为充分发挥S3C4510B的32性能优势,有的系统也采用两片16位数据宽度的Flash存储器芯片并联(或一片32位数据宽度的Flash存储器芯片)构建32位的Flash存储系统。其构建方式与16位的Flash存储器系统相似。

采用两片HY29LV16并联的方式构建32位的FLASH存储器系统,其中一片为高16位,另一片为低16位,将两片HY29LV16作为一个整体配置到ROM/SRAM/FLASH Bank0,即将S3C4510B的nRCS<0>(Pin75)接至两片HY29LV16的CE#端;

两片HY29LV160的RESET#端接系统复位信号;

两片HY29LV160的OE#端接S3C4510B的nOE(Pin72);

低16位片的WE#端接S3C4510B的nWBE<0>(Pin100),高16位片的WE#端接S3C4510B的nWBE<2>(Pin102);

两片HY29LV160的BYTE#均上拉,使之均工作在字模式;

两片HY29LV160的地址总线[A19~A0]均与S3C4510B的地址总线[ADDR19~ADDR0]相连;

低16位片的数据总线与S3C4510B的低16位数据总线[XDATA15~XDATA0]相连,高16位片的数据总线与S3C4510B的高16位数据总线[XDATA31~XDATA16]相连。

注意此时应将S3C4510B的B0SIZE[1:0]置为“11”,选择ROM/SRAM/FLASH Bank0为32位工作方式。

2.S3C4510B系统管理器关于存储器映射的工作原理

当系统设计制作完成时,必须经过仔细的调试,才能保证系统按照设计意图正常工作。尽管系统的调试与个人对电路工作原理的理解和实际的电路调试经验有很大的关系,但一定的调试方法也是必不可少的。掌握正确的调试方法可使调试工作变得容易,大大缩短系统的开发时间,反之,可能会使整个系统的开发前功尽弃,以失败告终。

在系统的两类存储器中,SDRAM相对于FLASH存储器控制信号较多,似乎调试应该困难一些,但由于SDRAM的所有刷新及控制信号均由S3C4510B片内的专门部件控制,无需用户干预,在S3C4510B正常工作的前提下,只要连线无误,SDRAM就应能正常工作,反之,Flash存储器的编程、擦除操作均需要用户编程控制,且程序还应在SDRAM中运行,因此,应先调试好SDRAM存储器系统,再进行Flash存储器系统的调试。

基于S3C4510B系统的最大可寻址空间为64MB,采用统一编址的方式,将系统的SDRAM、SRAM、ROM、Flash、外部I/O以及片内的特殊功能寄存器和8K一体化SRAM均映射到该地址空间。为便于使用与管理,S3C4510B又将64MB的地址空间分为若干个组,分别由相应的特殊功能寄存器进行控制:

(1) ROM/SRAM/Flash组0~ROM/SRAM/Flash组5,用于配置ROM、SRAM或Flash,分别由特殊功能寄存器ROMCON0~ROMCON5控制;

(2)DRAM/SDRAM组0~DRAM/SDRAM组3用于配置DRAM或SDRAM,分别由特殊功能寄存器DRAMCON0~DRAMCON3控制;

(3)外部I/O组0~外部I/O组3用于配置系统的其他外扩接口器件,由特殊功能寄存器REFEXTCON控制;

(4)特殊功能寄存器组用于配置S3C4510B片内特殊功能寄存器的基地址以及片内的8K一体化SRAM,由特殊功能寄存器SYSCFG控制;

在系统中,使用了Flash存储器和SDRAM,分别配置在ROM/SRAM/FLASH组0和DRAM/SDRAM组0,暂未使用外扩接口器件。

3基于S3C4510B的嵌入式系统Flash存储器接口电路的调试

Flash存储器的调试主要包括Flash存储器的编程(烧写)和擦除,与一般的存储器件不同,用户只需对Flash存储器发出相应的命令序列,Flash 存储器通过内部嵌入的算法即可完成对芯片的操作,由于不同厂商的Flash存储器在操作命令上可能会有一些细微的差别,Flash存储器的编程与擦除工具一般不具有通用性,这也是为什么Flash接口电路相对较难调试的原因之一,因此,应在理解Flash存储器编程和擦除的工作原理的情况下,根据不同型号器件对应的命令集,编写相应的程序对其进行操作。

若使用SDT调试环境,调试过程与上述步骤相似。

>obey C:\\memmap.txt

打开AXD Debugger的命令行窗口,执行obey命令:

此时,2MB的Flash存储器映射到地址空间的0x0000,0000~0x001F,FFFF处,选择菜单Processor Views→Memory选项,出现存储器窗口,在存储器起始地址栏输入Flash存储器的映射起始地址:0x0,数据区应显示Flash存储器中的内容,若Flash存储器为空,所显示的内容应全为0xFF,否则应为已有的编程数据。双击其中的任一数据,输入新的值,对应存储单元的内容应不能被修改,此时可初步认定Flash存储器已能被访问,但是否能对其进行正确的编程与擦除操作,还需要编程验证,通过程序对Flash存储器进行编程和擦除操作。

4结束语

这样整个基于的嵌入式系统Flash存储器接口电路的调试基本上完成了,当然对于不同的系统,操作是略有不同的,我们可以根据所要开发或使用的嵌入式系统模式,进行适当的调整,保证我们正确的使用Flash存储器。

上一篇:μC/OS-II在S3C44BOX上的移植

下一篇:基于嵌入式系统开发之中断控制的实现

推荐阅读最新更新时间:2024-03-16 13:20

设计资源 培训 开发板 精华推荐

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

深入理解计算机系统

深入理解计算机系统 【得捷Follow me第4期】+小白手把手带你学习rp2040+w5500(所有任务)

【得捷Follow me第4期】+小白手把手带你学习rp2040+w5500(所有任务) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号