1.引言

传统的数据采集系统,通常采用MCU或DSP作为控制模块,来控制A/D,存储器和其他一些外围电路。这种方法编程简单,控制灵活,但缺点是控制周期长,速度慢。特别是当A/D本身的采样速度比较快时,MCU的慢速极大地限制了A/D高速性能的使用。MCU的时钟频率较低并且用软件实现数据的采集,软件运行时间在整个采样时间中占的比例很大,使得采样速率较低。

随着数据采集对速度性能的要求越来越来高,传统的采集系统的弊端越来越明显。本设计采用FPGA,各模块设计使用VHDL语言,其各进程间是并行的关系。它有MCU无法比拟的优点。FPGA的时钟频率高,全部控制逻辑由硬件完成,实现了硬件采样,速度快。

2.系统的总体设计

本数据采集系统,采用FPGA+MCU的结构,主控逻辑模块用FPGA来实现,在系统中对A/D器件进行采样控制,起到连接采样电路和MCU的桥梁作用,数据处理、远程通信及液晶显示控制等由MCU来完成。FPGA把传统的纯粹以单片机软件操作形式的数据采集变成硬件采集。

首先用VHDL语言来设计状态机,用MCU来启动状态机,使其控制A/D器件,实现数据采集。并将采集到的数据存储到FPGA内部的数据缓存区FIFO中。当FIFO存储已满时,状态机控制FIFO停止数据写入,并通知单片机取走采集数据进行下一步处理。这种设计思想大大减轻了单片机的软件运行时间,提高了采集速率。这里,把6路模拟信号采集任务作为快任务,把用于系统自检的6路检测量信号作为慢任务。为了使快任务的优先级高于慢任务,本系统设计两个状态机分别实现快任务和慢任务的数据采集,并由单片机生成PWM波,分别控制两个状态机。系统的总体框图如图1所示:

3.系统主要器件的选择

3.1 FPGA芯片选型及依据

FPGA实现主控逻辑控制,要求响应速度快,效率高。可采用ALTERA公司的ACEX1K系列EP1K5O芯片,最高工作频率可达250MHz.

该系列芯片的特点是将LUT(查找表)和EAB(嵌入式阵列)相结合,提供了效率最高而又廉价的结构。基于LUT的逻辑对数据路径管理、寄存器强度、数学计算或数字信号处理的设计提供优化的性能和效率,而EBA可实现RAM(随机读写存储器)、ROM(只读存储器)、双口RAM或FIFO(先人先出存储器)功能,使得ACEX1K适合复杂逻辑以及有存储、缓冲功能的数据采集系统。

3.2 ADC芯片选型及依据

数据采集系统的输入信号多数都来源于现场传感器的输出信号,传感器种类不一,致使信号特性也不同,各通道信号的幅度与频率范围有很大的不同,高精度的、大动态范围的A/D转换芯片使设计更能满足测量的需要。本设计中A/D转换模块选用的AD574A是美国模拟数字公司(Analog)推出的单片高速12位逐次比较型A/D转换器,转换速率:25us,内置双极性电路构成的混合集成转换显片,具有外接元件少,功耗低,精度高等特点,并且具有自动校零和自动极性转换功能,只需外接少量的阻容件即可构成一个完整的A/D转换器。

4.FPGA方案设计

4.1 设计思想

用VHDL语言来设计两个状态机,状态机1来控制A/D实现快任务的采集,状态机2来完成慢任务采集。两个状态机的时钟信号CLK(高电平有效)均来自单片机生成的PWM波,状态机1直接由单片机控制,状态机2则是由单片机经反向器来控制。首先置P1.0口为高电平,并用定时器来产生中断,使P1.0口产生PWM波。当P1.0口为高电平时启动状态机1,此时状态机2不动作;当快任务采样完成后,由定时器产生中断,将P1.0口置为低电平,此时状态机2动作,来完成慢任务采集。下一个周期完成同样的操作。对应快任务的采集数据缓存在快任务FIFO,慢任务的采集数据缓存在慢任务FIFO里,单片机读对应的FIFO数据来进行相应处理。

4.2 各模块的设计

根据以上的设计思想,FPGA系统的硬件设计模块主要有状态机模块,FIFO设计模块[4-5].

下面具体给出硬件原理设计。

4.2.1 状态机的设计

该设计过程主要是建立采集所需要的硬件电路,等待时钟信号的到来便立刻启动A/D进行工作。了解了AD574A的工作时序,就可以写出状态机的采样控制状态。控制状态编码表如表1所示。[page]

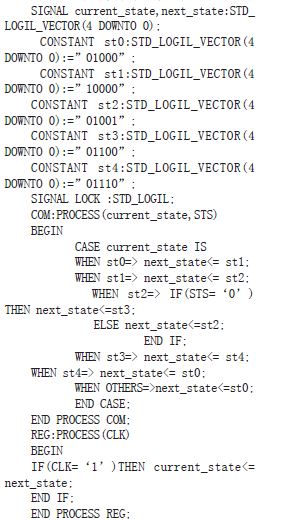

用VHDL语言来实现状态机,其原程序:

然后在Quartus Ⅱ 中进行仿真,仿真如图2所示:

4.2.2 FIFO模块设计

利用FPGA中的EAB/ESB等嵌入式模块构成的LPM宏功能模块来生成LPM_FIFO.其编辑定制方法:

(1)进入QuartusⅡ,选择菜单File->TOOL->Megawizard Plug-In Manager,选择Create a new custom megafunctionvariation,选择FIFO.

(2)选择FIFO数据位宽度为12,深度为512.

(3)选择FIFO的端口:12位数据输入输出端口data[120]和q[120];对clock同步的数据写入和读出请求wrreq和rdreq;异步清零aclr;存储数据溢出信号full.

5.结论

本文完成高速、多通道的数据采集系统的FPGA设计。利用VHDL语言对FPGA进行设计,并在QuartusⅡ中进行系统仿真和验证。

由FPGA在线编程的特点,可以依据现场的具体情况,对FPGA的内部配置进行修改,进一步增加了系统应用的灵活性,因此该系统是一种比较理想的实时高速数据采集方案

上一篇:数控电源电路故障检修讨论

下一篇:基于单片机的数控开关电源设计方案

推荐阅读最新更新时间:2024-03-16 13:28

嵌入式C语言自我修养——从芯片、编译器到操作系统 带目录 文字版

嵌入式C语言自我修养——从芯片、编译器到操作系统 带目录 文字版 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号