LPC1768有三个独立的时钟源,可以通过软件进行配置。MCU上电并成功复位后,内部的RC振荡器开始起振,并以此为工作频率去读取内部ROM区的代码来执行初始化工作,其中就包括对系统时钟的配置(在文件system_LPC17xx.c中)。

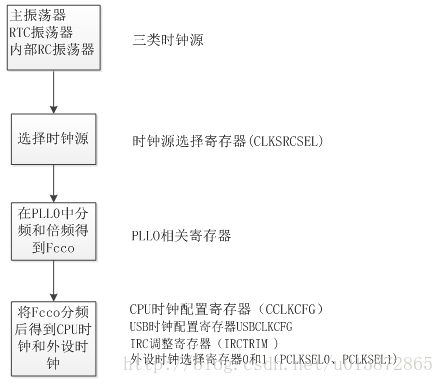

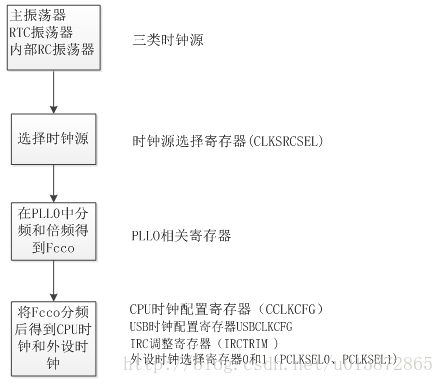

系统时钟配置的过程如下:

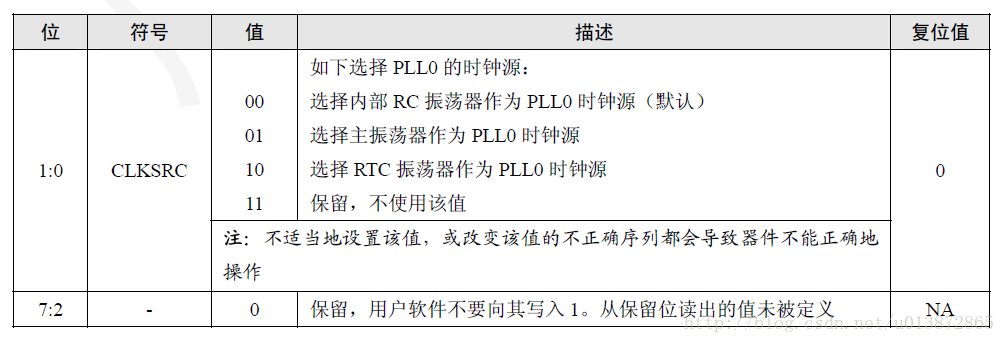

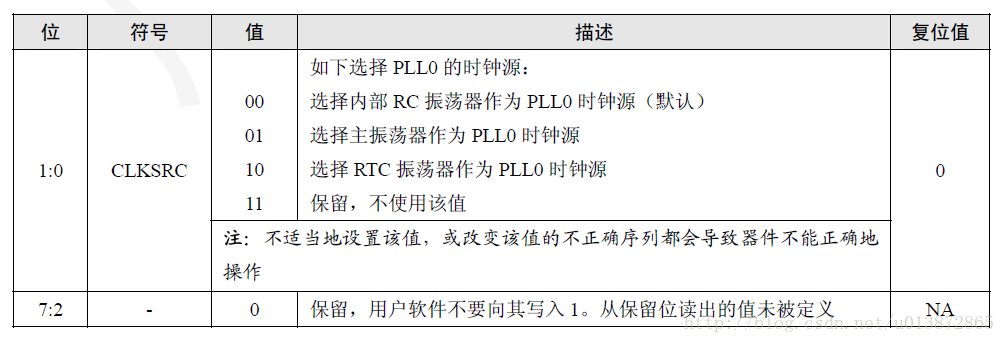

LPC1700系列Cortex-M3微控制器包括3个独立的振荡器,它们分别为主振荡器(通常指外界晶振)、内部RC振荡器和RTC振荡器。每个振荡器可根据特定的应用要求来选用(通过配置时钟源选择寄存器CLKSRCSEL),寄存器配置如下

表1 时钟源选择寄存器位描述

注意:注意下列有关时钟源选择的限制:

1. IRC的精度达不到USB接口的时间基准精度要求,因此IRC振荡器不应用作(通过PLL0)USB子系统的时钟源(USB要求一个占空比为50%的48MHz时钟源);

2. 如果CAN波特率高于100kbit/s,则IRC振荡器不应用作(通过PLL0)CAN控制器的时钟源

值得一提的是,LPC1768有一个专门针对主振荡器的寄存器叫作系统控制和状态寄存器(SCS),在选择主振荡器作为时钟源前,需要配置该寄存器。在该寄存器中可以配置主振荡器的频率范围、主振荡器使能,或读取主振荡器的状态(是否稳定)。位描述如下:

表2 系统控制和状态寄存器(SCS)位描述

时钟源确定后,PLL将输入时钟源升频,然后再分频以提供给CPU、外设或USB子系统使用的实际时钟。需要注意的是USB子系统有其自身特定的PLL(见“PLL1”的描述)。PLL0可产生的时钟频率高达100MHz,是CPU所允许的最大值。

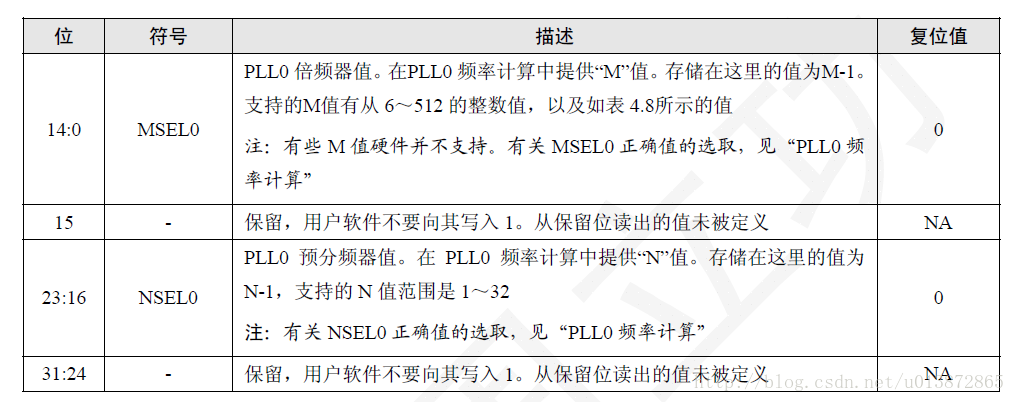

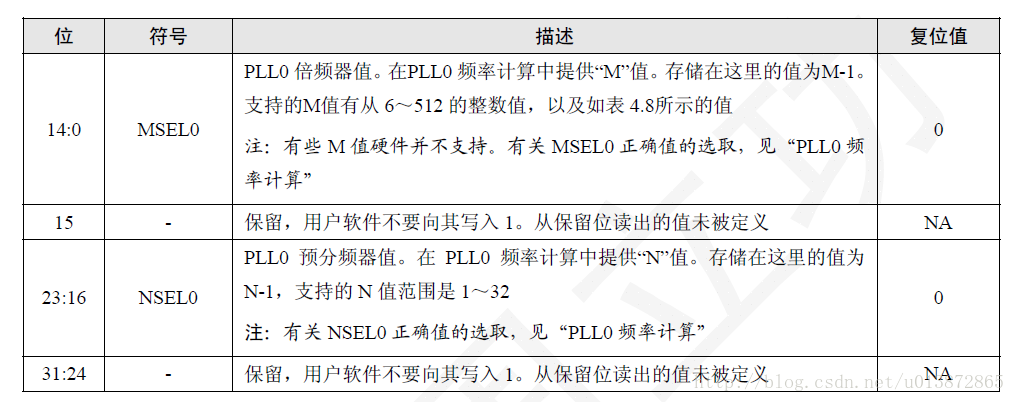

倍频和分频值通过写PLL0配置寄存器(PLL0CFG)中的MSEL0和NSEL0来改变,寄存器的位描述如表2.

表3 PLL0配置寄存器位描述

注意:在配置PLL0时必须将正确的馈送序列写入PLL0FEED寄存器才能使PLL0CON和PLL0CFG寄存器的更改生效。请参见手册PPL0馈送寄存器。

PLL0输出频率(当PLL0被激活且连接时)的公式:

Fcco=(2×M×FIN)/ N。

Fcco表示的是经过PLL0处理后输出的频率值,如果要为CPU和外设提供工作频率,还需要分别经过时钟分频器的分频,例如CPU时钟配置寄存器(CCLKCFG)、USB时钟配置寄存器(USBCLKCFG)等。

如果要用户根据需要自己配置M和N的值,请参见手册“计时和功率控制”一章中的确定4.5.11小节“PLL0频率参数的过程”。

在建立LPC1768的工程时,我们需要添加“system_17XX.c”文件,该文件主要的作用就是对系统时钟的配置,配置过程基本和本文一致。

关键字:LPC1768 时钟

引用地址:

LPC1768时钟详解

推荐阅读最新更新时间:2024-03-16 16:07

数码管时钟电路的设计

LED数码管时钟电路采用24h计时方式,时、分、秒用六位数码管显示。该电路采用AT89C2051单片机,使用3V电池供电,只使用一个按键开关即可进入调、省电(不显示LED数码管)和正常显示三种状态。 1. 时钟电路硬件设计 数码管时钟电路如下所示,其采用AT89C2051单片机最小化应用设计,LED显示采用动态扫描方式实现,P1口输出端码数据,P3.0~P3.5口作扫描输出,P3.7接按钮开关。为了提供LED数码管的驱动电流,用三极管9012作电源驱动输出。为了提高秒计时的精确性,采用12MHz晶振。 2. 系统主要程序的设计 ( 1 )主程序 本设计中的计时采用定时器 T0中断完成,其余状态循环调用显

[单片机]

基于XC2V1000型FPGA的FIR抽取滤波器的设计

1 引言 抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA)有着规整的内部逻辑阵列和丰富的连线资源,特别适用于数字信号处理,但长期以来,用FPGA实现抽取滤波器比较复杂,其原因主要是FPGA中缺乏实现乘法运算的有效结构。现在,FPGA集成了乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍用Xilinx公司的XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

[应用]

stm32 hal i2c 库读写sd3088时钟

前一版本的修正。 sd3008在每次通信开始0.5s做一次总线复位,不必考虑stm32的i2c Bug问题。 而且HAL库,是不是也应考虑到软件上补充这个Bug? 使用HAL_I2C_Mem_Read/Write,使得代码非常好看。模拟I2C方式,一字长蛇阵模样。 使用Freertos,读取时间、保存数据到用户SRAM,需要考虑Mutex对RTC时钟资源进行保护。 * SD3088时钟芯片 读写 * 文件 sd3088.h * http://git.oschina.net/maizhi/small-pellet-sove-control-system *作者 于 *版本 v1.1 */ #incl

[单片机]

编写bootloader(一):编写前的介绍及关闭看门狗和时钟的设置

我们知道,U-Boot最大的作用就是启动内核。然而,启动内核之前,它也要做许多事情。接下来,我们就自己编写一个bootloader,让它执行启动内核的功能。 对于bootloader,我们知道,它的第一段代码就是Start.S,这是一个汇编文件,在这个文件里面,我们进行一些硬件的初始化,也就是bootloader初始化的第一阶段。在这个初始化里面,我们需要做以下事情: 1.关看门狗 2.设置时钟 3.初始化SDRAM 4.重定位代码 对于上面的步骤,我分别解释一下。首先,关看门狗,是防止程序定时重启;设置时钟,可以设置机器的运行频率,如CPU运行频率,与HCLK有关的部件的频率、与

[单片机]

STM32时钟体系结构

STM32的时钟体系可以直接以图概括(摘自STM32F10X参考手册) 下面就此图做分析 1. STM32输入时钟源 1.1 时钟源的作用 无论是小型单片机还是像STM32这样高级单片机,它们工作的核心都是大规模的时序逻辑电路,而驱动时序逻辑电路的关键则是准确而又稳定的时钟源。它的作用就像小学在操场上做广播体操时候播放的背景音乐,用于协调和同步各单元运行,为时序电路提供基本的脉冲信号。 1.2 STM32时钟源的设计 在51单片机中,一般都外接一个11.0592MHz的晶振,注意,提供时钟的不是晶振,而是RC时钟电路,而晶振只是时钟电路的元件之一。同理,在STM32中,时钟源也是由RC时钟电路产生,与51单片机的区别是区别在于

[单片机]

STM32的各种时钟系统的应用解析

时钟系统是处理器的核心,所以在学习STM32所有外设之前,认真学习时钟系统是必要的,有助于深入理解STM32。 重要的时钟: PLLCLK,SYSCLK,HCKL,PCLK1,PCLK2 之间的关系要弄清楚; 1、HSI:高速内部时钟信号 STM32单片机内带的时钟 (8M频率) 精度较差 2、HSE:高速外部时钟信号 精度高 来源(1)HSE外部晶体/陶瓷谐振器(晶振) (2)HSE用户外部时钟 3、LSE:低速外部晶体 32.768kHz 主要提供一个精确的时钟源 一般作为RTC时钟使用 在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。 ①、HSI是高速内部时钟,RC振荡器,频率为8MHz。 ②

[单片机]

LCD1602&DS1302时钟测试程序+仿真图分享

comments : 1、八线制驱动LCD1602B:PB0-PB7为数据线,PD3/PD4/PD6控制LCD1602B的RS,RW,EN。 2、设置和读取DS1302内部时钟,并通过LCD1602显示。 3、进行此实验请插上JP1、JP2的所有8个短路块,PC2、PC3、PC4、PC7短路块。 4、DS1302芯片接口占用JTAG仿真接口,在做实验时需要关闭mega16的JTAG功能,否则 不正常显示。 仿真原理图如下(proteus仿真工程文件可到本帖附件中下载) 单片机源程序如下: #include iom16v.h #include macros.h #include ds1302.h #include L

[单片机]

STM32 SPI时钟问题

STM32中有SPI1/2/3,关于SPI的时钟问题,要具体看是SPI1还是SPI2/3。SPI1时钟由APB2时钟分频而来,而SPI2/3时钟由APB2时钟分频而来。 APB1的最高频率是36MHz,APB2的最高频率是72MHz,而PCLK1和PCLK2一般也默认配置为其最高工作频率36M和72M,详参时钟树。 SPI1时钟由APB2时钟分频而来,可以选择2、4、8、16、32、64、128、256这几个分频系数。而手册规定STM32的SPI时钟最快是18MHz。对于STM32F103的SPI1接口时钟,由72M的PCLK2分频得到,所以分配系数大于等于4(72M/4 = 18M)。对于STM32F103的SPI2/3

[单片机]

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号