1,板上的存储资源

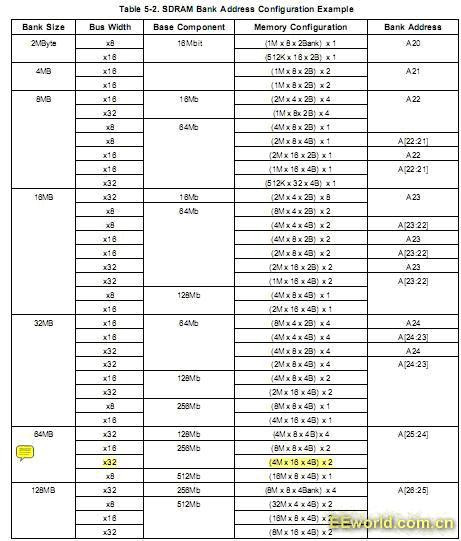

两个32M的SDRAM.

一个2M的NOR FLASH

一个128M(有些是64M)的NAND FLASH

以上这些资源看原理图便知.

2,板上的I/O资源

这块板子上(准确的说是S3C2440)的I/O空间是用存储映射的方法映射到存储空间上的,也就说I/O空间是要占用存储空间的.

3,各种存储器的区别与各自的用途

为什么这块板子上有那么多存储设备呢?原因很简单.每种存储设备的用途都不一样,而且为了兼顾广大用户的需要,也必须有不同的存储设备.首先说SDRAM.(写到这突然想起忘了说SRAM了.SRAM是静态随机存储器,它具有掉电不丢失数据且不必频繁刷新的特点,存储速度快,相当于PC的内存,看来这块相当于内存的东西很重要,可是刚刚怎么没说有这块东西呢?原因很简单.因为本来就没有.其实,如果需要随机存储器,SDRAM就是随机存储器啊,只是它需要不断的刷新以保持里面的数据(电平).说到这,SDRAM的作用同学们也应该了解了.也就说我们这块板子就是有64M的内存,足够用了.

其次说说NOR FLASH.NOR FLASH是具有SRAM接口特性的ROM.可是NOR FLASH才2M未免太少了,没错,是很少,可是我们有NAND FLASH啊,它也是ROM啊,所以加起来我们可以说这块板子有130M(66M)的硬盘.这也足够用了,可以少好几个Linux了.

再说说NAND FLASH,NAND FLASH可以做的很大,但是速度却比不上NOR FLASH,NOR FLASH能做快却不能做的大,所以,速度和容量是一对矛盾.为了克服这对矛盾,这板子上两种FLASH都有了.各有用途.另外,初学者一定要知道NAND FLASH 与NOR FLASH启动的不同吧.这是跟他们的特性有关的,接下来谈谈.

4,NOR FLASH 启动与NAND FLASH 启动

开发板上有一个S2开关,当它打在NOR一端是就是NOR启动.相反,打在另一端就是NAND FLASH启动了.先说着两种启动的不同,再说说硬件上是如何启动的,空间有时如何分配的.当S2打在NAND FLASH启动,那么程序就是在NAND FLASH上跑起来.其实,在内部还有一个4K字节的steppingstone的缓冲器(其实这是一个SRAM),当选择NAND FALSH 启动时,这个缓冲器映射在地址0x0000_0000上,而它负责将NAND FLASH上的代码复制到SDRAM上(大家都知道,程序运行时都是在RAM上运行的,怎么可能是在FLASH上运行呢,其实就是将FLASH上的代码复制了而已)而负责复制这段代码的东西就是传说中的BIOS啦.

当S2打在NOR FLASH一端时,又有什么区别呢?当选择用NOR FLASH启动时,2M的NOR FLASH就映射到地址0x0000_0000上,程序就是从这里运行了.那难道程序就能从NOR FLASH上运行吗?当然不行,那为什么可以在这里启动呢,其实这个NOR FLASH已经安装了BIOS的了(若有读者不知什么是BIOS,那就暂且认为它的功能就是从FLASH上复制代码到SDRAM就可以了)

4,S3C2410 S3C2440NAND 存储系统

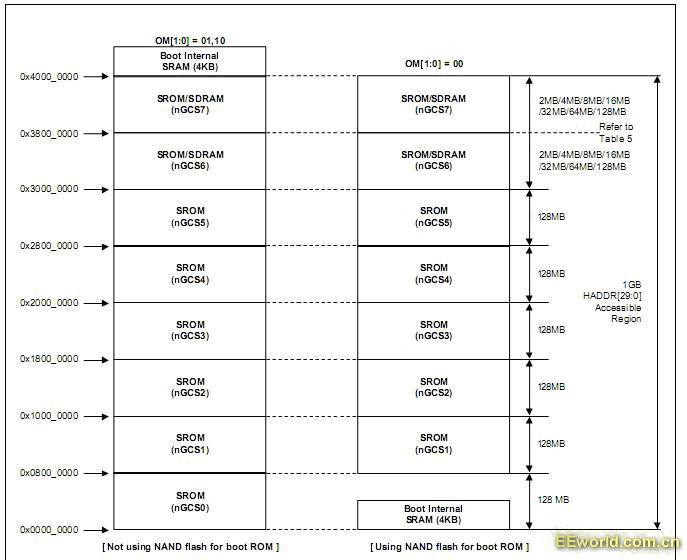

大家都知道,32位可以寻址4G空间.但是S3C2440却的存储空间里把4G这样子分的:

(途中只显示最低的1G)

0x4000_0000只有还有3G空间是这样分配:

OM[1:0]=01或者是10 时:0x4000_0000-0x4000_0fff.这4字节的就是前面说的stepingstone的啦.0x4000_0fff_0x4800_0000是没用到的.0x4800_0000-0x6000_0000的空间是特殊功能寄存器的.你发现,所有的寄存器都是在这个范围内的.0x6000_0000—0Xffff_ffff的还是未用到的.

OM[1:0]=00时.这个时候如上图所示.刚刚说的steppingstone映射到ox000_0000那里,也即是途中的BOOT INTERNAL SRAM.其他的一样.

其实.S3C2440把低1G的空间分成了8块,由图可知,第0至6这七块的起始地址是不变的.而第七段的地址是可变的(它的地址有第六块需要用到多少来决定,反正就是第六第七是连在一起的).前6块可以是ROM SRAM .最后两块不但可以是ROM,SRAM外,还可以是SDRAM.其实啊,简单点的说,就是只有最后两块才能是SDRAM.也就是说SDRAM必须要映射到这两块里面.mini2440就是选择映射在第七块上,所以SDRAM的起始地址是0x3000_0000(这就是手册上为什么在加载测试程序时DNW的初始值要设为这个,它就是为了想程序直接加载到SDRAM上,这只是做实验而且,掉电后还是会丢失的.所以做产品时是不可能这样做的).

刚刚说S3C2440把存储空间分为8块,它为什么要这么做呢?其实很简单,即使它不这么做,我们也会这么做的.先了算一算数:每块128M,那就是需要27根地址线来寻址.而8块呢就跟着引出与之一一对应的8跟片选引脚.讲到这聪明的读者必能想到.其实这8根片选引脚就是里面用3根地址线译码出来的.所以一共用了30根地址线,30根不正好是1G么.呵呵.

说的差不多了.应该有很多需要完善的,但是这对于初学者来说还是有一定的帮助吧?

S3C2440 MEMORY CONTROLLER详解

BANK0总线宽度由OM[1:0]引脚决定,当OM[1:0]=01时,booting ROM data width是16位,当[1:0]=10时,booting ROM data width是32位,当OM[1:0]=00时,从NAND FLASH启动。在友善之臂S3C2440开发板上,OM1引脚直接接地。

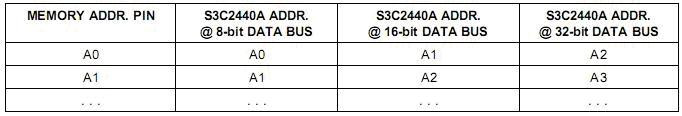

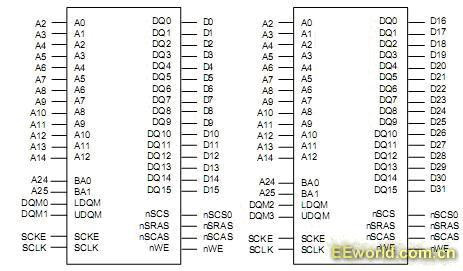

具体的S3C2440与两片SDRAM接线方式如下图所示:

SDRAM的工作时序作为ARM工程师了解即可,具体的读写控制由寄存器控制器完成,作为FPGA工程师则需要详细了解SDRAM工作原理与时序,在此不再赘述。作为ARM工程师,最重要的是准确配置与SDRAM相关的寄存器。

软件可编程的大小端模式;

地址空间:每个BANK可寻址128MB(总共8个BANK 1GB空间);

可编程的访问位宽:BANK0为16或32位,其他BANK为8或16或32位;

8个存储器BANK,其中6个用于ROM或者SRAM,2个用于ROM、SRAM或者SDRAM;

BANK0~BANK6的起始地址固定;

BANK7的起始地址和大小可编程;

所有存储器BANK的访问周期可编程;

外部wait信号可延长总线周期;

支持SDRAM的自刷新和掉电模式。

上一篇:基于LPC1114的学习型红外遥控器

下一篇:ARM3级流水和5级流水为什么都是PC=PC+8

推荐阅读最新更新时间:2024-03-16 15:04

代码揭秘:从C/C++的角度探秘计算机系统

代码揭秘:从C/C++的角度探秘计算机系统 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号