AT89S51单片机共有4个双向的8位并行I/O口,分别记为PO、Pl、P2和P3,其中输出锁存器属于特殊功能寄存器。端口的每一位均由输出锁存器、输出驱动器和输入缓冲器组成,这4个端口除了按字节输入/输出外,还可以按位寻址,便于位控功能的实现。

PO口

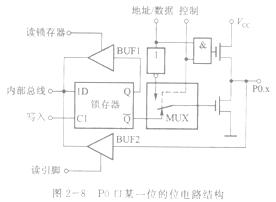

PO口是一个双功能的8位并行口,字节地址为80H,位地址为80H~87H。端口的各位具有完全相同但又相互独立的电路结构,PO口某一位的位电路结构如图2-8所示。

1.位电路结构

PO口某一位的电路包括:

(1)一个数据输出的锁存器,用于数据位的锁存。

(2)两个三态的数据输入缓冲器,分别是用于读锁存器数据的输入缓冲器BUF1和读引脚数据的输入缓冲器BUF2。

(3)一个多路转接开关MUX,它的一个输入来自锁存器的Q(的反)端,另一个输入为地址/数据信号的反相输出。MUX由“控制”信号控制,实现锁存器的输出和地址/数据信号之间的转接。

(4)数据输出的控制和驱动电路,由两个场效应管(FET)组成。

2.工作过程分析

(1) PO口用作地址/数据总线 当AT89S51外扩存储器或I/O时,PO口作为单片机系统复用的地址/数据总线使用。

当作为地址或数据输出时,“控制”信号为1,硬件自动使转接开关MUX打向上面,接通反相器的输出,同时使与门处于开启状态。当输出的地址/数据信息为l时,与门输出为1,上方的场效应管导通,下方的场效应管截止,PO.x引脚输出为l;当输出的地址/数据信息为O时,上方的场效应管截止,下方的场效应管导通,PO.x引脚输出为0。这说明PO.x引脚的输出状态随地址/数据状态的变化而变化。输出电路是上、下两个场效应管形成的推拉式结构,大大提高了负载能力,上方的场效应管这时起到内部上拉电阻的作用。

当PO口作为地址/数据输入时,仅从外部存储器(或外部I/O)读入信息,对应的“控制”信号为0,MUX接通锁存器的Q(的反)端。由于PO口作为地址/数据复用方式访问外部存储器时,CPU自动向PO口写入FFH,使下方的场效应管截止,上方的场效应管由于控制信号为O也截止,从而保证数据信息的高阻抗输入,从外部存储器输入的数据信息直接由PO.x引脚通过输入缓冲器BUF2进入内部总线。

具有高阻抗输入的I/O口如果是真正的双向口,它应是具有高电平、低电平和高阻抗3种状态的端口。因此,PO口作为地址/数据总线使用时是一个真正的双向端口,简称双向口。

(2) PO口用作通用I/O口 当PO口不作为系统的地址/数据总线使用时,此时PO口也可作为通用的I/O口使用。

当用作通用的I/O时,对应的“控制”信号为0,MUX打向下面,接通锁存器的Q(的反)端,与门输出为0,上方的场效应管截止,形成的PO口输出电路为漏极开路输出。

PO口用作输出口时,来自CPU的“写”脉冲加在D锁存器的CP端,内部总线上的数据写入D锁存器,并由引脚PO.x输出。当D锁存器为1时,Q端为0,下方场效应管截止,输出为漏极开路,此时,必须外接上拉电阻才能有高电平输出;当D锁存器为0时,下方场效应管导通,PO口输出为低电平。

PO口作为输入口使用时,有两种读入方式:“读锁存器”和“读引脚”。当CPU发出“读锁存器”指令时,锁存器的状态由Q端经上方的三态缓冲器BUF1进入内部总线;当CPU发出“读引脚”指令时,锁存器的输出状态=1(即Q(的反)端为0),从而使下方场效应管截止,引脚的状态经下方的三态缓冲器BUF2进入内部总线。

3.PO口的特点

综上所述,PO口具有如下特点:PO口为双功能口——地址/数据复用口和通用I/O口。

(1)当PO口用作地址/数据复用口时,是一个真正的双向口,用作与外部存储器的连接,输出低8位地址和输出/输入8位数据。

(2)当PO口用作通用I/O口时,由于需要在片外接上拉电阻,端口不存在高阻抗(悬浮)状态,因此是一个准双向口。为保证引脚信号的正确读入,应首先向锁存器写l。单片机复位后,锁存器自动被置1;当PO口由原来的输出状态转变为输入状态时,应首先置锁存器为1,方可执行输入操作。

一般情况下,PO口大多作为地址/数据复用口使用,这时就不能再作为通用I/O口使用。

Pl口

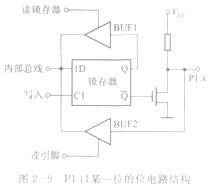

Pl口是单功能的I/O口,字节地址为90H,位地址为90H~97H。Pl口某一位的位电路结构如图2-9所示。

1.位电路结构

P1口位电路结构由以下三部分组成:

(1)一个数据输出锁存器,用于输出数据位的锁存。

(2)两个三态的数据输入缓冲器BUF1和BUF2,分别用于读锁存器数据和读引脚数据的输入缓冲。

(3)数据输出驱动电路,由一个场效应管(FET)和一个片内上拉电阻组成。

2.工作过程分析

P1口只能作为通用的I/O口使用。

(1) P1口作为输出口时,若CPU输出1,Q=1, Q(的反)=0,场效应管截止,Pl口引脚的输出为1;若CPU输出Q=0,Q(的反)=1,场效应管导通,P1口引脚的输出为0。

(2) P1口作为输入口时,分为“读锁存器”和“读引脚”两种方式。“读锁存器”时,锁存器的输出端Q的状态经输入缓冲器BUF1进入内部总线;“读引脚”时,先向锁存器写1,使场效应管截止,Pl.x引脚上的电平经输入缓冲器BUF2进入内部总线。

3.P1口的特点

P1口由于有内部上拉电阻,没有高阻抗输入状态,故为准双向口。作为输出口时,不需要在片外接上拉电阻。

P1口“读引脚”输入时,必须先向锁存器写入1。

P2口

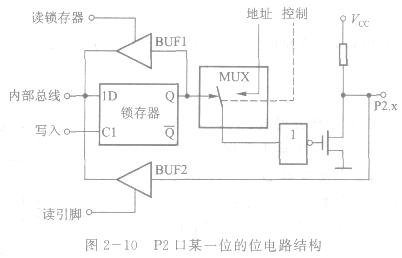

P2口是一个双功能口,字节地址为AOH,位地址为AOH~A7H。P2口某一位的位电路结构如图2-10所示 。

。

1.位电路结构

P2口某一位的电路包括:

(1)一个数据输出锁存器,用于输出数据位的锁存。

(2)两个三态数据输入缓冲器BUF1和BUF2,分别用于读锁存器数据和读引脚数据的输入缓冲。

(3)一个多路转接开关MUX,它的一个输入是锁存器的Q端,另一个输入是地址的高8位。

(4)输出驱动电路,由场效应管(FET)和内部上拉电阻组成。

2.工作过程分析

(1) P2口用作地址总线 在内部控制信号作用下,MUX与“地址”接通。当“地址”线为O时,场效应管导通,P2口引脚输出0;当“地址”线为1时,场效应管截止,P2口引脚输出1。(2) P2口用作通用I/O口 在内部控制信号作用下,MUX与锁存器的Q端接通。

CPU输出1时,Q=1,场效应管截止,P2.x引脚输出1;CPU输出0时,Q=0,场效应管导通,P2.x引脚输出0。

输入时,分为“读锁存器”和“读引脚”两种方式。“读锁存器”时,Q端信号经输入缓冲器BUF1进入内部总线;“读引脚”时,先向锁存器写1,使场效应管截止,P2.x引脚上的电平经输入缓冲器BUF2进入内部总线。

3.P2口的特点

作为地址输出线使用时,P2口可以输出外部存储器的高8位地址,与PO口输出的低8位地址一起构成16位地址,可以寻址64 KB的地址空间。当P2口作为高8位地址输出口时,输出锁存器的内容保持不变。

作为通用I/O口使用时,P2口为一个准双向口。功能与Pl口一样。

一般情况下,P2口大多作为高8位地址总线口使用,这时就不能再作为通用I/O口使用。

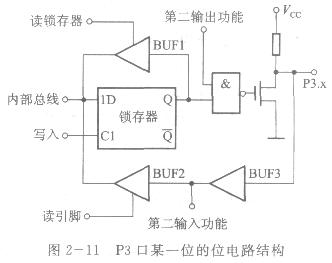

P3口

由于AT89S51的引脚数目有限,因此在P3口电路中增加了引脚的第二功能。P3口的每一位都可以分别定义为第二输入功能或第二输出功能。P3口的字节地址为BOH,位地址为BOH~B7H。P3口某一位的位电路结构如图2-11所示 。

。

1.位电路结构

P3口某一位的电路包括:

(1)一个数据输出锁存器,用于输出数据位的锁存。

(2)3个三态数据输入缓冲器BUF1、BUF2和BUF3,分别用于读锁存器、读引脚数据和第二功能数据的输入缓冲。

(3)输出驱动电路,由与非门、场效应管(FET)和内部上拉电阻组成。

2.工作过程分析

(1) P3日用作第二输入/输出功能 当选择第二输出功能时,该位的锁存器需要置1,使与非门为开启状态。当第二输出为1时,场效应管截止,P3.x引脚输出为1;当第二输出为0时,场效应管导通,P3.x引脚输出为0。

当选择第二输出功能时,该位的锁存器和第二输出功能端均应置1,保证场效应管截止,P3.x引脚的信息由输入缓冲器BUF3的输出获得。

(2) P3口用作第一功能——通用I/O口 当P3口用作第一功能通用输出时,第二输出功能端应保持高电平,与非门为开启状态。CPU输出1时,Q=l,场效应管截止,P3.x引脚输出为l;CPU输出0时,Q=0,场效应管导通,P3.x引脚输出为0。

当P3口用作第一功能通用输入时,P3.x位的输出锁存器和第二输出功能均应置1,场效应管截止,P3.x引脚信息通过输入BUF3和BUF2进入内部总线,完成“读引脚”操作。

当P3口实现第一功能通用输入时,也可以执行“读锁存器”操作,此时Q端信息经过缓冲器BUF1进入内部总线。

3.P3口的特点

P3口内部有上拉电阻,不存在高阻抗输入状态,为准双向口。

P3口作为第二功能的输出/输入或第一功能通用输入,均需将相应位的锁存器置1。实际应用中,由于复位后P3口锁存器自动置l,满足第二功能所需的条件,所以不需要任何设置工作,就可以进入第二功能操作。

当某位不作为第二功能使用时,可作为第一功能通用I/O口使用。

引脚输入部分有两个缓冲器,第二功能的输入信号取自缓冲器BUF3的输出端,第一功能的输入信号取自缓冲器BUF2的输出端。

P3口的第二功能定义见表2-1。

P1~P3口驱动LED发光二极管

下面以常见的P1~P3口驱动LED发光二极管问题为例,来讨论P1~P3口与LED发光二极管的驱动连接问题。

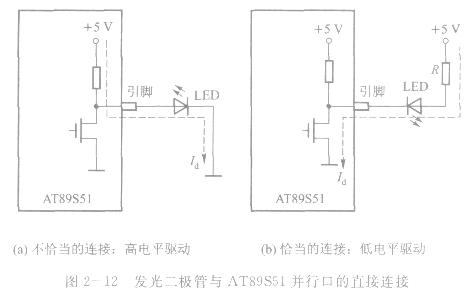

PO口与Pl、P2、P3口相比,PO口的驱动能力较大,每位可驱动8个LSTTL输入,而Pl、P2、P3口的每一位的驱动能力,只有PO口的一半。当PO口的某位为高电平时,可提供400 μA的电流;当PO口的某位为低电平(0.45 V)时,可提供3.2 mA的灌电流,如低电平允许提高,灌电流可相应加大。所以,任何一个口要想获得较大的驱动能力,只能用低电平输出。例如,使用单片机的并行口P1~P3直接驱动发光二极管,电路如图2-12所示。由于P1~P3口内部有30 kΩ左右的上拉电阻,如果高电平输出,则强行从Pl、P2和P3口输出的电流Id会造成单片机端口的损坏,如图2-12(a)所示。

如果端口引脚为低电平,能使电流Id从单片机的外部流入内部,则将大大增加流过的电流值,如图2-12(b)所示。所以,当P1~P3口驱动LED发光二极管时,应该采用低电平驱动。

上一篇:AT89S51的时钟电路与时序

下一篇:AT89S51存储器的结构

推荐阅读最新更新时间:2024-03-16 15:50

设计资源 培训 开发板 精华推荐

- 感恩季 送礼季!EEWORLD陪你玩着游戏奔新年

- 免费试用+优惠购+任务解锁赢好礼!这个夏天pyboardCN V2畅玩走起!

- Vicor白皮书下载——双向电源:“安静”改变世界的驱动力

- TI直播:精讲“双向CLLLC谐振、双有源电桥(DAB)参考设计”

- 吉时利DMM6500 6½ 位数字触摸屏万用表六大功能,满足工程师的切身需求,献给有梦想的你!

- 手机观看TI视频教程,随时随地充电学习

- 中秋芯币兑大礼

- MPS有奖分享|电感应用中,哪个问题最令你头大?

- 邀你参加:EEWORLD&ST 智能产品线下研讨会(12月6日-深圳)

- TI 最新CapTIvate™ 触控微控制器技术直播开始报名喽!报名参与有礼呦!

深入理解计算机系统

深入理解计算机系统 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号