随着科学技术的发展,嵌入式处理器在通信设备、消费电子、军用电子等领域有了广泛的应用,而且对处理器的处理速度、功耗及工作温度都有了更加严格的要求,尤其在汽车电子、军用电子等方面的应用。

Freescale公司的MlPC5200B是一款紧凑型、低功率的嵌入式处理器,与其他的嵌入式处理器相比具有独特之处,能满足上述的性能要求。MP(25200B集成有高性能的MPC603e内核,该内核采用超标量体系结构,能在400MHz的频率和一40~85℃的温度范围内处理速度为760MIPS,105℃时以264MHz(500MIPS)运行,适用于更高温度级别的环境。而且.MPC603e内核集成了一个高性能、双精度的浮点单元(FPU),可加快与其他关键任务平行的复杂数学运算的速度。可为大多数视频算法提供足够的支持。此外,MPC5200B集成了丰富的外设接口[1],其强大的功能符合汽车电子系统开发的需求,为系统的开发提供了保证。

2系统的硬件设计

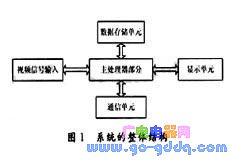

设计基于MPC5200B的嵌入式视频处理系统,在硬件方面需要提供全面的通信、足够的内存、调试功能以及测试显示功能。根据设计,本系统主要由主处理器部分、视频信号输入部分、数据存储部分、显示部分、通信部分等组成,如图1所示。

主处理器部分的设计主要包括了系统电源、PLL电源电路、时钟电路、软硬件复位电路、上电复位电路和下载调试电路等。

存储单元部分的存储器主要取决于微处理器的支持,MPC5200B支持的存储器主要包括SDRAM,ROM,FLASH,SRAM等。容量的大小取决于内核映射、操作系统、文件系统等的大小。

视频输入部分,模拟视频信号由差分电路输入,通过AD转换器AD9883A转换成数字信号,再送到MPC5200进行处理。

通信接口部分电路包括:人-机接口和机-机接口,提供了1个Ethernet接口、1个RS232接13、1个PCI接口、1个I2C接口等。

2.1存储系统设计

MPC5200B具有两组外部总线:SDRAM总线和LOCalPlus总线,SDRAM总线支持同步的单速率DRAM和双速率DRAM,采用突发式读取方式,提高了SDRAM总线的带宽。SDRAM总线的时钟频率等于内部总线XLBus的时钟频率。而LocalPlus总线一般可以和ROM,FLASH,SRAM及其他的外围设备相连接。

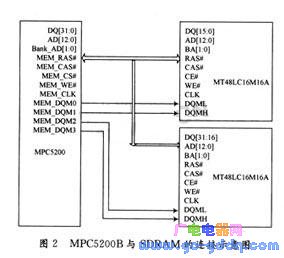

2.1.1MPC5200B与SDRAM的连接

MPC5200B内部自带16kB的SRAM,但需要扩展外部存储器,通过SDRAM控制器与外部SDRAM相连接,SDRAM用于存储系统所要处理的数据等。本系统采用两片MICRON公司的MT48LCl6M16A2SDRAM存储器,MT48LCl6M16A2是3.3V供电,支持自刷新模式,每8192个SDRAM时钟周期(64ms)刷新一次,其容量为256Mb,可配置为64M×4b,32M×8b,16M×16b。两片SDRAM可构成16M×32b的外部SDRAM存储器,连接原理图如图2所示。

当上电复位时,SDRAM总线是无效的,也就是说SDRAM的片选信号是无效的,所以上电时得先配置初始化寄存器,使SDRAM的片选信号有效,然后才能从SDRAM总线上读取数据,使系统正常运行。

SDRAM在上电100~200μs后,必须由一个初始化进程来配置SDRAM的模式寄存器,模式寄存器的值决定着SDRAM的工作方式,具体操作步骤如下:

(1)确定SDRAM的片选信号CS#的空间;

(2)根据SDRAM的参数和时钟频率计算存储器、控制器寄存器的值;

(3)写SDRAM的模式寄存器和控制寄存器。

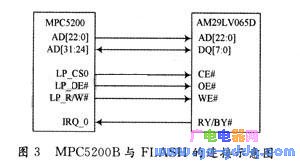

2.1.2MPC5200B与FLASH的连接

FLASH采用的是AMD公司的AM29LV065D,容量是8M×8B,支持3.0~3.6V的读、擦除和编程操作,用于存储系统的引导程序,与MPC5200B的连接原理图如图3所示。芯片AM29I。V065D是23根地址线和8根数据线,所以MPC5200B与AM29LV065D的连接可采用nonMUXed模式。MPC5200B的LocalPlus总线的高8位AD[31:24]作为数据线和FLASH的数据线相连接,而总线的低24位AD[23:0]作为地址总线与FLASH的地址线相连接。

因为系统上电后,系统从与LPCS0相连的存储设备启动,所以FLASH做BootROM时,片选信号CE#必须与MPC5200B的LPCS0引脚相连接。

FLASH是慢速设备,需要一些等待状态,因此在每次Boot时,需要默认最长的时间来启动MPC5200B。最长等待状态为48个PCIClocks(即727ns,当LocalPlus频率为66MHz时)。

2.2通信接口的设计

通信接口的主要功能是实现人-机、机-机之间的信息交互和数据的传输。主要设计包括以下几点:

Ethernet收发器采用的是Intel公司的芯片LXT972A,与MPC5200B的以太网口控制器相连。RXCLK与TXCLK:接收和发送时钟信号,由LXT972A提供,连接到MPC5200的以太网控制器端口。RXD[3:O],TXD[3:O]:分别为接收和发送信号,由MPC5200提供,连接到LXT972A的RXD和TXD13。TXEN:发送使能信号。COL::冲突监测信号,驱动控制器的冲突监测输入。

PCI接口控制器主要功能是实现主处理器与视频输入部分之间的数据传输。PCI的数据地址总线是复用的,均为MPC5200B的LocalPlus总线的数据地址总线,而PCI的控制信号线是由MPC5200的PCI控制器提供的。

RS232收发器采用的是MAXIM公司的MAX3232,与MPC5200B的UART口相连接。

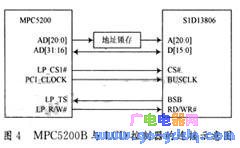

2.3与LCD控制器的接口设计

LCD控制器采用爱普生公司的液晶控制芯片S1D13806,S1D13806是高度集成的彩色LCD/CRT/TV图像控制器,内部集成有1280kb的SDRAM,支持多CPU接13,S1D13806的体系结构满足嵌入式系统的低电压、低功耗的要求。S1D13806具有21条地址线和16条独立的数据线,与LocalPlus总线的连接方式可为混合模式,因为MPC5200B的总线为数据、地址线复用的,所以需要地址锁存器来锁存地址。连接示意图如图4所示。

MPC5200B有3个基本的复位信号,上电复位、内部/外部硬件复位和内部/外部软件复位。

系统上电复位时间在上电后至少要保持35μs,这样系统时钟信号才能趋于一个稳定的状态。而硬件和软件复位信号要保持4095个时钟周期的低电平。

当外部硬件复位信号HRESET#有效时,内部复位逻辑捕捉到外部复位信号为低电平时,使内部硬件复位和软件复位信号保持4095个时钟周期的低电平。而只有当外部硬件复位信号至少保持4个时钟周期的有效电平后才能被确认为有效复位信号。MPC5200B的时钟分配模块(CDM)中的寄存器有软件复位设置位,可通过微处理器来设置。当这个寄存器中的软件复位位设置为0时,会引起外部和内部的软件复位[1]。

3系统的BSP配置

硬件系统设计完成以后还要进行嵌入式系统的设计。VxWorks以其优越的性能被广泛运用于各种嵌入式系统。

3.1BSP的概述

3.1.1BSP的功能

(1)初始化

CPU初始化初始化CPU内部状态寄存器、控制寄存器、高速缓存等。

目标机初始化初始化控制芯片的寄存器(如BUS,DMA,DRAM)、I/O寄存器,为上层软件系统提供硬件环境的支持。

系统资源初始化初始化操作系统,为操作系统正常运行进行资源初始化。

(2)提供VxWorks访问硬件的驱动程序和相关设备的初始化操作。

(3)集成了与硬件相关的软件和部分硬件无关的软件。

3.1.2BSP的组成

BSP由头文件、源文件、makefile文件和派生文件组成。

3.2调试过程

系统设计时采用Bootrom加VxWorks的方式,这种启动形式有其独特优点,如适应硬件、方便现场调试等。

本系统采用的调试工具是WindRiver公司的调试软件visionCLICK及仿真器WindRiverICE。具体步骤如下:

(2)上电后,用仿真器的串口连接电脑的RS232串口,打开超级终端,按下仿真器的复位键,在超级终端可看到仿真器的相关信息。主要看IPAddress,主机(host)的IP的地址要和仿真器的IP地址在同一IP段,在超级终端可运行help命令,可看到各种命令,均可运行。运行"eth-setup"命令可更改仿真器的IP地址。

(3)打开visionCLICK,新建工程,按照提示设置,主要有:configurationfile,symbolfile,downloadfile和sourcepath,其他的选项默认,生成bootromuncmp.ab和bootrom_unemp.bdx

(4)连接仿真器,下载,运行。提示无误后,可观察各窗口的寄存器,内存等单元的值,进行调试,如有错误,修改源代码,重新开始编译、下载,直到完全正确为止。

BootROM调试完后,把目标板的以太网口和主机的网口相连,BootROM会自动从网口引导,把编译好的VxWorks加载到目标板,进行调试。最后全部完成后,把BootROM和VxWorks都固化到目标板上,以便脱机运行。

4结语

系统的硬件设计完成后,在基于MPC5200B的嵌入式视频处理系统的硬件基础上,移植了嵌入式操作系统VxWorks,然后进行相关的驱动程序和应用程序的开发,并选择相应的视频图像处理算法,实现完整的嵌入式视频处理系统。实验结果表明,该系统满足视频信号处理的要求。随着科技的发展,嵌入式计算机在消费电子、通信设备、工业控制和军用电子等领域均有广泛的应用,所以本系统的应用前景是非常广泛的。

上一篇:基于CAN总线的嵌入式控制器串行通讯的应用

下一篇:基于嵌入式系统的负压吸引器设计

推荐阅读最新更新时间:2024-03-16 15:54

机器视觉技术 (陈兵旗)

机器视觉技术 (陈兵旗) DSP原理及图像处理应用

DSP原理及图像处理应用 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号