0 引言

过采样∑-△A/D转换器以其高精度和易于用标准数字CMOS工艺实现的特点而被广泛应用,并越来越多地集成到片上系统(SOC)中。∑-△ADC采用的是过采样和低位量化结合的方法,能够避免使用高精度模拟电路,将噪声推向高频,具有分辨率高、量化结构简单等优点。降采样滤波器作为过采样∑-△A/D转换器的重要组成部分,用于滤除基带信号带外噪声和降低抽样频率至临界抽样频率。目前国内∑-△ADC的研究主要集中在音频领域,带宽20 kHz。本文介绍了一种带宽150 kHz、16 bit∑-△模数转换器中的降采样滤波器的设计与实现。

1 ∑-△ADC的主要性能指标

信号与噪声加失真比(SINAD)是直流到奈奎斯特频段内,正弦波的RMS(均方根,表示交流信号的有效值或有效直流值)值与转换器噪声的RMS值之比,包括谐波成分。

信噪比(RSN)是直流到奈奎斯特频段内,正弦波的RMS值与转换器噪声的RMS值之比。

无杂散动态范围(SFDR)是RMS信号幅度与最大杂散频谱分量RMS值的比率。

总谐波失真(THD)是出现在输入频率整数倍频点(谐波)失真的RMS值与输入(或输出)正弦波的RMS值之比。

有效位数(ENOB)与SINAD的关系为

本设计要达到的性能指标是ENOB≥14 bit;SINAI)≥86 dB;SFDR≥92 dB;THD≤一90 dB;信号带宽为150 kHz;精度为16 bit。

2 调制器的系统设计

2.1 低阶∑-△调制器

调制器中的阶数即积分器的个数,一阶∑-△调制器的信噪比

RSN=6.02N+1.76—5.17+301g(OSR) (2)

式中:N为模拟调制器中量化器的位数;OSR为过采样比。式(2)表明,当OSR足够大时,在理论上也可获得相当好的量化信噪比。

2.2 高阶∑一△调制器

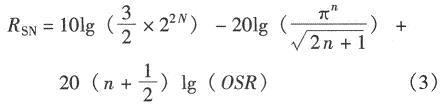

高阶∑-△调制器理想信噪比

式中n为调制器阶数。

但是在使用一位量化器情况下,环内滤波器增加到三阶以上时,工作情况会变得不稳定。

2.3 本设计中的∑一△调制器

本设计采用三阶∑-△调制器(n=3),OSR为128,调制器的量化器用1 bit进行量化(N=1,降低模拟电路设计的难度)。由式(3)可得RSN=133.9 dB,满足16 bit精度要求。

设计要求带宽为150 kHz,而过采样率设为128,则理想情况下为

fs=150 kHz×2×128=38.4 MHz

考虑到系统设计和实现的非理想特性,本设计的采样频率定为50 MHz,经过128倍降采样后ADC的输出数据速率为390.625 kHz。

本系统设计在Matlab 7.0环境下采用Mathworks公司的Delta-Sigma Toolbox中提供的迭代逼近法实现满足要求的噪声传输函数,得到初始结构参数。并根据文献得到∑-△调制器的三阶CRFB系统实现模型,对该模型的性能分析可得其峰值信噪比达到113.2 dB,满足16 bit精度要求。

3 降采样滤波器的设计和系统仿真

本设计中的降采样滤波器由级联积分梳状滤波器、频率补偿滤波器和FIR半带滤波器级联组成。其中级联积分梳状滤波器实现多倍降采样,频率补偿滤波器针对多倍降采样后的通带下降进行补偿,而FIR型半带滤波器硬件结构非常简单并且适合实现D=2倍降采样,因此作为本降采样系统中的最后一级。

3.1 级联积分梳状滤波器

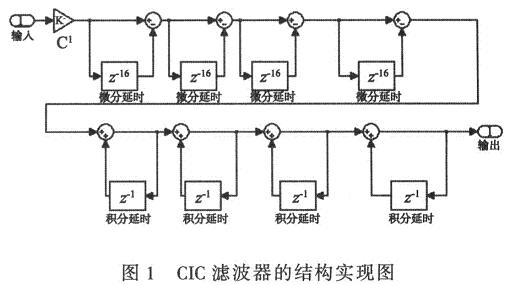

CIC滤波器是由积分模块与梳状滤波器模块组成的一种滤波器。Hogenauer提供了输入、输出比特数之间的关系,它们之间满足

![]()

本设计中CIC滤波器的降频倍数R为16,调制器输出一位量化的数据,Bin=1。而参考文献指出,CIC的级数要求大于调制器的阶数,因此本设计的级数N=4。由式(4)得Bout=17,满足精度要求。CIC滤波器的结构用Matlab 7.0中Simulink Library搭建,实现如图1所示。

3.2 频率补偿滤波器

CIC存在着通带下降的问题。观察CIC滤波器的幅频响应图发现f=150 kHz时,Magnitude=O.996 l,而本设计的ENOB要求达到14 bit,即误差应小于2-14,无法满足。因此,本设计引入了Sharpened CIC和ISOP两种补偿技术对CIC的通带下降进行补偿。

3.2.1 Sharpened CIC滤波器

参考文献提出的一种新的CIC结构是基于由J.Kaiser和R.Hamming提出对滤波器响应进行锐化的技术。这项新的技术尝试通过复用相同的滤波器来同时减小通带下降和提高阻带衰减。Sharpened CIC的结构框图如图2所示。

而本设计中CIC滤波器的群延时为30,其中的H(z)为CIC滤波器的传输函数。

3.2.2 ISOP滤波器

CIC抽取滤波器通带下降这一问题还可以通过级联内插二阶多项式获得部分解决。ISOP滤波器的系统函数为

式中:I为正整数;c为实数。

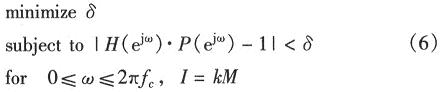

如果CIC滤波器已经确定,则最佳ISOP滤波器可以采用切比雪夫逼近法设计。对所有满足 的整数k,解如下方程

的整数k,解如下方程

可得到使δ最小的一组(k,c)对。

本设计中,k=4,c=1 617.19,f=166 kHz时Magnitude=0.999 947,满足ENOB为14 bit的要求,并为后面的设计留下16 kHz的冗余空间。

3.3 FIR半带滤波器

FIR型半带滤波器是一种特别适合实现D=2倍降采样的线性相位滤波器,其硬件结构非常简单,因此在降采样系统中的最后一级一般都采用半带滤波器。

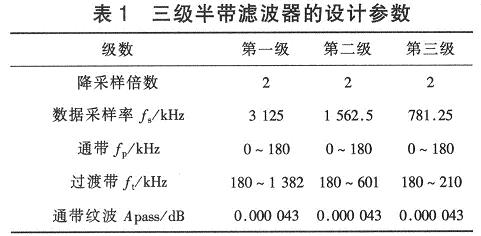

根据∑一△ADC的技术指标,可以得到三级半带滤波器的设计参数,如表1所示。

通带设为O~180 kHz,是为了保证0~150 kHz带宽内均能满足指标要求。通带纹波取0.000 005(0.000 043 dB),是为了满足设计的有效位数为14 bit,并且考虑到尾数舍入等非理想因素的存在。

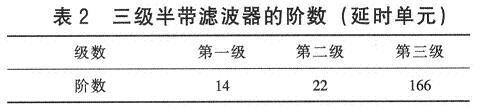

根据表1,调用Matlab 7.O中的工具箱组件filter design,得到三级半带滤波器的系数。表2分别列出了三级半带滤波器的阶数(延时单元)。

3.4 系统仿真与验证

实现∑-△ADC的整体结构如图3所示,抽取滤波器由Sharpened CIC滤波器、ISOP滤波器和三级半带滤波器组成。Sharpened CIC实现16倍抽取,三级半带滤波器实现8倍抽取。

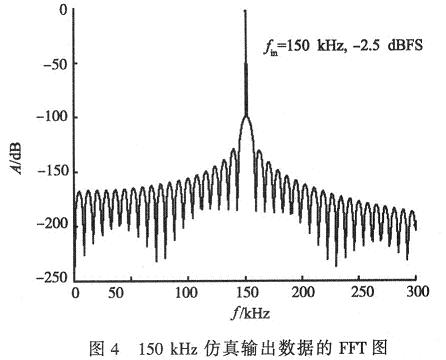

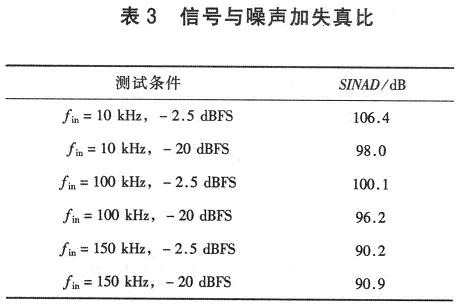

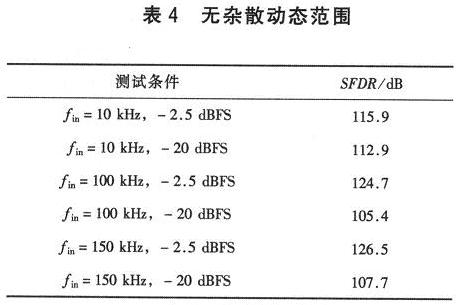

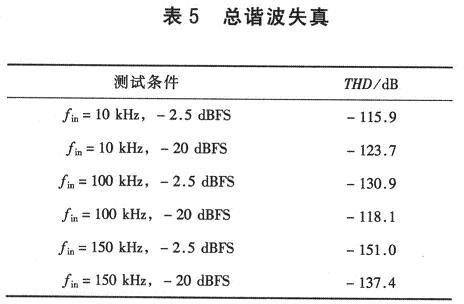

图4为150 kHz输入信号(一2.5 dBFS)仿真输出数据的FFT图。表3、4、5分别为SINAD、SFDR和THD的仿真数据。

4 降采样滤波器的ASIC设计

4.1 电路设计

本设计用Verilog硬件描述语言描述电路,采用Synopsys的Design Compiler进行综合。

4.1.1 滤波器系数优化

本设计采用CSD码(canonical signed-digit)来表示量化后的系数。和二进制代码相比CSD码采用0、l和一1来表示一个数,具有非零位的个数最少、每一个非零位的相邻位必为零的特点。

4.1.2 乘法器设计

本设计中乘法器单元的上限定为16×16,本文采用了Synopsys提供的DesignWare库中的16×16乘法器单元,该单元的设计和综合都比较成熟,通过Design Compiler综合后面积和速度的优化都比较理想。对于位数高于16 x 16的乘法器,本文以16×16乘法器单元先进行低位乘法运算,再进行高位乘法运算,最后再将高低位结果移位相加得到最终的乘法结果。

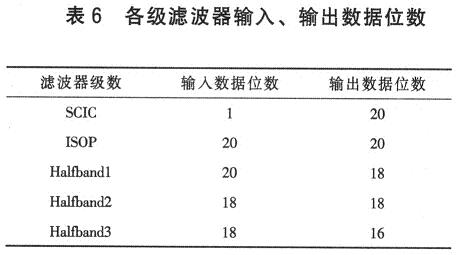

4.1.3 各级间输入输出位数的确定

本文设计了一个滤波器各级位数动态可调的方法,对降采样滤波器各级输入、输出位数各种可能的情况进行分析,得到最终的各级滤波器的输入输出数据位数如表6所示。

4.1.4 时钟的处理

系统用到了多个分频时钟,为了方便后面布局布线做时钟树,本设计采用计数器产生使能信号进行分频。

4.1.5 Design Compiler综合

本设计采用SMIC 0.18μm CMOS工艺库,将编写的Verilog代码用Synopsy的Design Compiler综合,通过加上适当的约束条件反复优化,最终得到综合结果。综合结果通过Synopsys VCS仿真验证。

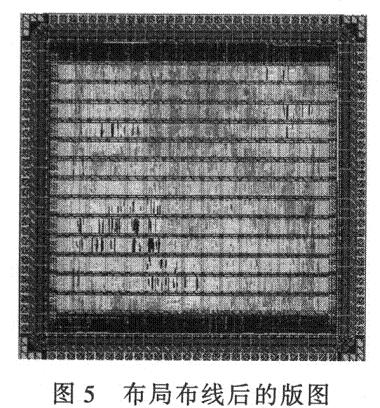

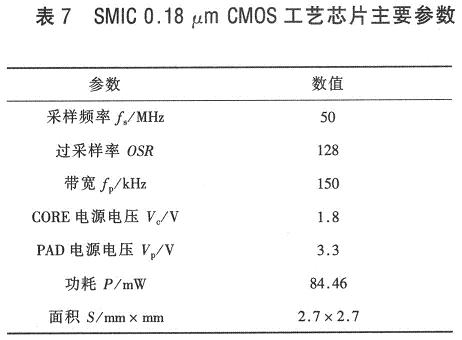

4.2 版图设计

本设计采用Cadence Encounter对综合后的滤波器的门级网表进行布局布线,图5是完成布局布线后的版图。芯片主要参数如表7所示。

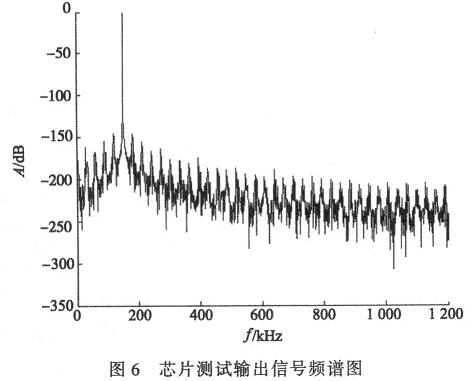

5 芯片测试

在模拟三阶CRFB结构的∑-△调制器输入的情况下,通过逻辑分析仪采集输入为150 kHz正弦信号的输出数据,并由计算得到的频谱如图6所示,信号与噪声加失真比(SINAD)大于86 dB,满足性能指标要求。

6 结论

本文介绍了一个用于带宽150 kHz、精度16 bit的高精度、宽带∑-△模数转换器中的降采样低通滤波器。本设计可以集成在SOC芯片中,主要应用于医疗仪器、移动通信、过程控制和PDA等领域。滤波器通过级联Sharpened CIC滤波器、ISOP滤波器和半带滤波器实现。并通过Synopsy的Design Compiler进行电路综合和Cadence Encounter进行布局布线,采用SMIC 0.18μm CMOS工艺实现。系统仿真和芯片测试结果表明,性能满足设计指标要求。

上一篇:Linear推出超低功率14 位150Msps模数转换器

下一篇:8bit 800Msps高速采样保持电路的设计

推荐阅读最新更新时间:2023-10-12 20:14

- CGD和Qorvo将共同革新电机控制解决方案

- 是德科技 FieldFox 手持式分析仪配合 VDI 扩频模块,实现毫米波分析功能

- 贸泽开售可精确测量CO2水平的 英飞凌PASCO2V15 XENSIV PAS CO2 5V传感器

- 玩法进阶,浩亭让您的PCB板端连接达到新高度!

- 长城汽车研发新篇章:固态电池技术引领未来

- 纳芯微提供全场景GaN驱动IC解决方案

- 解读华为固态电池新专利,2030 叫板宁德时代?

- 让纯电/插混车抓狂?中企推全球首款-40℃可放电增混电池,不怕冷

- 智驾域控知多少:中低端车型加速上车,行泊一体方案占主体

- Foresight推出六款先进立体传感器套件 彻底改变工业和汽车3D感知

电子技术基础 (王建民)

电子技术基础 (王建民) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号