数字反馈

数字反馈可能由于容性耦合、地电流或甚至波导动作而产生。即使是非常之小的反馈因素也会在 ADC 输出频谱中引起不希望有的音调。当一个无偏移的 ADC 接收一个 1LSB 量级的非常微弱信号时,这个 ADC 非常像一个具 120dB 增益的放大器:被驱动的所有输出将以与输入信号相同的频率提供极大的功率。

数字反馈可能发生在器件级或系统级上。ADC 之前的宽带增益会加重这种影响。在低信号电平时,数字反馈可能以增大的奇次谐波形式出现,或者在延迟的反馈作用下改变噪声层的形状,或者以某种噪声层增大的形式出现。积分噪声性能通常不会受到太大的影响,不过在严重的情况下,噪声层的集中区域有可能被抬升 20dB 之多。如果有一个碰巧与抬高的噪声层区域撞上的窄带应用,那么这就意味着实实在在的 20dB 量级的信噪比 (SNR) 损失。

在低信号电平下,如果失调电压很大 (以致代码不能穿过主要的位边界),则数字反馈被消除。在数字反馈难以控制的地方,可以考虑故意引入偏移电压。在高信号电平时,数字反馈一般在一定程度上被解除了相关性,因此不像在低信号电平时那么明显。但这时数字反馈仍然可能在某种程度上降低 SNR。

在确定是否发生数字反馈的过程中,有意引入或清除失调电压的能力可以是一种有效的工具。假如,当存在一个低信号电平时,SNR 在引入失调电压的情况下有所改善,则表明正在发生数字反馈。

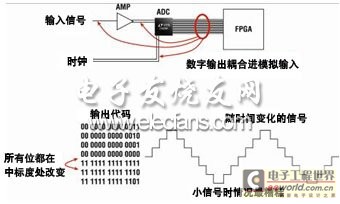

图 1:严重数字反馈的典型表现 (采用 6 级流水线时)

图 1 显示了相对严重的高频数字反馈的模拟结果,该情形与我们研究过的客户的一些布局实例产生的结果非常相像。尽管是以更加严重的形式,但是这仍然代表了 ADC 本身的反馈机制。

噪声层的整形与流水线延迟有关。具有偶数流水线级的 ADC 将在奈奎斯特频率下产生一个峰值 (而不是这里所观察到的为零)。如果所关注的频谱区域局限于 DC 和 1/4 奈奎斯特 (Nyquist) 频率之间,您可以认为数字反馈不是问题。具有一个较大流水线延迟的 ADC 将在这些特性之间呈现较短的时间间隔。

进入编码时钟的数字反馈可能产生 2 阶和 4 阶甚至其他阶谐波,但是仅在较高信号电平时才比较明显。这与以下情况类似:耦合进时钟的模拟输入功率会对时钟进行相位调制,从而产生 2 阶谐波失真。进入放大器或进入非快速稳定网络的较低频率反馈,可能产生有一些零点、而不是抬高某些区域的噪声层,而且可能往往提高靠近 DC 或奈奎斯特频率的区域。实际情况也许涉及这些反馈机制中的若干种,这往往会产生更加复杂的噪声层。

图 2:进入未实现良好稳定网络中放大的较低频数字反馈示例

图 2 仅示出了低频反馈的一个例子。这种工作特性可能并不稳定,因而会产生出现在不同位置的“零”。这些深谷零的位置提供了起因的相关线索,因为它们指示了在频域中的那些点上产生极小功率的重复图形。这可被看作是一个精细复杂的弛豫振荡器,涉及 ADC 之前的增益以及各种延迟 (包括流水线延迟)。一个高阶滤波器可以改变这种反馈行为,或者在采用具微秒延迟的 SAW 滤波器的情况下,可以相当有效地控制反馈行为。这种不稳定的反馈行为是由热噪声和输入电源激发的。对多次转换进行平均后,这类反馈行为可以产生相当一致的噪声层升高。例如,通过在驱动器放大器下面走数据总线,可以产生这类反馈行为。

如果选择了不良的布局,则器件级和系统级上的数字反馈均会变得更糟。通常,给定的设计似乎将拥有兼顾这方面性能所需的全部特性。长的输出总线、以低特性阻抗布线以及在接收设备端很重的容性负载所有这一切都导致在输出级产生更大的脉冲电流。类似地,采用最大的 OVDD (数字输出电源电压) 最大限度地增大了数字电流。如果降低数字输出电压摆幅,就会相应地降低耦合回模拟电路的数字噪声。在电路板底面放置 OVDD 旁路、增大引线电感、大体积电容器、小直径通孔、厚的电路板、散热等等所有这一切都增大了电源轨至输出部分的阻抗,从而增大了跨地回路产生的信号。把 OGND 回接至一个接地不良的焊盘会使情况更糟。所有这些都将在 IC 基片上导致更多的接地反弹。使事情更糟的是,非对称地处理模拟和时钟输入也会导致数字反馈。对称地处理这些输入将保持采样过程或时钟接收器的共模抑制,并降低数字反馈。举一个不对称的例子: 将一个大测试焊盘放置在刚好位于ADC 下方的电路板底部的两个输入之一上,而将另一个测试焊盘安放于一定距离之外的另一个输入上,这种做法可以满足线路内测试人员的要求,但这种不对称性将会损害 ADC 性能。如果您必须提供探测,则把测试焊盘并排放置,使信号走线从中穿过,并在这些元件之后靠近 ADC 的地方布设终端。测试焊盘是无引线的电容器,如果这么用,而不是在不同长度的传输线尾端充当起缩短作用的容性组件,那么在 GHz 频率上也许是有益的。

避免将一个输入布置在电路板顶面,另一个布置在电路板底面,这听起来也许是显然的事。除了与高频行为有关的非对称,这样的布置还会拾取布满电路板走线的两个平面之间的电位差。

甚至不要用层的改变使差分放大器的输出反向。差分放大器的 + 输出不必一定驱动 ADC 的 + 输入,它们是可互换的。就 AC 应用而言,这一般来说没有关系。如果确实有关系,那么在驱动器之前实现。

内部数字反馈大部分是一种高频现象。较低的采样率往往不那么成问题,除非到负载的距离增大了。如果从负载返回的反射信号在不到 1/2 个时钟周期内消失,那么它们就不会产生数字反馈。

新的 ADC 帮助克服数字反馈

当数字输出回馈耦合至模拟电路部分时,数字反馈将出现,从而引起干扰。这种干扰在噪声层中表现为异常的整形,而在 ADC 输出频谱中则表现为寄生噪声。最糟糕的情况出现在中标度处,这采用 CMOS 输出模式,所有输出从 1 切换为 0 (2 进制补码格式) 或从 0 切换为 1,从而产生大的地电流,如图 3 所示。

图 3:ADC 中的数字反馈

跨过这个中标度点的小信号在所有这些数字信号输出的和中产生一个不相称的输出功率。

凌力尔特已经推出了 LTC2261 系列超低功率 14 位 /12 位、25Msps 至 150Msps ADC,提供了一种新的和专有的功能,可在甚至良好的布局做法也无效的情况下减少数字反馈。交替位极性 (ABP) 模式在输出缓冲器之前使所有奇数位反相,以当工作在中标度周围时,实现数目相等的 1 和 0 的切换,从而有效地消除了引起数字反馈的大的地平面电流。

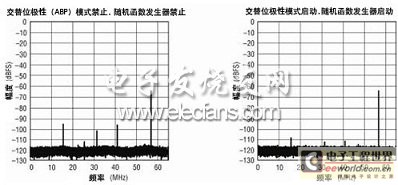

图 4:交替位极性模式

图 4 显示了怎样利用交替位极性模式改变数字输出字。消除地平面电流,以在小的输入信号跨过中标度时,减少反馈回 ADC 输入的能量。当这种模式启动时,所有奇数位 (D1、D3、D5、D7、D9、D11、D13) 在输出缓冲器之前都反相,如图 5 所示。偶数位 (D0、D2、D4、D6、D8、D10、D12) 不受影响。这种方法可降低电路板地平面中的数字电流,并降低数字噪声,尤其是在模拟输入信号非常小的情况下。通过使奇数位反相,在接收器端对数字输出解码。利用简单的 SPI 连接至 ADC,通过串行设定启动交替位极性模式。

图 5:对交替位极性模式数据解码

除了交替位极性模式,还提供一个可选数据输出随机函数发生器,以减少来自数字输出的干扰。该随机函数发生器解除了数字输出的相关性,以减少出现重复码的可能性,从而避免重复码耦合回 ADC 输入,在输出频谱中引起不想要的音调。通过在数字输出被传送至芯片之外以前对其进行随机化处理,即可实现这些无用音调的随机化以减小此类音调的幅度。

数字输出通过在 LSB (实际上是白噪声) 与所有其他数据输出位之间运用一种“异”逻辑运算来进行“随机化”。如欲解码,则采用逆运算;在 LSB 与所有其他位之间应用一种“异”运算。交替位极性模式与数字输出随机函数发生器无关 ━━ 这两种功能可以同时接通、同时不接通或任一接通。如示,两种数字反馈抑制方法 (交替位极性模式和数字输出随机函数发生器) 可使无寄生动态范围 (SFDR) 性能改善 10~15dB。

图 6 示出了 LTC2261 对一个 70MHz IF、-65dBFS 输入信号进行采样并折返至 ADC 的第一奈奎斯特区域的 FFT 曲线图。左侧的曲线图示出了采用交替位极性模式 (数字输出随机函数发生器被停用) 时的 ADC 性能。噪声层中的凸起和输出频谱中的寄生噪声由数字反馈引起,输入端上的低电平信号使数字反馈有所衰减 (数字输出在全“1”和全“0”之间切换)。凸起的数目对应于 ADC 中流水线级的数目。右侧的 FFT 曲线图示出了同时采用交替位极性模式和随机函数发生器时 SFDR 性能的改善情况。噪声层现在很平坦,而且最高的寄生噪声减低了 12dB。

图 6:运用交替位极性模式和随机函数发生器时 LTC2261-14 的 SFDR 性能。

Fs=125Msps,AIN= 70MHz、-65dBFS,平均 128k 点 FFT

与今天市场上提供的同样采样率和分辨率的可比较 ADC 相比,LTC2261 系列 ADC 的功耗仅为其 1/3。LTC2261-14 为 14 位 125Msps ADC 仅从 1.8V 模拟电源消耗 127mW 功率,而 14 位 25Msps ADC LTC2256-14 仅消耗 30mW 功率 (参见图 7 以了解整个系列的器件)。为了进一步节省功率,还提供了打盹或休眠模式,以使功率降至 0.5mW。

图 7:超低功率 1.8V ADC 系列

LTC2261 是一款极端灵活的高速 ADC,具一个 SPI 兼容的接口,以设定和调节若干独特的设置。SPI 端口用于选择数字输出配置 (CMOS、DDR CMOS、DDR LVDS)、从 7 种 LVDS 输出电流设定值中进行选择,以根据所驱动的负载或距离决定最佳的功率要求,或启用任选的 LVDS 输出终端来帮助消减由接收器上的不良终接所引起的任何反射,从而节省了外部组件和板级空间。还可以选择测试模式,以允许用户验证 ADC 和处理器之间的连接。

结论

在采样情况下,良好布局仍然不能提供避免数字反馈所需的隔离,LTC2261 的内置功能可用来帮助抵消引发这种不良干扰的地电流。LTC2261 提供极高的灵活性和调节能力,以改善数据采集系统的性能。

上一篇:一种单键开关机和复位方案

下一篇:基于DP标准发射端扩频时钟发生器电路设计

推荐阅读最新更新时间:2023-10-12 20:32

- ADI有奖下载活动之21:ADI民用雷达解决方案

- 下资料赢京东卡|泰克公司的创新一代触摸屏示波器

- “慧眼”识PCIe——阅读《PCIe要了解的十件事》和泰克OPEN-DAY的培训资料 抽奖、分享赢好礼!

- 关注 PI 最新 SCALE-iDriver IC产品系列 答题有好礼!

- 【在线研讨会】ADI RadioVerse™技术与集成DPD算法的RF收发器AD9375

- 预报名有奖直播:煮酒数创客,看如何让好创意发生!

- 【EE团拍卖】RealARM6410 零元风暴来袭,你能HOLD住吗?

- 如何加快你的FPGA设计步伐

- 英特尔 SoC FPGA 开发者论坛 (ISDF) 预约报名享好礼!

- 你玩板我有奖|老板新玩还有奖

电子技术 数字部分 (任希)

电子技术 数字部分 (任希) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号