任意波形发生器是目前电子测量仪器中发展最为快速的产品之一。它既可输出标准函数信号,也可以产生由用户定义的非标准函数波形(任意波形)信号,并且有丰富的模拟调制(AM,FM,PM)和数字调制(FSK,PSK)功能,能为不同的应用领域提供各种标准或非标准信号,尤其在水下声纳、通信、雷达导航、电子对抗等装备的研制、生产、维修中,是必不可少的信号发生器。基于数字频率合成技术,给出高速任意波形发生器的设计方案。

1 高速任意波形发生器的硬件设计

1.1 任意波形发生器的工作原理

目前任意波形发生器的产生有两种方案,一种方案是采用直接数字频率合成(DDS)技术产生任意波形,工作原理如图1所示。

一个标准的DDS电路应当由以下几部分构成,既相位累加器、波形存储器、D/A转换器、低通或带通滤波器构成。任意波形数据预先通过人机接口写入波形存储器中,相位累加器的作用是根据输入的频率控制字对参考振荡器输出的时钟相位进行采样。当相位累加器的步长为K时。任意波形的输出频率

式中,Fs为固定采样时钟频率,n为相位累加器长度,改变频率控制字K,就可以改变DDS的输出频率。

采用DDS技术构成的任意波形发生器具有输出频率分辨率高、频率改变相位连续等优点,但也存在两个重要缺陷。首先是当相位累加器的相位增量步长较大时,输出波形将产生抖动;其次由于DDS技术不是逐点读取波形存储器中的数据,因此输出波形会丢失许多有用的信息。

任意波形发生器的另外一种设计方案如图2所示,其工作原理是任意波形发生器的时钟通过使计数器加1来改变由计数器构成的地址产生电路的输出地址,计数器顺序扫过波形存储器中的每一个地址直到波形数据的末端,每个地址中的波形数据都被送至D/A转换器中以将数字信号转为模拟信号,而后D/A转换器的输出信号还需经过低通滤波器对D/A转换器输出信号的跃变边缘进行平滑处理得到所需的任意波形。在这种方案中,所有波形数据都被送入D/A转换器中,所以不会丢失波形数据,但要全部输出波形存储器中定义的波形数据内容,并且任意波形的输出信号频率可变,那么取样时钟的频率就必需是可变的,这点与由DDS构成的任意波形发生器有着明显的区别。采用该方案任意波形的输出频率

式中,Fs为可变采样时钟频率。

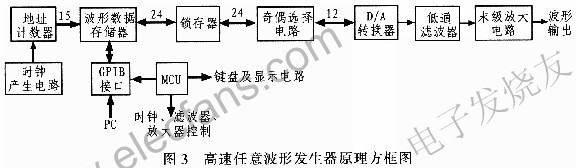

使用该方案电路结构简单,能够输出复杂的任意波形,对于高速任意波形发生器最为适合。基于该方案的任意波形发生器采样速率可达200百万次/秒,任意波形的最高输出频率可以达到50 MHz。高速任意波形发生器波形总体电路的方框图如图3所示。

1.2 任意波形产生电路的设计

如图4所示,一个完整的任意波形产生电路主要由时钟发生电路、地址计数器、波形存储器、锁存器、奇偶数据选择电路以及D/A转换器构成。

时钟发生电路用于产生任意波形发生器所需的可变时钟,通常可以由单片机控制的锁相环电路构成,在实际设计中采用锁相环集成电路,产生最高频率为100 MHz的时钟信号,时钟电路的输出信号送往地址计数器的时钟输入端,以驱动地址计数器扫描波形存储器中的数据,地址计数器采用15位二进制同步计数器,逻辑上等同于4片74F161级联,地址计数器输出的15位地址数据与波形存储器的地址输入端相连,波形存储器使用四片32 K×8(读写速度为12 ns)的SRAM级联成32 K×32的SRAM阵列,SRAM阵列输出端的32比特数据中,24比特为波形数据,2比特为控制信号,其余6比特数据线不使用。每个波形点分辨率为12比特,每个地址存放两个波形点的数据,单片段任意波信号最长可达64 K个点,2个控制信号分别为停止位、同步位,停止位数据线通过D触发器与地址计数器的预置数控制端端相连,当检测到扫描至最后一个波形地址时,停止位将地址计数器的预置数控制端置位,这样在下一个时钟到来时,地址计数器又从该任意波形的首地址寻址,读取波形数据。控制信号中的同步位用于输出外同步信号。波形存储器输出的24位任意波形数据由锁存器锁存后送往12位奇偶数据选择电路的输入端。如前所述,波形存储器的每个地址存放两个点的波形数据,在通过人机接口向波形存储器写入波形数据时,一个点的波形数据由每个地址中的奇数位数据构成,另外一个点的数据由偶数位构成,这样做的好处是每个采样时钟到来时,可同时读取2个波形点的数据,使得输出波形的最高频

率增大了1倍,相当于采样时钟的频率提高了1倍,大大提高仪器性能。12位奇偶数据选择电路逻辑上等同于3片74F157。奇偶数据选择电路的输出端与D/A转换器的输入端相连,D/A转换器的作用是将从波形存储器中读取的数字信号转换为模拟信号,由于最高时钟频率为100 MHz,所以D/A转换器选择速率为125百万次/秒的AD975。根据采样定律输出信号的基波频率将低于所用的参考时钟频率的一半,在本方案中采样时钟最高频率为100 MHz,一个任意波形最少可由4个点构成,并且每个时钟周期读取两个波形数据,因此所输出的任意波形信号的最高频率为50 MHz。上述电路中,15位同步二进制地址计数器、24位锁存器、12位奇偶数据选择电路及相关控制电路也可由高速CPLD实现。

1.3 滤波器设计

经过D/A转换后的信号通常含有较多的时钟成分及较为陡峭的跃变边缘,为了减少输出波形的抖动、抑制高次谐波,在任意波形发生器的设计中选择有效的滤波器就显得非常重要,高速任意波形发生器即能输出正弦波,又可输出三角波、锯齿波、脉冲波以及任意波型,因此要根据不同频段和波形来选择不同性能的滤波器,椭圆(Elliptic)滤波器具有陡峭的过渡特性,适合用作正弦波的输出滤波器,三角波、锯齿波和任意波具有丰富的频谱,因此要求滤波器在通带范围内具有良好的幅频特性,以保证信号通过滤波器后即不产生失真,又能滤去杂散信号。椭圆滤波器对正弦波以外的其他波形会产生剧烈的振铃,而具有线形相位的高斯(Gaussian)滤波器可以满足这些要求,在本方案中由于任意波形发生器的采样时钟可变,因此它的低通滤波器的截止频率也必须变化,否则在有些频段就不起滤波作用,或者是在高频段有用信号会被衰减,为此本设计方案中采用截止频率为25 MHz、50 MHz的七阶椭圆滤波器以及截止频率为20 MHz高斯滤波器,由单片机根据不同情况编程选择。图5给出了截止频率为50 MHz的七阶椭圆滤波器以及截止频率为20 MHz高斯滤波器的电路。

1.4 GPIB接口设计

尽管目前在智能仪器中有许多新的接口标准,比如USB、LAN等,但是GPIB(General Purpose Interface Bus)接口仍然是业界公认的智能仪器标准接口,在本方案中采用GPIB接口由PC机向任意波形发生器下载数据,并可通过GPIB总线远程控制任意波形发生器,GPIB接口电路由采用NI公司的NAT7210 GPIB专用集成电路和TI公司生产的GPIB总线驱动器SN75160以及SN75162构成,NAT7210输出的是标准的GPIB格式数据,符合IEEE488.2标准,GPIB总线驱动器的作用是增强接口的驱动能力。NAT7210与SN75160、SN75161以及单片机之间的连接方法参见文献。

2 高速任意波形发生器的软件设计

高速任意波形发生器的软件包括PC机部分的波形编辑及下载软件以及仪器内部的单片机控制软件两部分,波形编辑及下载软件具备各种任意波形编辑能力,例如直线编辑方式、曲线编辑方式、公式编辑方式、调制波形编辑方式。波形编辑及下载软件能够通过GPIB接口与任意波形发生器通信完成任意波形数据的下载及仪器的远程监控。仪器内部的单片机控制软件结构采用经典的主程序循环和中断服务模式,其流程图如图6所示。仪器加电后,首先进行自检和软、硬件的初始化,再进入主程序的循环,主程序的循环是等待中断处理的过程,它依据中断请求判断中断源,开中断并转向相应的中断处理子程序,完成对应操作或硬件控制。

3 结束语

经过对完成的任意波形发生器样机进行测试,采用该方案的任意波形发生器能够输出低至10 MHz、高达50 MHz的任意波形,输出波形稳定,无波形数据丢失现象,通过PC机上的波形编辑软件,能够产生种类丰富的任意波形,可广泛应用在国防、科研、教育及工业生产等各个领域。

上一篇:基于Agilent ADS仿真软件的高效GaN宽禁带功率放大

下一篇:超小型低噪声放大器MAX2664和MAX2665

推荐阅读最新更新时间:2023-10-12 20:35

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号