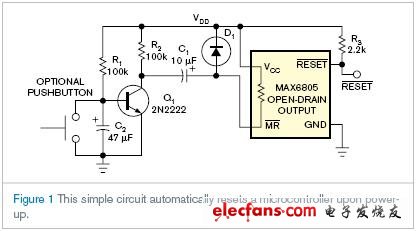

通过给晶体管增加一些电容、二极管和电阻,使用保持时间可调的复位IC,将纯手动复位转换为自动复位。

在大多数应用中, (手动复位)引脚通常与开关相连,为管理芯片制造手动复位信号。随后,在预先设定的有效延时时间后,其从低电平有效复位回到高电平状态。手动复位适用于大多数应用;然而,它需要人为干涉产生复位信号。在一些应用中,手动复位存在争议,因为系统每次上电时都要执行。

(手动复位)引脚通常与开关相连,为管理芯片制造手动复位信号。随后,在预先设定的有效延时时间后,其从低电平有效复位回到高电平状态。手动复位适用于大多数应用;然而,它需要人为干涉产生复位信号。在一些应用中,手动复位存在争议,因为系统每次上电时都要执行。

更进一步,包括嵌入式处理器在内的应用需要复位输出为保持高电平——也就是说,非有效——在应用复位或低有效之前的某个时期。如图1电路在设备上电时无需按下复位键的情况下,被证实是有效的,因为在复位的低信号到来之前,复位自动以预先设定的保持时间发生。

电路使用带 引脚和低有效输出

引脚和低有效输出 的复位管理芯片。通常

的复位管理芯片。通常 输入的内部上拉电阻为20到50kΩ。上电期间,

输入的内部上拉电阻为20到50kΩ。上电期间, 内部电阻将电容C1充电到正向最大值VDD。为管理芯片产生

内部电阻将电容C1充电到正向最大值VDD。为管理芯片产生 复位输入,其

复位输入,其 输入必须接收低有效的地信号,需要晶体管Q1导通。这个导通的时间长度取决于R1和C2的RC时间常数。这两个器件决定Q1什么时候导通,从而为

输入必须接收低有效的地信号,需要晶体管Q1导通。这个导通的时间长度取决于R1和C2的RC时间常数。这两个器件决定Q1什么时候导通,从而为 输出提供保持时间可调的高电平。为增加保持时间,增加R1和C2的RC时

输出提供保持时间可调的高电平。为增加保持时间,增加R1和C2的RC时

间常数即可。

复位管理芯片只在 管脚的电压超过触发阈值电压和管理器内部复位周期结束时,产生

管脚的电压超过触发阈值电压和管理器内部复位周期结束时,产生 输出。这个延时时间滤除了所有输入电压的毛刺。因为Q1的导通,使C1的负向变为地。而C1的正向不能立即改变极性,其被拉低并通过

输出。这个延时时间滤除了所有输入电压的毛刺。因为Q1的导通,使C1的负向变为地。而C1的正向不能立即改变极性,其被拉低并通过 输入的内部上拉电阻,缓慢的再次充电。当达到复位芯片的阈值电压时,一旦达到芯片的延时时间便输出复位信号。C1的选择并不严格。然而,它的值应该尽量大——例如0.1到10µF——使C1和内部上拉电阻所得的RC时间常数足够大。这个值确保C1在

输入的内部上拉电阻,缓慢的再次充电。当达到复位芯片的阈值电压时,一旦达到芯片的延时时间便输出复位信号。C1的选择并不严格。然而,它的值应该尽量大——例如0.1到10µF——使C1和内部上拉电阻所得的RC时间常数足够大。这个值确保C1在 引脚上保持了至少1us的低电平。

引脚上保持了至少1us的低电平。

C2充电到Q1的偏置电压后,晶体管仍然导通。在下一次上电或手动按键复位电路时,晶体管C2放电。这个动作一旦发生,Q1关闭。R1将C1的负向充电到供电电压VDD。因为电容C1的正向不能立即改变,其表现为充电到2VDD。然而,保护二极管D1将C1的电压箝位到仅为VDD加上二极管的导通电压。一旦C2充电足够使Q1再次导通时,重复循环。

上一篇:基于DDS的多通道信号源设计

下一篇:如何降低射频功率放大器的功耗方案比较

推荐阅读最新更新时间:2023-10-12 20:42

- 电源情报站 MPS小程序干货推荐,下载有好礼!4月活动开始啦~

- ADI有奖下载活动之7 可编程逻辑控制器(PLCs)解决方案

- 安世半导体&世平集团 高效能&小型化, Nexperia MOSFET的5G解决方案 观看、下载 闯关赢好礼!

- 了解Keithley 4200-SCS参数分析仪,下载技术文章,抽奖赢礼!

- 分享赢开发板:告诉小伙伴,2018年ST全国巡回研讨会开始啦

- 意法半导体工业峰会2019( 深圳 )

- “搜器件”小程序又添新功能!

- 有奖直播|魏德米勒产品在半导体行业的应用 报名中

- DSP-Sitara精品课上线,礼品、开发板等你拿!

- 有奖直播:市场环境不确定,为物联网设备保驾护航英飞凌很确定

电气控制与S7-1200_PLC应用技术

电气控制与S7-1200_PLC应用技术 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号