2012年4月底,随着英特尔发布新一代的ivy bridge芯片组的原生支持USB3.0,更让USB3.0走下神坛。成本的降低让消费者买得起、用得起,普及性大为提升。另外,业界龙头微软将于2012年推出全新的Windows 8,其中装载USB3.0原生驱动程序,这使得USB3.0主控芯片的使用者将获得更好的兼容性,也带动计算机、芯片供应商大规模部署USB 3.0相关产品。尤其是USB 3.0接口大幅了提升USB 2.0接口的效能瓶颈,利用PCIe技术重新取得外部高速接口的规格优势,加上多埠支持的Host芯片技术日益成熟,将在PC和笔记本中大量装载,吸引更多厂商支持USB 3.0高速接口,USB3.0接口将迎来全面普及时代。

目前,市场上各种USB3.0规格的电子产品及外设众多,USB3.0最大传输带宽高达4.8Gbps,传输速度比USB 2.0提升10倍,其最大优点在于USB 3.0保留了即插即用功能并可充当供电来源,且能与USB 2.0兼容,除了为厂商带来更多利润外,也让使用者能够方便升级,并享受其创新功能。除了台式计算机和笔记本电脑等主机端,USB3.0还将应用于各种计算机外部设备,包括U盘、外接式硬盘等。据研究机构IDC的预测,到2015年,USB3.0出货量将加速倍增至23亿,其中50%将应用在存储功能上,这部分市场规模将达到400亿元。业界认为2012年第二季PC与笔记本装载多埠USB 3.0高速接口的比例将大幅增加,其原因一方面是USB 3.0多埠Host芯片解决方案成本持续压低,另一方面则是USB 3.0的外围产品也不再局限于外接硬盘、U盘等产品,预计将会有移动电话、平板电脑、数码相机等推出。

高性能USB3.0物理层IP

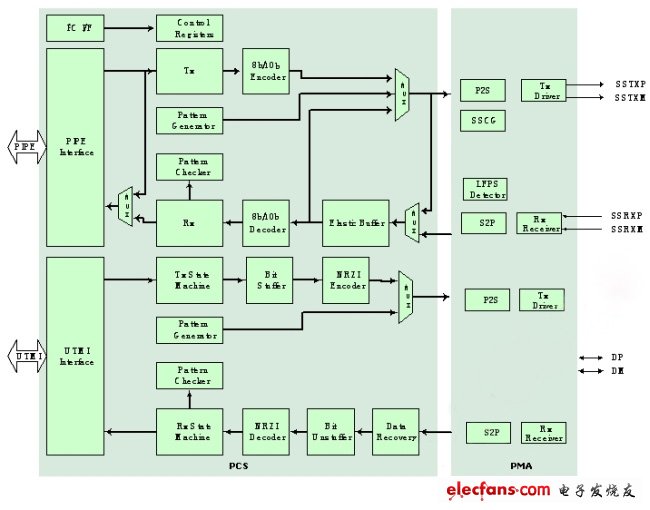

智原科技在USB3.0物理层IP的第一个产品就是2008年8月USB-IF协会在Intel举办的IDF上展出的全球第一个USB3.0原型。如图1所示,USB3.0 物理层IP主要包含二大部分:PMA(Physical Medium Attachment Sublayer)和PCS(Physical Coding Sublayer)。

图1:USB3.0 物理层IP主要包含PMA和PCS。

PCS部分主要是进行自动协商(Auto negotiation)及8b/10b编码及解码。自动协商通过两个连接的设备选择常见的传输参数,如速度和流量控制,在这个过程中,所连接的设备首先先各自以自已的最高速传输,再协商找出二边都能支持的最高速作为传输模式。决定传输模式后,PCS即对被传送和接受的信息编码和解码,目的是使接收器更容易恢复信号。

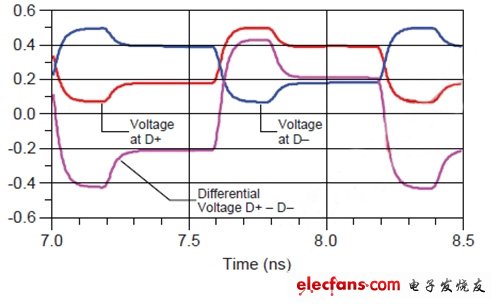

PMA部分主要处理模拟的高速信号,该信号速度高达5Gbps。在传输线方面,USB3.0支持长达3米的四线差分信号线及11英寸PCB。如图2所示,5Gbps信号在长线缆上采用的是差分信号方式传输,从而避免信号被干扰及减少电磁干扰(EMI)问题。PMA电路分为以下六个主要模块。

图2:5Gbps信号采用差分传输可以减少电磁干扰。

并串联(P2S,Parallel to Serial):将较低速的并行信号转成高速的串行信号。

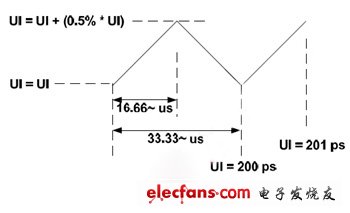

展频频率产生器(SSCG,Spread Spectrum Clock Generator):如图3所示,在5Gbps的传输速度下往低速进行三角展频。这一展频的动作可使信号在传输线及PCB的信号传输时减少电磁干扰问题。

图3:5Gb/ps的传输速度往低速做三角展频。

TX Driver:该模块将5Gbps的高速单端信号转换成高速差分信号,并根据USB3.0规格产生3.5dB/6dB去加重(de-emphasis),在TX端口利用3.5dB/6dB去加重来加强高频的能量,避免传输损失使得眼图的开度变小。

低频周期信号侦测器(LFPS Detector,Low Frequency Period Signal Detector):如果链接处于某种闲置状态,则可通过低频周期信号发送低频周期信号(LFPS)进行通信,这种方式的功耗明显低于SuperSpeed信号发送方式。事实上,不管是主机还是设备发送LFPS,都会退出闲置模式。

RX Receiver:该接收器包含均衡器模块和时钟-数据恢复模块。均衡器接收高速5Gbps的高速信号,并对因传输损失的高频能量做补偿,使时钟-数据恢复模块在锁存数据时,眼图拥有较大开度。

串并联(S2P,Serial to Parallel):将接收下来较高速的串行信号转成高速的并行信号。

USB 3.0控制器硬件电路主要处理USB3.0协议的数据与控制路径。接口部分包括两种接口模块:一种是与USB 3.0物理层进行通信的PIPE接口模块,另一种是与SoC芯片内部AHB总线进行通信的AHB总线接口模块,综合结果显示总线速度可以超过266MHz。USB 3.0设备控制器结构如图4所示。USB3.0链路层模块(U3LKL)实现了USB 3.0规范第7章 “Link Layer Specification”所要求的指标,整个模块始终工作在125MHz。

图4:USB 3.0设备控制器结构框图。

模块里包含了链路封包传送仲裁器、链路封包接收器、链路封包提取器、链路有序集接收器、链路字节驱动器、链路扰频/解扰器、链路层训练及状态机等功能模块。其中的链路封包传送仲裁器从“协议层传送封包接口”、“标头重试缓冲”以及“传送链路命令模块”等三个地方选择数据来源。基于“链路层训练及状态机”的状态,8b_driver模块会传送诸如TSEQ、TS1、TS2或一般封包等相应数据。扰频器模块将基于从TS2分析而得到的“链路配置字段”来决定是否传送加扰数据到PIPE接口。

USB 3.0协议层模块(U3PTL)负责处理从链路层模块送入的SS 封包,并且决定适当的反应,再将数据写入BFM,更新与封包EP有关的上下文。协议层模块决定响应的类型,例如NRDY、ERDY、STALL、ACK以及PING_RESPONSE,该模块还要从BFM的IN EP请求数据传输。如果数据准备好了且标头是所期望的,该模块也会将DP封包数据写到BFM 的OUT EP,整个模块同样也工作在125MHz。

USB 3.0电源管理模块(U3PWE)负责处理PowerDown模式以及发送和侦测LFPS信号的类型。基于LTSSM的状态,U3PWE将会依照PIPE的规范来控制PowerDown模式。电源管理模块工作在aux_clk时钟域,该时钟域在cclk和low_power_clk等两个时钟域间切换。在一般模式下,aux_clk就是cclk;在U3/Disabled模式下,aux_clk会被切换到low_power_clk以达到节省功耗的目的。

USB3.0产品的PCB布线设计

为维持USB 3.0 5Gbps超高速信号传输的信号完整性,在PCB设计考虑时,需要确保特性阻抗的匹配,并采取抑制信号衰减的对策。特性阻抗的整合重点是配线幅度与配线间隔的调整以及通孔的设计;而信号衰减控制所涉及的领域,除了USB 3.0物理层传输电路与接收电路的设计之外,还需要注意PCB的设计。

一般消费类产品在进行PCB材料的选择时,基于成本考虑因素会选择普通的FR-4 多层板来设计,PCB 板厂商制造时会有±10%的误差变化。这也是为何需要将差分信号线尽可能靠近的原因。同时,不同的PCB电路板材质会有不同的介电常数,建议在预布线时与PCB板制造商讨论PCB Stack-Up堆栈结构的设计,以符合高速线路阻抗控制条件。在实际设计时,建议可以通过调整走线宽度(Trace Width)来改变Z Diff,不建议调整线距S。通常,PCB线路板供应商会提供线间距(Line-to-Line Spacing)的最小参考。

要设计一个具有USB 3.0差分传输线(Differential Signal)架构的PCB,并符合信号完整性的测试要求,两组差分信号高速信号线SSRX+/-及SSTX+/-的走线必须有良好的对称性与合适的PCB Stack-Up堆栈结构设计。PCB电路板的走线可以采用微带传输线(Microstrip Line)方式来实现,一则阻抗较容易控制,二则可以避免穿过贯孔,造成阻抗不连续。走线布线(Trace Routing)必须考虑走线宽度与PCB电路板介质厚度(H)对于微带传输线特性阻抗的影响。以6层板PCB布局为例:顶层/上层铜泊的高度(t)等于1.7mils时,电路板的介电常数为Er = 4.0,tanδ= 0.023(PCB板FR4材料在高频应用时的典型数值),走线线宽为6mils,线间距为6mils,线路板介质厚度(h)与传输线特性阻抗Z Diff的关系可以参考图5。

图5:线路板介质厚度与传输线特性阻抗的关系。

在差分传输线架构传输下,USB 3.0物理层传输电路的收发器电路的接收端SERDES电路会存在终端阻抗,而差分传输关注的是SSRX+/-及SSTX+/-两组差分信号两端的差分特性阻抗。差分特性阻抗所需的数值就是终端阻抗的两倍。USB 3.0增加了SSRX+/-及SSTX+/-两组差分信号,不同于D+/-这组信号使用带直流准位的信号,SSRX+/-及SSTX+/-都是用电容隔离直流准位之后的交流差分信号。SSRX+/-及SSTX+/-两组差分信号的方向是固定的,不同于D+/-信号采用半双工模式,SSRX+/-及SSTX+/-两组差分信号属于双单工模式。而差分信号可以降低电磁干扰,抗扰性能较好。

USB3.0完整解决方案通过兼容性测试

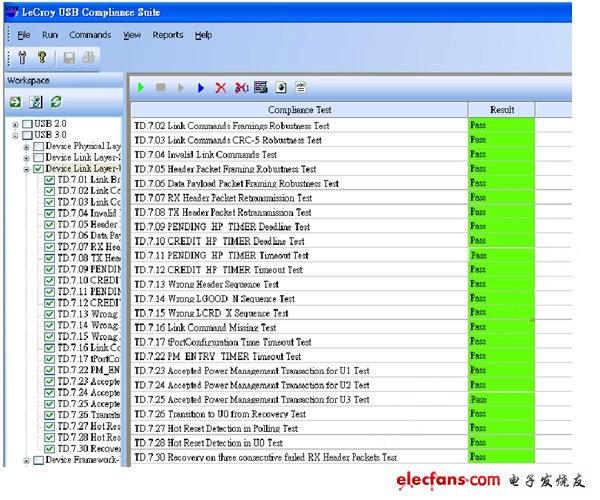

智原科技推出的USB 3.0完整解决方案,能够使不同应用的客户都顺利流片。主要的秘诀在于,智原科技的IP能够完全通过USB-IF兼容认证测试,USB-IF所进行的兼容性测试是为了确保所有使用者都能使用正常运作通过测试的USB设备。测试内容包括电气套件(Electrical Suites)、USB Command Verifier(USB CV)、链路层、Gold tree 等测试。电气套件测试是由仪器厂商的电气套件来检测信号是否符合USB3.0规范;USB CV是Windows的应用程序,用来根据检测规格书中第九章所要求的setup命令来检测设备;USB 3.0链路层测试确保了设计符合USB 3.0的通信协议。Gold tree 测试可以检测设备在Windows环境下的实际表现,确保了在真实情况下的运作不会受其他USB设备的干扰。

智原科技的USB 3.0 IP已在许多客户的产品上获得验证,通过USB兼容测试大会(Compliance Workshop-Plugfests)或测试实验室(PIL)的USB兼容认证测试。如图6所示,客户的产品可以通过安捷伦(Agilent)、泰克(Tektronix)、力科(LeCory)的电性测试解决方案,也能够通过力科(如图7所示)、Ellisys 的链路层测试方案,兼容性测试(Gold tree、CV)上能完全满足NEC、Fresco logic等各家主控芯片厂商的要求。

图6:通过Agilent的电性测试。

图7:通过LeCroy的链路层测试。

本文小结

不少追求高速体验的玩家已感受到了USB 3.0的优势。USB 3.0接口一般实测传输速率约370~390MB/s,大约可以容纳500个频道的DVD画质影音数据流,或100个频道的HD高画质(720×480@60Hz)音视频数据流;即使传递1个未压缩的Full HD高画质电影数据流,也就是1,920×1,080@60Hz的数据流量(相当于每秒190MB的大小),在USB 3.0的传输速度看来也是绰绰有余。面对USB 3.0飞速发展的风潮,我们的日常存储和数码应用也势必会随着电脑等硬件设备升级至USB 3.0而有所提升。USB 3.0成为市场主流已是不可阻挡的大势所趋,智原科技提供的USB3.0完整解决方案将帮助客户更快、更成功地切入市场。

上一篇:恩智浦JESD204A转换器配合高性能SiGeC技术特点

下一篇:通信行业存储解决方案

推荐阅读最新更新时间:2023-10-12 20:45

- 在发送信号链设计中使用差分转单端射频放大器的优势

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 安森美推出业界领先的模拟和混合信号平台

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 国产高精度、高速率ADC芯片,正在崛起

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

【用户手册】带+STM32MP157+MPU+的评估板

【用户手册】带+STM32MP157+MPU+的评估板 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号