正弦信号源在实验室和电子工程设计中有着十分重要的作用,而传统的正弦信号源根据实际需要一般价格昂贵,低频输出时性能不好且不便于自动调节,工程实用性较差。本文的设计以较低的成本制作正弦信号发生器,可用作核磁共振中引发磁场测量仪的激励一般的正弦信号,也可作为调制用的教学演示信号源。

正弦信号发生器主要由两部分组成:正弦波信号发生器和产生调幅、调频、键控信号。正弦波信号发生器采用直接数字频率合成DDS技术,在CPLD上实现正弦信号查找表和地址扫描,经D/A输出可得到正弦信号。具有频率稳定度高,频率范围宽,容易实现频率步进100 Hz。全数字化结构便于集成,输出相位连续,频率、相位和幅度均可实现程控。

调幅、调频、键控信号的产生可采用调频、调幅专用芯片能分剐实现,但是该方法实现的调频调幅功能,对于某一特定频率和特定的调制度、频偏效果较好,在载波频率可变和调制度、频偏要求任意设定的情况下难以实现。本文利用CPLD和单片机AT89S52不仅可以实现频率范围可调的正弦波信号,而且在CPLD内部加上相应的数字控制算法就能方便地实现调频FM,调幅AM和键控PSK、ASK数字调制功能有利于提高系统的整体性能和工作可靠性。正弦信号产生部分可在一片CPLD(EP1K30)中实现,大大地简化了硬件电路,便于功能扩展,并为进一步实现系统集成创造了条件。

1 理论分析与计算

1.1 正弦波形的产生

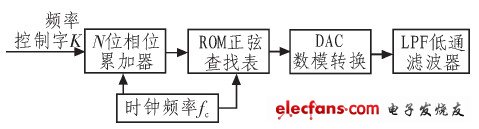

单向DDS由Nbit相位累加器和ROM只读存储器(正弦查找表)构成的数控振荡源(NCO),数模转换器(DAC)、低通平滑滤波器(LPF)构成,图1所示为DDS的基本结构。

图1中fc为时钟频率,K为频率控制字,N为相位累加器的字长,M为ROM地址线位数,L为ROM数据线宽度,fo为输出频率。相位累加器由全加器和累加寄存器级联组成。在时钟频率fc的控制下,对输入频率控制字K进行累加,累加满量时就产生溢出。相位累加器的输出对应于该时刻合成周期信号的相位,并且这个相位是周期性的,在0~2π范围内变化。相位累加器位数为N,最大输出为2N-1,对应于2π的相位,累加1次就输出1个相应的相位码,地址以查表方式,得到对应相位的信号幅度值,经过数模转换,就可以得到一定频率的信号输出波形,低通滤波器对输出的信号波形进行平滑处理,滤除杂波和谐波。由于控制字K经过2N/K次累加,相位累加器满量溢出,完成1个周期运算,所以输出频率fo由fc和K共同决定,即fo=fcK/2N且K《2N-1,得到DDS的最小分辨率可达fc/2N。理论上通过设定DDS相位累加器的位数N、频率控制字K和时钟频率fc的值,就可以产生任一频率的输出。根据频率步进100Hz的要求,选取累加器的位数为19位,计算出时钟频率fc应为52.4288 MHz。步进的累计误差通过软件补偿的方法进行修正,利用现有的52.416 0 MHz晶振完全精确地实现步进100 Hz的要求。

图1 基于DDS的正弦信号发生器的原理图

1.2 产生模拟幅度调制信号

用调制信号去控制高频振荡的幅度,使其幅度的变化量随调制信号成正比地变化,这一过程称为幅度调制。若载波为uc=Uc cosωct,调制信号为f(t)=cosΩt,则调幅波为

![]()

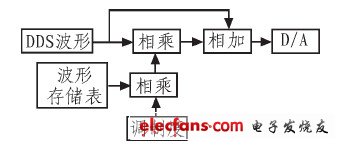

普通调幅波利用模拟相乘器实现,但是外围电路复杂,改变调制度需改变电路元件的参数,实现起来繁琐。可以采用CPLD芯片结合DDS技术灵活的实现数字调幅,原理如图2所示。

图2 幅度调制原理图

由DDS产生的波形信号作为载波,在单片机内部作调制信号为1 kHz的正弦波形存储表,根据键盘所设定的调制度ma(10%~100%)与存储表中的数据相乘的结果送CPLD与DDS得到的波形相乘,再与DDS信号相加就产生相应的数字调幅波编码,经D/A转换得到模拟调幅信号。

1.3 产生模拟频率调制信号

在连续波调制中,载波可表示为uc=Uc cosωct,调制信号为UΩ(t),调频波是瞬时频率的变化量与调制信号成正比,因此调频波的瞬时角频率除了载波角频率ωc外,还附加一项和调制信号成正比的部分,式中kf为比例系数,是单位调制信号强度引起的频率变化。△ωf(t)的最大值△ωf称为最大频偏,反映在频率上为f(t)=fc+△fcos(2πft),调频波的表达式:

![]()

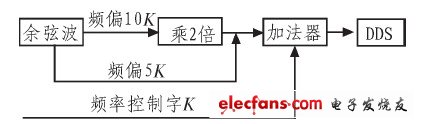

图3为CPLD数字调频电路,频偏为5 K时的控制字是50,将余弦波形与50相乘,并与单片机传递的频率控制字相加,送入DDS模块经D/A转换就可以输出调频波,其设计原理图如图4所示。

图3 CPLD数字调频电路图

图4 频率调制设计原理图

1.4 产生二进制PSK、ASK信号

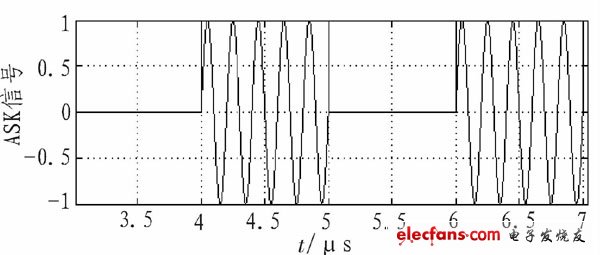

用数字基带信号去控制高频正弦波的幅度就是振幅键控调制ASK。在CPLD内部只需要根据所设定的二进制基带序列码对产生的DDS波形进行处理,二进制基带序列为1时波形通过,序列为0时输出0,仿真波形如图5所示。

图5 二进制ASK仿真波形图

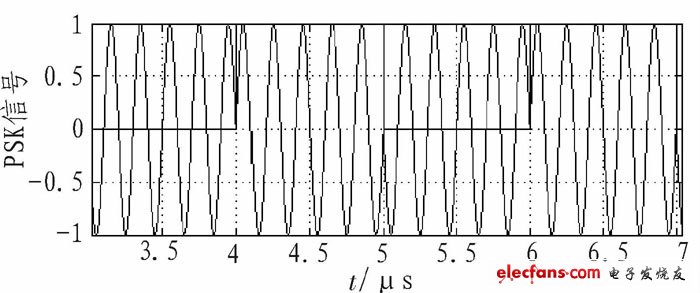

移相键控PSK是数字基带信号去控制载波的相位。它是利用载波不同相位或相位变化来传递信息的。PSK的实现方法是根据数字基带信号的两个电平(或符号)使载波相位在两个不同的数值之间切换,两个载波相位通常相差180°。波形如图6所示。

图6 二进制PSK仿真波形图

1.5 输出信号调理部分

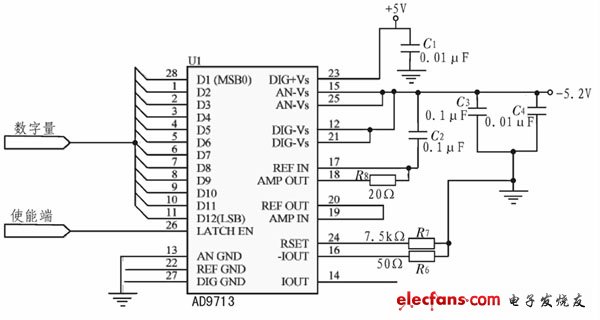

D/A转换电路如图7所示,选用的是12位高速D/A器件AD9713,该器件具有更好的静态性能和动态特性。AD9713B更新速率可达100MS/ s。由于该D/A转换器是针对DDS、波形重构和高质量图像信号处理等应用而设计的,这款芯片在动态特性方面表现特别突出,并且具有优良的谐波抑制能力。AD9713输出满量程电流输出是由VCONTROLAMP IN和RSET决定的,图7中AD9713采用内部参考电压,输出满量程电流为-20 mA。

图7 D/A转换电路

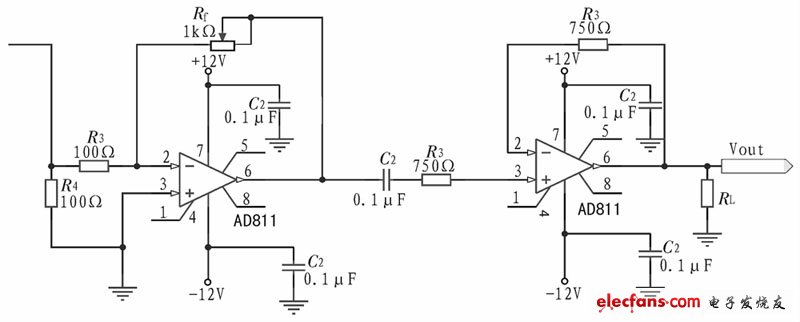

幅度调节电路是由放大器组成。高频信号放大要求放大器有足够的输出电压转换速率,在正弦波的情况下,放大器所需要的最大摆率SR=2πω=2πAf,其中ω为信号的角频率,A为信号幅度,f为频率。此外,幅度调节电路要求带低阻负载,放大器的电流输出能力也是个重要参数,要在50 Ω负载上输出6 V信号,则放大器至少要有120 mA的连续电流输出能力。考虑以上原因,本文选择AD公司的高速运放AD811作为输出放大器,它是一个宽带高速电流反馈型运算放大器,其各项参数非常适合上述指标:小信号带宽(G=+2时)达120 MHz,电压摆率SR为2 500 V/μs,全谐波失真THD为-74 dB(10 MHz),输出电流达100 mA,其短路输出电流可达150mA。

幅度调节电路如图8所示,图中R3和R4起分流作用,限制用于I/V转换的电流,1个电流反馈的高速放大电路。它把AD9713输出的电流转换成电压,通过反馈电阻Rf的电流决定AD811输出的幅度为6 V。为了增大后级的带负载能力设计了后级电压跟随,模拟输出的最后部分是滤波电路,滤波器的选择主要取决于系统所要输出的波形,在50 Ω的负载电阻上的电压峰峰值为6±1 V。

图8 幅度调节电路

1.6 频率值的接收与显示

键盘、显示部分用来实现用户与单片机的交互。系统采用中断查询的方式接收通过键盘输入的频率值。该频率值一方面送到数码显示接口进行显示,另一方面转化成频率控制字送往相位累加模块。

2 系统软件设计

单片机程序采用C语言,在Keil uV2环境下编译,用WAVE6000L仿真器调试CPLD在MAXPLUSⅡ下开发,采用VHDL语言编程。

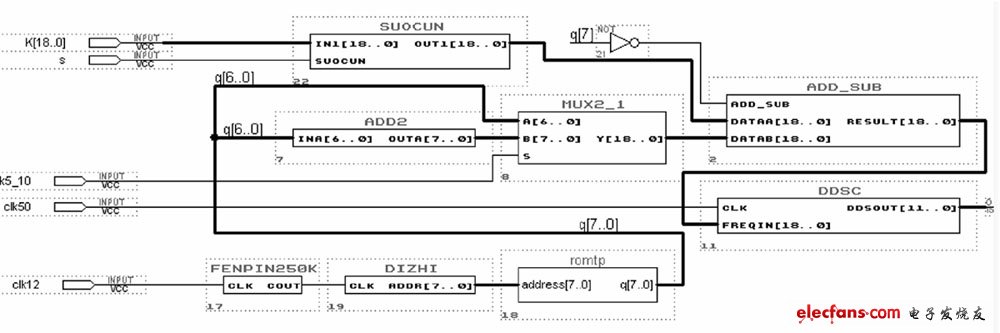

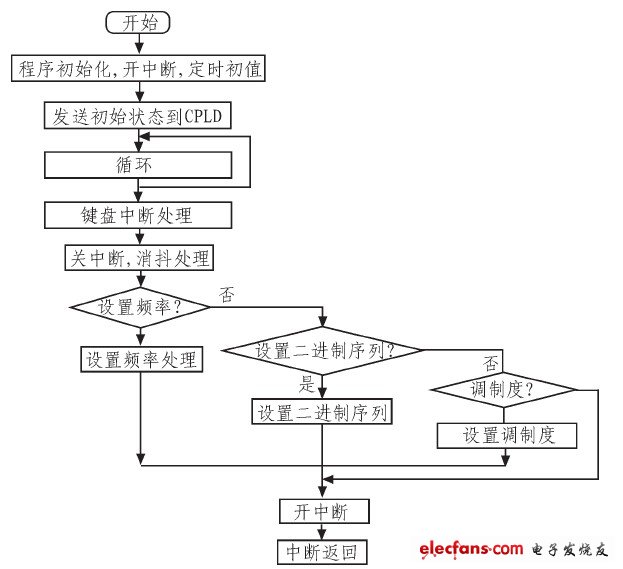

关于CPLD部分,相位测量仪和数字移相信号发生器采用ALTERA公司的EP1K30TC144-3FPGA芯片,原理图已经在前面的分析中。关于单片机部分,程序流程图如图9所示。

图9 程序流程图

3 功能及指标测试

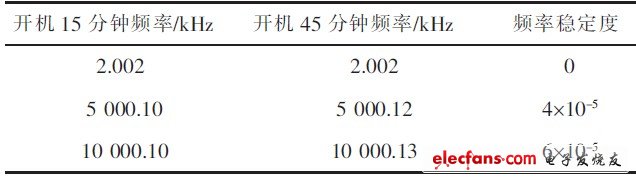

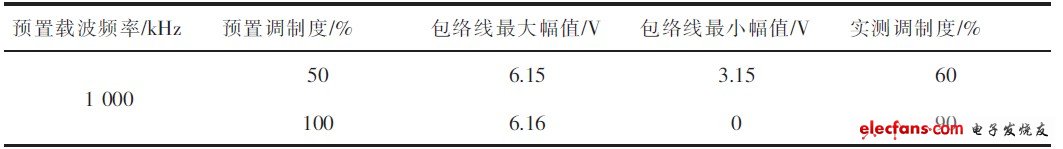

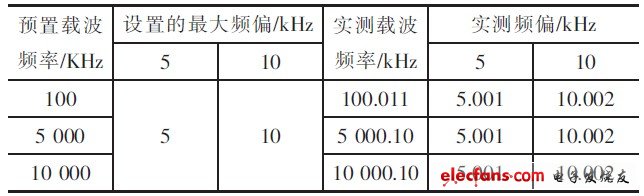

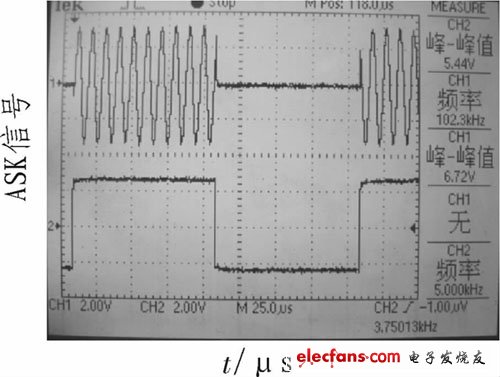

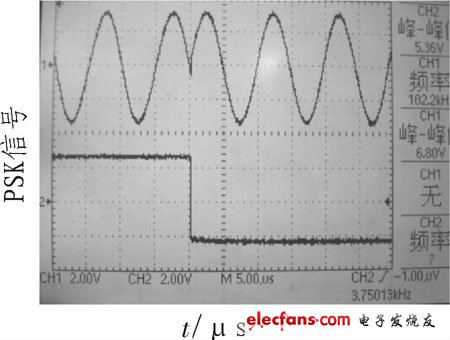

利用测试仪器:EE1641B1型函数信号发生器/计数器,直流稳压电源GPS-3303C、60 MHz示波器TDS1002,高频测试仪等对设计的信号发生器进行性能测试。正弦波的频率范围、步进、在50 Ω负载上的输出电压幅度,失真度测量如表1所示,频率稳定度测量如表2所示,步进为10%的幅度调制测试如表3所示,调制信号为1 kHz的频率调制测试如图10所示,二进制PSK、ASK如图11和图12所示。

表1 正弦波实验观察结果

表2 正弦波频率稳定度测试结果

表3 正弦波幅度调制测试结果

图10 正弦波频率调制测试结果

图11 ASK信号测试图

图12 PSK信号测试图

经过测试可以得到,本文设计的系统可达以下性能指标:

1)正弦波输出频率范围 1 kHz~10 MHz。

2)具有频率设置功能,频率步进100 Hz。

3)输出信号频率稳定度优于10-4。

4)输出电压幅度在50 Ω负载电阻上的电压峰-峰值Vopp≥1 V。

5)失真度用示波器观察时无明显失真。

综合分析各项指标的测试结果发现,该设计频率变化范围大,信号稳定度高,失真度好,达到了性能良好的设计要求。

4 结论

以CPLD和单片机AT89S52为基础,采用DDS技术实现的正弦信号发生器在保证输出稳定的正弦波频率情况下能够实现频率可调,失真度小,频率步进小,精确度高等特点,产生的正弦信号源可以广泛运用于教学或一般工业以及实验场合,测试结果表明本文提出的正弦信号发生器的设计是有效的,易于工程实现且具有一定的实用性。

上一篇:基于CPLD和AD9857的数字化多模式调制单元设计

下一篇:基于DSP的CPLD软件更新方案研究

推荐阅读最新更新时间:2023-10-12 20:46

- 在发送信号链设计中使用差分转单端射频放大器的优势

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 安森美推出业界领先的模拟和混合信号平台

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 国产高精度、高速率ADC芯片,正在崛起

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

电气控制与西门子S7-300PLC编程技术

电气控制与西门子S7-300PLC编程技术 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号