4.2 软件实现

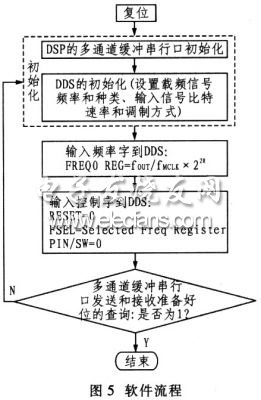

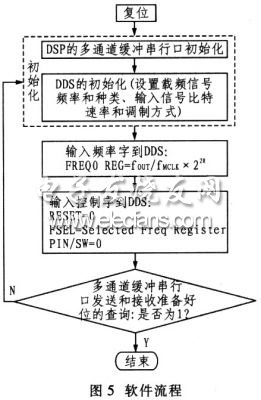

软件的流程如图5所示,主要包括复位、初始化、写频率字和控制字等部分。

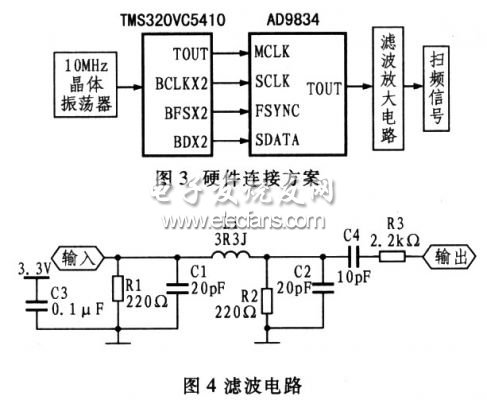

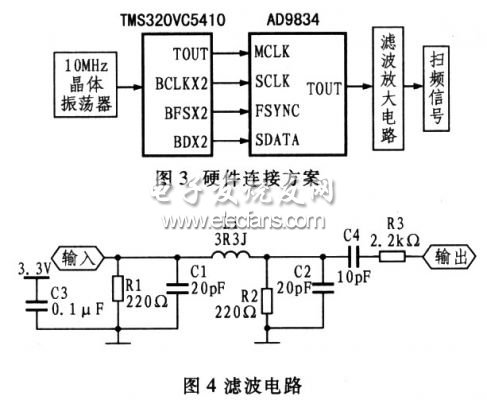

初始化部分包括对DSP多通道缓冲串行口的初始化及其配置和对AD9834写入控制字,应设置多通道缓冲串行口工作模式和DDS的SLEEP、RE-SET、SIGNPIB、HLB等位。在该系统设计中,AD9834采用串行控制比特位方式选择相位、频率寄存器;PIN/SW=0.选择控制字模式;FSEI=0,选择使用频率寄存器0(FREQ0);D13=0,将28位的频率寄存器分成2个14位的寄存器工作,且频率字的高14位和低14位可以独立改变。由于系统要求在上电后立即工作,故将AD9834的RESET引脚接低电平。必要时,也可以由系统中的其他模块如CPID控制DDS启动。SDATA、SCLK和FSYNC 3个引脚向AD9834中写数据和控制字。当FSYNC=0时,表示正向AD9834写入1个新字,并将在下1个SCL.K的下降沿读人第1位,其余的位在随后的SCLK的下降沿读入,经过16个SCLK下降沿后,置 FSYNC=1,实现了DSP对AD9834的控制。

由于将C5410的McBSP配置为时钟停止模式,串口接收控制寄存器SPCRl的时钟停止模式位cLKSTP和串口引脚控制寄存器PCR的发送时钟极性位CLKXP配置为CLKSTP=11,CLKXP=1(时钟开始于下降沿,有延时),因此,发送时钟模式引脚设为内部时钟输出(BCLKX=I);采样率发生器时钟源来自CPU时钟(CLKSM=I);发送帧同步模式引脚设置为输出(FSXM=1);发送帧同步极性引脚设置为低电平有效(FSXP=1);发送时钟极性设置为下降沿采样 (CLKXP=1);数据发送和接收延时时间为l位(RDATDLY=XDATDLY=01b);采样率发生器时钟的降频因子为49(CLKGDV=49)。因为16xbaud rateCLKOUT/1+CLKGDV为100/49,所以MCBSP的采样率发生器产生2MHz的时钟信号。

下面是通过McBSP口向AD9834传送频率为8.2MHz的频率字和控制字的程序段: L

程序设计中应该注意的重点就是对发送和接收准备好位的查询,如果在程序中没有查询或者查询的地点不对,则程序在单步运行时可能会正确发送和接收数据,但是当全速运行时,由于速度较高,因而不能进行正确的数据收发。正确的查询应该是在数据发送前查询SPCRl或SPCR2中的RRDY位或XRDY位,当RRDY位或XRDY位为0时,表明尚未接收或发送完数据,一直查询到RRDY位或XRDY位为1,表明上一组数据已接收或发送完毕,可以进行下一组数据的接收或发送。

5 结束语

由DDS技术产生的扫频信号源不仅频率稳定、信号精度高、抗干扰能力强,而且由于它是在计算机控制下直接实现的,因而易于实现智能化处理。在频率迅速变化的场合,DDS中寄存器更新的速度有时会成为关键指标,这时必须使用高速电路和高速串行口,由合理的硬件设计和软件流程来实现预期设计目标。

关键字:DSP EAS扫频 信号源

编辑:神话 引用地址:DSP实现EAS扫频信号源设计

推荐阅读最新更新时间:2023-10-12 20:49

ADSP系列数字信号处理器件的应用

摘要: ADSP是AD公司生产的浮点式DSP系列产品,文中对几种ADSP系列产品的特点作了综合描述,指出了它们各自系列的特性和数据处理能力。最后给出了ADSP系列产品应用于数字滤波器的实现方法和程序。

关键词: 超哈佛结构

ADSP 多功能指令 自动缓冲 数字滤波器

DSP(Digital Signal Processing)芯片也称数字信号处理器,它是一种特别适合于进行数字信号处理运算的微处理器,其主要特点是能够实时快速地实现各种数字信号处理算法。自1980年以来,DSP芯片得到了突飞猛进的发展,现在DSP芯片的应用越来越广泛。美国模拟器件公司(Analog

Devisce

[嵌入式]

基于MATLAB/SIMULINK的心电信号源系统设计

心电信号主要频率范围为0.05"100Hz,幅度约为0"4mV,信号十分微弱。由于心电信号中通常混杂有其它生物信号,加之体外以500Hz工频为主的电磁场干扰,使得心电噪声背景较强,测量条件比较复杂,为医学研究、救治和教学带来一定困难。本文通过对心电信号的特征分析,提出了基于MATLAB/SIMULINK的 心电信号 仿真方法,采用快速原型技术通过输入/输出卡,将虚拟仿真信号转化生成实际的物理电信号,并与实际硬件电路连接起来,构成心电信号的半实物仿真模型。

基本原理

心电信号

一个典型的心电信号如图1示,它由P波、Q波、R波、S波和T波组成,在诊断过程中可以根据这些特征波的间隔幅值以及P-R间隔、S

[工业控制]

基于DSP的电力线载波OFDM调制解调器

摘要:提出一种基于OFDM的电力线宽带高速通信系统的实现方案讨论了OFDM应用于电力线载波通信的原理,探讨了通信系统调制解调部分的硬件实现和软件流程,并对其关键的FFT算法进行了优化。

关键词:电力线载波 DSP OFDM FFT

利用电力线作为信道进行通信是解决“最后一公里”问题的一个很好的方法。然而电力线作为通信信道,存在着高噪声、多径效应和衰落的特点。OFDM技术能够在抗多径干扰、信号衰减的同时保持较高的数据传输速率,在具体实现中还能够利用离散傅立叶变换简化调制解调模块的复杂度,因此它在电力线高速通信系统中的应用有着非常乐观的前景。文中给出一种基于正交频分复用技术(OFDM技术)的调制解调器的设计方案。

1 OFD

[嵌入式]

探讨基于DSP数字摄像机技术发展

作为DSP领先者的美国德州仪器公司(TI)在数字照相机应用方面同样独占鳌头。首先基于TMS320C54x通用平台上实现影像压缩,然后将影像前端处理的分立器件集成为一个专用芯片,进而把两者合二为一并集成ARM7通用处理器,就是TMS320DSC2x系列通用数字相机平台。这是TI为业界首创的单片影像处理体系架构(SOC),之后又不断提升该平台的性能和功能,并成功推进更新换代。

与此同时,在通用DSP上实现数字网络摄像机的尝试始终没有停止,而真正的突破在与TI的DSP专家采用C6211实现的MJPEG实时处理系统。虽然外围还需要不少分立的期间,但是依赖于C6x高速并行处理能力,其视频性能在业界处于优异的水平。而其功能已经可

[嵌入式]

基于MATLAB/SIMULINK的心电信号源系统设计

心电信号主要频率范围为0.05“100Hz,幅度约为0”4mV,信号十分微弱。由于心电信号中通常混杂有其它生物信号,加之体外以500Hz工频为主的电磁场干扰,使得心电噪声背景较强, 测量 条件比较复杂,为医学研究、救治和教学带来一定困难。本文通过对心电信号的特征分析,提出了基于MATLAB/SIMULINK的心电信号仿真方法,采用快速原型技术通过输入/输出卡,将虚拟仿真信号转化生成实际的物理电信号,并与实际硬件电路连接起来,构成心电信号的半实物仿真模型。

基本原理

心电信号

一个典型的心电信号如图1示,它由P波、Q波、R波、S波和T波组成,在诊断过程中可以根据这些特征波的间隔幅值以及P-R间隔、S

[医疗电子]

Altera 20nm FPGA:创新的3D集成、收发器与可变精度DSP

近期,Altera CTO Misha Burich时隔5个月再度访华,带来了最新Altera基于20nm的关键消息。

创新的3D集成

和赛灵思不同的是,Altera在28nm时代并没有宣传3D或者2.5D技术,因此原本在代工厂上与TSMC合作更长时间的Altera并没有在创新工艺上占据先机。

所以在下一代20nm FPGA 上,Altera必须占据先机。

Misha Burich表示,“20nm 3D IC工艺可以把不同的die放在同样的一个硅晶圆上,实现异构的FPGA,比如在FPGA上加上光模块,HardCopy ASIC或者其他存储器等,从而实现不同类的产品。”

谈到两家3D技术的区别

[嵌入式]

HPI在MCU和DSP接口中的应用

描述HP I接口的工作原理及C8051F060和TMS320VC5409 (简称C5409)之间的接口电路设计,给出了 HP I 接口的软件设计。该系统具有设计灵活、数据传输速度快、适用于其他含有HP I接口的DSP应用系统,为开发人员提供了一种便捷稳定的数据共享、传输方式。

1 TMS320VC5409的HPI - 8接口

C5409的HP I - 8是一个增强型8位HP I8接口,主要用来与主处理器接口。C5409 内部有32K的RAM空间,除了DSP本身可以访问该RAM区域外,主机也可以通过HP I口实现对整个RAM的访问,从而实现主机与DSP的通信。HPI - 8接口通过HP I控制寄存器HP IC、地址寄存

[嵌入式]

集成工具提高嵌入式DSP系统设计与自动化程度

嵌入式 DSP 系统传统设计流程通常由概念到算法及算法到产品两个阶段构成,通常这两个阶段互相独立且由不同设计小组完成。 传统的设计流程里要用手工在两个阶段之间进行转换与衔接,这样容易出现错误而推迟产品的上市时间。本文介绍一种集成工具可以使设计与验证测试更加自动化,且具有更高效率,可减少产品缺陷。 过去几年以来,产品与系统在软件方面的功能不断增强,高强度实时要求越来越多。对设计工程师而言,为与竞争对手展开竞赛,争取更快将新产品投向市场,高效系统开发方法成为重中之重,对开发数字信号处理器算法的工程师而言尤为如此。此外,产品开发周期和生命周期不断缩短等因素,也促使工程师和设计经理对开发方法和软件工具进程进行全面重新评估。 产品漏洞会导致

[电源管理]

零点起步——TMS320C6000系列DSP原理与应用系统设计

零点起步——TMS320C6000系列DSP原理与应用系统设计

京公网安备 11010802033920号

京公网安备 11010802033920号