异步复位相比同步复位:

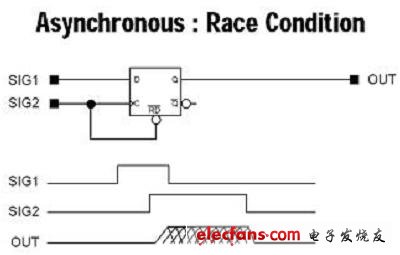

1. 通常情况下(已知复位信号与时钟的关系),最大的缺点在于异步复位导致设计变成了异步时序电路,如果复位信号出现毛刺,将会导致触发器的误动作,影响设计的稳定性。

2. 同时,如果复位信号与时钟关系不确定,将会导致亚稳态情况的出现。下面先给出一个例子,然后就亚稳态进行重点讨论。

亚稳态的定义(说明):

在 Howard Johnson 的《High Speed Digital Design: A Handbook of Black Magic》一书中,专门就逻辑电路的亚稳态作了专门的分析。由于 timing margine 不够,电路的输入没有能够上到所需要的逻辑电平高度,导致逻辑器内部不得不花费额外的时间使得输出达到所需的稳定逻辑状态,这个额外的时间,我们也叫作决断时间(resolution time)。在 Johnson举的例子里,逻辑器件的逻辑电平是用电容来维持的,如果时序不够,就好像给电容充电不足。

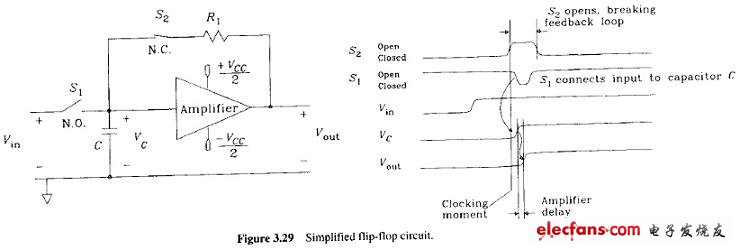

Howard Johnson 在书中(P123 页-3.11.2)用一个 flip-flop 的例子来说明亚稳态(metastable behavior)。

书中用一个 amplifier,两个 switch,一个电容来模拟 flip-flop 的工作状态。电容用来保存电路的逻辑电平,两个 switch 状态的改变可以模拟数据的输入和 flip-flop 的工作状态。在flip-flop开始翻转之前,输入数据的逻辑电平存储在电容里,然后flip-flop通过一个switch S1断开与输入端的连接,同时通过 amplifier(带有一个正反馈环)开始进行内部的翻转机制。

从输入端 switch S1断开,和正反馈环上的 switch S2闭合开始,amplifier 就处于一个幂指数形式的中间态,或者说是不稳定态(形象地说就是“工作中”),可以用如下式子表达:

V(out)=V(in)exp[kt]。

其中 V(in)表示输入逻辑的电平,V(out)表示输出的逻辑电平。k 是一个时间常数,它和 amplifier 的带宽以及正反馈环路有关。

我们看到,如果 flip-flop 在用电容对输入电压采样的时间过短,也就是所谓的时序不够,就会导致 V(in)的值很小,对于 flip-flop 就需要花很长的时间使得输出逻辑 V(out)达到标准电平,也就是说电路处于中间态的时间变长,使得电路“反应”变迟钝。这就是我们所说的“亚稳态”。

从 Johnoson 的一系列试验可以看出,随着 timing margine 不足程度的加深,逻辑电路“反应”会越来越慢,当超过一定的极限时候,逻辑电路就没有输出。

可以说,电路亚稳态的存在,会给时序设计带来很多连锁反应。因此 ,对于高速逻辑电路的设计,充分的 timing margine 是必需的。

亚稳态在设计中的问题分析

1. 亚稳态与设计可靠性

设计数字电路时大家都知道同步是非常重要的,特别当要输入一个信号到一个同步电路中,但是该信号由另一个时钟驱动时,这是要在接口处采取一些措施,使输入的异步信号同步化,否则电路将无法正常工作,因为输入端很可能出现亚稳态(Metastability),导致采样错误。这里我们对亚稳态的起因、危害、对可靠性的影响和消除仿真做一些介绍。

2. 亚稳态发生的原因

在同步系统中,如果触发器的 setup time / hold time 不满足,就可能产生亚稳态,此时触发器输出端 Q 在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里 Q 端会出现毛刺、振荡、或固定在某一电压值,而不一定等于数据输入端 D 的值。这段之间称为决断时间(resolution time)。经过 resolution time 之后 Q端将稳定到 0 或1上,但是究竟是0 还是 1,这是随机的,与输入没有必然的关系。亚稳态实质是介于”0””1”电平之间的一个状态。亚稳态是 FF的一个固有特性。正常采样也会有一个亚稳态时间。当建立保持时间满足时,FF 在经历采样、亚稳态后,进入一个正确的状态。如果建立保持时间不满足,那么FF会有一个相当长的亚稳态时间,最后随机进入一个固定态。

3. 亚稳态的危害

由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出 0~1 之间的中间电压值还会使下一级产生亚稳态,即导致 meta. stability的传播。逻辑误判(由于组合逻辑的 race,导致总线状态的不稳定)有可能通过电路的特殊设计减轻危害(如异步 FIFO中 Gray码计数器的作用,一次只变化一位),而亚稳态的传播则扩大了故障面,难以处理。

4. 亚稳态的简单解决办法

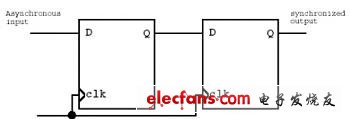

只要系统中有异步元件,亚稳态就是无法避免的,因此设计的电路首先要减少亚稳态导致错误的发生,其次要使系统对产生的错误不敏感。前者要靠同步来实现,而后者根据不同的设计应用有不同的处理办法。用同步来减少亚稳态发生机会的典型电路如图 1 所示。

图 1 两级同步化电路

在图 1 中,左边为异步输入端,经过两级触发器同步,在右边的输出将是同步的,而且该输出基本不存在亚稳态。其原理是即使第一个触发器的输出端存在亚稳态,经过一个 CLK 周期后,第二个触发器 D 端的电平仍未稳定的概率非常小,因此第二个触发器 Q 端基本不会产生亚稳态。

注意,这里说的是“基本”,也就是无法“根除”,那么如果第二个触发器 Q出现了亚稳态会有什么后果呢?后果的严重程度是由你的设计决定的,如果系统对产生的错误不敏感,那么系统可能正常工作,或者经过短暂的异常之后可以恢复正常工作,例如设计异步 FIFO时使用格雷码计数器当读写地址的指针就是处于这方面的考虑。如果设计上没有考虑如何降低系统对亚稳态的敏感程度,那么一旦出现亚稳态,系统可能就崩溃了。

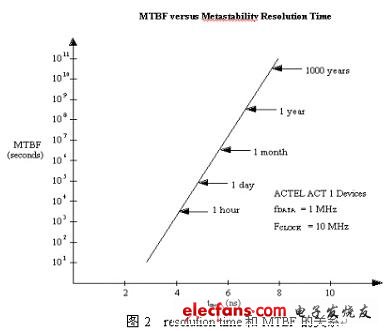

5. 亚稳态与系统可靠性

使用同步电路以后,亚稳态仍然有发生的可能,与此相连的是平均故障间隔时间MTBF(mean time between failure),亚稳态的发生概率与时钟频率无关,但是 MTBF与时钟有密切关系。 有文章提供了一个例子,某一系统在 20MHz 时钟下工作时,MTBF约为 50年,但是时钟频率提高到 40MHz 时,MTBF 只有 1 分钟!可见降低时钟频率可以大大减小亚稳态导致系统错误的出现,其原因在于,时钟周期如果尽可能的大于 resolution time 可减小亚稳态传递到下一级的机会,提高系统的 MTBF,如图 2 所示。

6. 总结

亚稳态与设计可靠性有非常密切的关系,当前对很多设计来说,实现需要的功能并不困难,难的是提高系统的稳定性、可靠性,较小亚稳态发生的概率,并降低系统对亚稳态错误的敏感程度可以提高系统的可靠性。

上一篇:平行缝焊用盖板可靠性研究

下一篇:稳健设计采用Saber仿真器提高系统可靠性

推荐阅读最新更新时间:2023-10-12 20:54

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

电气控制与S7-1200_PLC应用技术

电气控制与S7-1200_PLC应用技术 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号