嵌入式技术被广泛应用于信息家器、消费电子、交换机以及机器人等产品中,与通用计算机技术不同,嵌入式系统中计算机被置于应用环境内部特征不明显。系统对性能、体积、以及时间等有较高的要求。复杂的嵌入式系统面向特定应用环境,必须支持硬、软件裁减,适应系统对功能、成本以及功耗等要求。

0.1 嵌入式系统与协同性

从信息传递的电特性过程分析,嵌入式系统特征表现为,计算机技术与电子技术紧密结合,难以分清特定的物理外观和功能,处理器与外设、存储器等之间的信息交换主要以电平信号的形式在IC 间直接进行。

从嵌入深度ED来看,信息交换在IC 间越直接、越多,嵌入深度就越大。

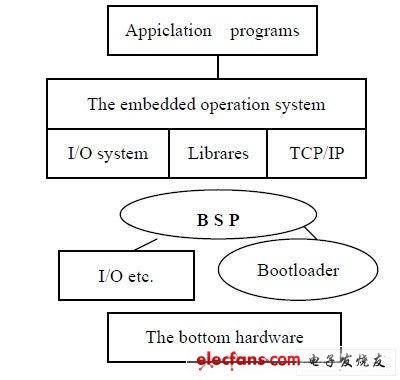

在设计实验系统模型(图1)时,充分考虑到软硬协同性,使其成为一个实验与研究完备平台。软硬件协同性问题涉及到协同性划分技术和协同性设计技术。协同性核心问题之一将涉及启动加载软件Bootloader、系统板级支持包BSP 以及嵌入式OS 之间融合和移植。协同性设计技术与系统功能、性能以及开发人员等因素相关,其核心内容为软硬件的协同描述、验证和综合提供一种集成环境。

图 1. 嵌入式系统结构模型

0.2 没有操作系统OS 的嵌入式系统

0.2.1 系统特点

由于系统的性质、任务、成本等原因,没有操作系统支持的嵌入式系统将继续大量存在。这样的系统使用专用开发工具(如:仿真在线调试器ICE 等)。通过串口或并口在PC机上联机调试程序,具有源代码调试功能。

0.2.2 局限性分析

没有OS 的系统按照“指令顺序执行+中断”的模式运行。在作者参与的早期程控交换机系统设计中,需要对不同端口量级(从10 到1000 等)的分机进行实时处理。通过建立交换系统核心硬件层(存储体、第一层I/O 等)以及用户口地址等程序;然后建立定时和非定时事件、过程以及任务中断链和任务表,应用中断对任务以及过程调度。设计人员要完成相当于部分操作系统功能的编写,导致软件结构复杂、工作量大尤其是重复劳动。

0.3 具有OS 的嵌入式系统

图1 的2 嵌入式系统就是具有嵌入式OS 的一种结构模型。引入嵌入式OS 可以面对多种嵌入式处理器环境(如:MPU、DSP、SOC 等)提供类同的API 接口,使基于OS 上的程序具有较好的移植性。从协同划分与设计技术出发,通过嵌入式软件的函数化、产品化能够促进分工专业化,减少重复劳动。

1. Bootloader/BSP 特性

Bootloader 与BSP 配合,通过初始化硬件设备、建立内存空间映射,“屏敝”硬件环境,为调用操作系统内核和应用程序运行作好准备。

1.1 Bootloader 特性与结构分析

Bootloader 是系统加电后首先运行的程序,主要依赖于硬件,建立一个通用版本几乎不可能。即使同一CPU,硬件稍作变化,Bootloader 也必须修改。建立良好的BootLoader 结构,为系统二次开发以及减轻BSP的开发难度、可移植提供有益帮助;同时,也是保护硬件平台设计知识产权的重要措施。

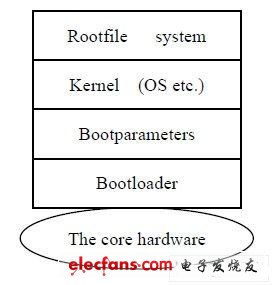

启动过程分单阶段(Single STage)和多阶段(Multi-Stage)。从协同性划分技术角度,设备初始化程序等通常放在stage 中,stage2 设置内核参数和调用,应具有可读性和可移植性。从固态存储设备上启动的Bootloader 大多都是两阶段的启动过程。Bootloader 的存贮体和分区:Flash/RAM/固态存贮器(图2);Flash 存储分区有连续和非连续两种方式。当系统需要多媒体等功能,用DOC(Disk ON Chip)技术解决大容量嵌入式OS 的存贮。

图2. 空间分配结构示意图

1.2 BSP 特性

作为板级支持软件包BSP 处在一个软硬件交界的中心位置,结构与功能随系统应用范围表现较大的差异。不同的硬件环境和操作系统,BSP 具有不同的内容与结构。从协同性角度,在系统设计初始阶段,就必须考虑BSP 可移植性、生成组件性以及快速性。如,BSP 的编程大多数是在成型的模板上进行,保持与上层OS 正确的接口。

2. Bootloader/BSP 协同性与设计

在建构嵌入式系统的过程中,应从系统结构和协同性角度,关注底层软件的设计。bootloaer 和BSP构成底层软件设计的核心内容,与硬件、过程、功能划分结合紧密。

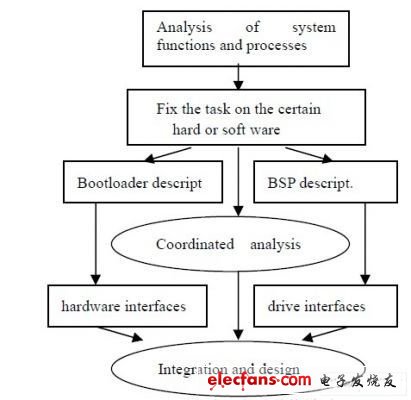

2.1 Bootloader 与BSP 协同性分析流程

首先用对任务所涉及的功能和过程进行系统级划分,确定将功能划分给软件还是硬件,对执行确定相关的“延迟”特性。形成模型创建、配置、*估等协同流程,克服传统孤立的设计模式。在面对系统低层软件Bootloader 与BSP 设计时,在前面分析系统结构以及特性基础上,给出如下系统性流程图。

图 3. 系统底层软件结构模型

2.2 基于ARM-μCLinux 系统bootloader 设计

在系统结构模型以及设计流程的基础上,下面通过实例说明bootloader 的主要设计过程。

基于ARM-μCLinux 嵌入式系统的启动引导过程:通过串口更新系统软件平台,完成启动、初始化、操作系统内核的固化和引导等。硬件平台由内嵌ARM10 的处理器、存储器2MBFlash 和16MBSDRAM、串口以及以太网口组成。软件平台组成:系统引导程序、嵌入式操作系统内核、文件系统。采用Flash 存储bootloader、内核等,直接访问内核所在地址区间的首地址。

2.3 μCLinux 内核的加载

系统采用μCLinux 自带的引导程序加载内核,用自举模式和内核启动模式相互切换;同时,切换到内核启动模式,自动安全地启动系统。针对ARM7TDMI 的无MMU 特性,采用修改后的μCLinux 内核引导程序加载操作系统和初始化环境,解决内核加载的地址重映射问题和操作系统的内存管理问题。

2.4 WinCE 系统下BootLoader

完成定制WinCE 的加载主要工作是编写启动加载程序bootloader 和板级支持包BSP。Bootloader 涉及到基本的硬件操作,如CPU 的结构、指令等,同时涉及以太网下载协议TFTP 和映像文件格式。Bootloader支持命令输入的方式,不用人工干预加载WinCE,其主控部分通过串口来接收用户的命令。

2.5 系统板级支持包BSP

由于硬件环境、Bootloader 映射范围以及二次开发等原因,系统启动加载程序Bootloader 不能把经过裁剪的OS 直接引导进入硬件环境,需要建立BSP 文件,如VxWorks 的BSP 和Linux 的BSP 相对于某一CPU 来说尽管实现的功能一样,写法和接口定义可以完全不同。BSP 的结构与内容差异性较大,依据不同的系统和应用环境,应设计建立合理、稳定的BSP 内核。

2.6 交叉融合

在分析过程、任务划分以及系统协同性的基础上,对系统底层软件设计应考虑Bootloader、BSP、接口以及应用程序交叉与融合。应用BSP 组成灵活性,设计充分考虑软硬件协同。接口驱动程序,如网络驱动、串口驱动和系统下载调试、部分应用程序可添加到BSP 中,从系统结构的角度是,简化软件层次和硬件尤其是存贮体系结构,当操作系统运行于硬件相对固定的系统,BSP 也相对固定,不需要做任何改动,建立独立的应用程序包。如果BSP 中的应用程序不断升级,将对系统稳定性造成影响。

图 4 表征了嵌入式系统三个软件环节的结构变化,Bootloader、BSP、接口驱动程序以及部分应用程序将产生融合与交叉。对于一次开发功能强大的嵌入式系统,应充分利用嵌入式处理器供应商提供的Bootloader,使建立BSP 的过程变得相对容易。

图 4. 软件交叉与融合示意图

3.结束语

通过对嵌入式系统结构与协同性探讨,分析了嵌入式系统的特点和协同性。应用结构协同思路与流程,建立一个结构良好与嵌入式核心硬件层密切相关的Bootloader 和BSP,对顺利植入裁剪良好的OS、简化软件结构以及保护硬件平台知识产权都有重要意义。嵌入式处理器种类多,系统结构不尽相同,Bootloader和BSP 的内容随之会产生差异,应充分考虑系统协同问题,避免传统的多次设计、反复实验的方式,为实际应用提供有益帮助。

上一篇:现场总线的选用问题

下一篇:USB概述与EZ-USB 2131Q芯片

推荐阅读最新更新时间:2023-10-12 20:54

- 在发送信号链设计中使用差分转单端射频放大器的优势

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 安森美推出业界领先的模拟和混合信号平台

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 国产高精度、高速率ADC芯片,正在崛起

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

嵌入式C编程与Atmel AVR_(美国)

嵌入式C编程与Atmel AVR_(美国) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号