超低功耗、高集成的模拟前端芯片MAX5865是针对便携式通信设备例如手机、PDA、WLAN以及3G无线终端而设计的,芯片内部集成了双路8位接收ADC和双路10位发送DAC,可在40Msps转换速率下提供超低功耗与更高的动态性能。芯片中的ADC模拟输入放大器为全差分结构,可以接受1VP-P满量程信号;而DAC模拟输出则是全差分信号,在1.4V共模电压下的满量程输出范围为400mV。利用兼容于SPITM和MICROWIRETM的3线串行接口可对工作模式进行控制,并可进行电源管理,同时可以选择关断、空闲、待机、发送、接收及收发模式。通过3线串口将器件配置为发送、接收或收发模式,可使MAX5865工作在FDD或TDD系统。在TDD模式下,接收与发送DAC可以共用数字总线,并可将数字I/O的数目减少到一组10位并行多路复用总线;而在FDD模式下,MAX5865的数字I/O可以被配置为18位并行多路复用总线,以满足双8位ADC与双10位DAC的需要。

1 MAX5865的工作原理

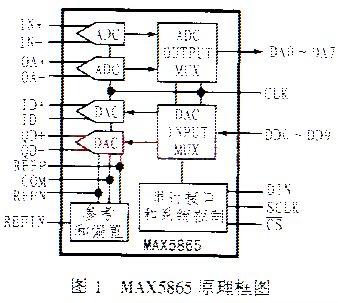

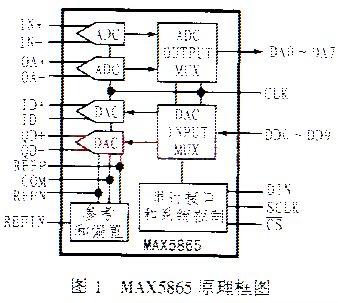

图1所示为MAX5865内部结构原理框图,其中,ADC采用七级、全差分、流水线结构,可以在低功耗下进行高速转换。每半个时钟周期对输入信号进行一次采样。包括输出锁存延时在内,通道I的总延迟时间为5个时钟周期,而通道Q则为5.5个时钟周期,图2给出了ADC时钟、模拟输入以及相应输出数据之间的时序关系。ADC的满量程模拟输入范围为VREF,共模输入范围为VDD/2%26;#177;0.2V。VREF为VREFP与VREFN之差。由于MAX5865中的ADC前端带有宽带T/H放大器,因此,ADC能够跟踪并采样/保持高频模拟输入>奈魁斯特频率。使用时可以通过差分方式或单端方式驱动两路ADC输入IA+ QA+ IA-与QA-。为了获得最佳性能,应该使IA+与IA-以及QA+与QA-间的阻抗相匹配,并将共模电压设定为电源电压的一半VDD/2。ADC数字逻辑输出DA0~DA7的逻辑电平由OVDD决定,OVDD的取值范围为1.8V至VDD,输出编码为偏移二进制码。数字输出DA0~DA7的容性负载必须尽可能低<15pF,以避免大的数字电流反馈到MAX5865的模拟部分而降低系统的动态性能。通过数字输出端的缓冲器可将其与大的容性负载相隔离。而在数字输出端靠近MAX5865的地方串联一个100Ω电阻,则有助于改善ADC性能。

MAX5865的10位DAC可以工作在高达40MHz的时钟速率下,两路DAC的数字输入DD0~DD9将复用10位总线。电压基准决定了数据转换器的满量程输出。DAC采用电流阵列技术,用1mA1.024V基准下满量程输出电流驱动400Ω内部电阻可得到%26;#177;400mV的满量程差分输出电压。而采用差分输出设计时,将模拟输出偏置在1.4V共模电压,则可驱动输入阻抗大于70kΩ的差分输入级,从而简化RF正交上变频器与模拟前端电路的接口。RF上变频器需要1.3V至1.5V的共模偏压,内部直流共模偏压在保持每个发送DAC整个动态范围的同时可以省去分立的电平偏移设置电阻,而且不需要编码发生器产生电平偏移。图2(b)给出了时钟、输入数据与模拟输出之间的时序关系。一般情况下,I通道数据ID在时钟信号的下降沿锁存,Q通道数据QD则在时钟信号的上升沿锁存。I与Q通道的输出同时在时钟信号的下一个上升沿被刷新。

3线串口可用来控制MAX5865的工作模式。上电时,首先必须通过编程使MAX5865工作在所希望的模式下。利用3线串口对器件编程可以使器件工作在关断、空闲、待机、Rx、Tx或Xcvr模式下,同时可由一个8位数据寄存器来设置工作模式,并可在所有六种模式下使串口均保持有效。在关断模式下,MAX5865的模拟电路均被关断,ADC的数字输出被置为三态模式,从而最大限度地降低了功耗;而空闲模式时,只有基准与时钟分配电路上电,所有其它功能电路均被关断,ADC输出被强制为高阻态。而在待机状态下,只有ADC基准上电,器件的其它功能电路均关断,流水线ADC亦被关断,DA0~DA7为高阻态。

图2

2 MAX5865的典型应用

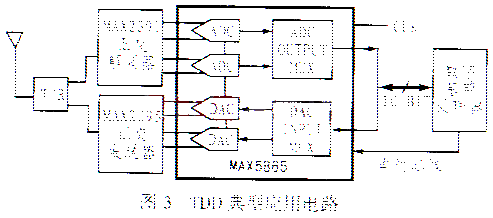

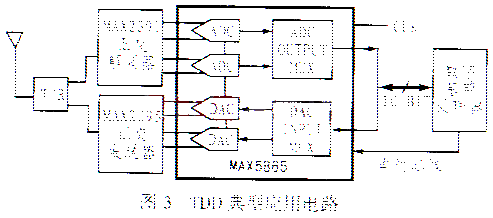

MAX5865能以FDD或TDD模式工作在各种不同的应用中如在WCDMA-3GPP FDD与4G技术的FDD应用中工作于Xcvr模式,或在TD-SCDMA、WCDMA-3GPPTDD、IEEE802.11a/b/g及IEEE 802.16等TDD应用中在Tx与Rx模式间切换等。在FDD模式下,ADC和DAC可同时工作,且当fCLK 为 40MHz时,消耗的功率为75.6mW。实际上,ADC总线与DAC总线是分开的,并与数字基带处理器通过18位(8位ADC与10位DAC)并行总线进行连接。而在TDD模式下,ADC与DAC交替工作,ADC与DAC总线共享,它们一起构成10位并行总线连到数字基带处理器,并可通过3线串行接口选择Rx模式以启用ADC或选择Tx模式启用DAC。由于在Rx模式下,DAC内核被禁用而不能发送;而Tx模式下,ADC总线为高阻态,从而消除了杂散辐射,同时也避免总线冲突。在TDD模式下,当fCLK为40MHz时,Rx模式下的功耗为63mW,Tx模式下的DAC功耗为38.4mW。

图3所示是MAX5865工作在TDD模式的应用电路,该方案提供了完整的802.11b射频前端解决方案。由于MAX5865的DAC采用共模电压为1.4V的全差分模拟输出,而ADC具有较宽的输入共模范围,可以直接与RF收发器接口,因此可省去电平转换电路所需要的分立元件和放大器。同时,由于内部产生共模电压免除了编码发生器的电平偏移或由电阻电平偏移引起的衰减,DAC保持了全动态范围。MAX5865的ADC具有1VP-P满量程范围,可接受VDD/2 %26;#177;200mV的输入共模电平。由于可以省去分立的增益放大器与电平转换元件,因此简化了RF正交解调器与ADC之间的模拟接口。

3 设计注意事项

3.1 系统时钟输入(CLK)

MAX5865芯片的ADC与DAC共享同一CLK输入,该输入接受由OVDD设定的CMOS兼容信号电平,范围为1.8V至VDD。由于器件的级间转换取决于外部时钟上升沿和下降沿的重复性,因此,设计时应采用具有低抖动、快速上升和下降(<2ns)的时钟。特别是在时钟信号的上升沿进行采样时,其上升沿的抖动更应尽可能地低。任何明显的时钟抖动都会影响片上ADC的SNR性能。

实际上,欠采样应用对时钟抖动的要求更严格,由于此时有可能将时钟输入作为模拟输入对待,因此,布线时应避开任何模拟输入或其它数字信号线。MAX5865的时钟输入工作在OVDD/2电压阈值下,能接受50%%26;#177;15%的占空比。

3.2 基准配置

MAX5865内部具有精密的1.024V内部带隙基准,该基准可在整个电源供电范围与温度范围内保持稳定。在内部基准模式下,REFIN接VDD时的VREF是由内部产生的0.512V。COM、REFP、REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/2、VREFN=VDD/2-VREF/2。分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。

在外部基准模式下,在REFIN引脚一般应施加1.024V%26;#177;10%的电压。该模式下,COM、REFP与REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/4、VREFN=VDD/2-VREF/4。可分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。在该模式下,DAC的满量程输出电压和共模电压均与外部基准成正比。例如,若VREFIN增加10%(最大值),则DAC的满量程输出电压也增加10%或达到%26;#177;440mV,同时共模电压也将增加10%。

1 MAX5865的工作原理

图1所示为MAX5865内部结构原理框图,其中,ADC采用七级、全差分、流水线结构,可以在低功耗下进行高速转换。每半个时钟周期对输入信号进行一次采样。包括输出锁存延时在内,通道I的总延迟时间为5个时钟周期,而通道Q则为5.5个时钟周期,图2给出了ADC时钟、模拟输入以及相应输出数据之间的时序关系。ADC的满量程模拟输入范围为VREF,共模输入范围为VDD/2%26;#177;0.2V。VREF为VREFP与VREFN之差。由于MAX5865中的ADC前端带有宽带T/H放大器,因此,ADC能够跟踪并采样/保持高频模拟输入>奈魁斯特频率。使用时可以通过差分方式或单端方式驱动两路ADC输入IA+ QA+ IA-与QA-。为了获得最佳性能,应该使IA+与IA-以及QA+与QA-间的阻抗相匹配,并将共模电压设定为电源电压的一半VDD/2。ADC数字逻辑输出DA0~DA7的逻辑电平由OVDD决定,OVDD的取值范围为1.8V至VDD,输出编码为偏移二进制码。数字输出DA0~DA7的容性负载必须尽可能低<15pF,以避免大的数字电流反馈到MAX5865的模拟部分而降低系统的动态性能。通过数字输出端的缓冲器可将其与大的容性负载相隔离。而在数字输出端靠近MAX5865的地方串联一个100Ω电阻,则有助于改善ADC性能。

MAX5865的10位DAC可以工作在高达40MHz的时钟速率下,两路DAC的数字输入DD0~DD9将复用10位总线。电压基准决定了数据转换器的满量程输出。DAC采用电流阵列技术,用1mA1.024V基准下满量程输出电流驱动400Ω内部电阻可得到%26;#177;400mV的满量程差分输出电压。而采用差分输出设计时,将模拟输出偏置在1.4V共模电压,则可驱动输入阻抗大于70kΩ的差分输入级,从而简化RF正交上变频器与模拟前端电路的接口。RF上变频器需要1.3V至1.5V的共模偏压,内部直流共模偏压在保持每个发送DAC整个动态范围的同时可以省去分立的电平偏移设置电阻,而且不需要编码发生器产生电平偏移。图2(b)给出了时钟、输入数据与模拟输出之间的时序关系。一般情况下,I通道数据ID在时钟信号的下降沿锁存,Q通道数据QD则在时钟信号的上升沿锁存。I与Q通道的输出同时在时钟信号的下一个上升沿被刷新。

3线串口可用来控制MAX5865的工作模式。上电时,首先必须通过编程使MAX5865工作在所希望的模式下。利用3线串口对器件编程可以使器件工作在关断、空闲、待机、Rx、Tx或Xcvr模式下,同时可由一个8位数据寄存器来设置工作模式,并可在所有六种模式下使串口均保持有效。在关断模式下,MAX5865的模拟电路均被关断,ADC的数字输出被置为三态模式,从而最大限度地降低了功耗;而空闲模式时,只有基准与时钟分配电路上电,所有其它功能电路均被关断,ADC输出被强制为高阻态。而在待机状态下,只有ADC基准上电,器件的其它功能电路均关断,流水线ADC亦被关断,DA0~DA7为高阻态。

图2

2 MAX5865的典型应用

MAX5865能以FDD或TDD模式工作在各种不同的应用中如在WCDMA-3GPP FDD与4G技术的FDD应用中工作于Xcvr模式,或在TD-SCDMA、WCDMA-3GPPTDD、IEEE802.11a/b/g及IEEE 802.16等TDD应用中在Tx与Rx模式间切换等。在FDD模式下,ADC和DAC可同时工作,且当fCLK 为 40MHz时,消耗的功率为75.6mW。实际上,ADC总线与DAC总线是分开的,并与数字基带处理器通过18位(8位ADC与10位DAC)并行总线进行连接。而在TDD模式下,ADC与DAC交替工作,ADC与DAC总线共享,它们一起构成10位并行总线连到数字基带处理器,并可通过3线串行接口选择Rx模式以启用ADC或选择Tx模式启用DAC。由于在Rx模式下,DAC内核被禁用而不能发送;而Tx模式下,ADC总线为高阻态,从而消除了杂散辐射,同时也避免总线冲突。在TDD模式下,当fCLK为40MHz时,Rx模式下的功耗为63mW,Tx模式下的DAC功耗为38.4mW。

图3所示是MAX5865工作在TDD模式的应用电路,该方案提供了完整的802.11b射频前端解决方案。由于MAX5865的DAC采用共模电压为1.4V的全差分模拟输出,而ADC具有较宽的输入共模范围,可以直接与RF收发器接口,因此可省去电平转换电路所需要的分立元件和放大器。同时,由于内部产生共模电压免除了编码发生器的电平偏移或由电阻电平偏移引起的衰减,DAC保持了全动态范围。MAX5865的ADC具有1VP-P满量程范围,可接受VDD/2 %26;#177;200mV的输入共模电平。由于可以省去分立的增益放大器与电平转换元件,因此简化了RF正交解调器与ADC之间的模拟接口。

3 设计注意事项

3.1 系统时钟输入(CLK)

MAX5865芯片的ADC与DAC共享同一CLK输入,该输入接受由OVDD设定的CMOS兼容信号电平,范围为1.8V至VDD。由于器件的级间转换取决于外部时钟上升沿和下降沿的重复性,因此,设计时应采用具有低抖动、快速上升和下降(<2ns)的时钟。特别是在时钟信号的上升沿进行采样时,其上升沿的抖动更应尽可能地低。任何明显的时钟抖动都会影响片上ADC的SNR性能。

实际上,欠采样应用对时钟抖动的要求更严格,由于此时有可能将时钟输入作为模拟输入对待,因此,布线时应避开任何模拟输入或其它数字信号线。MAX5865的时钟输入工作在OVDD/2电压阈值下,能接受50%%26;#177;15%的占空比。

3.2 基准配置

MAX5865内部具有精密的1.024V内部带隙基准,该基准可在整个电源供电范围与温度范围内保持稳定。在内部基准模式下,REFIN接VDD时的VREF是由内部产生的0.512V。COM、REFP、REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/2、VREFN=VDD/2-VREF/2。分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。

在外部基准模式下,在REFIN引脚一般应施加1.024V%26;#177;10%的电压。该模式下,COM、REFP与REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/4、VREFN=VDD/2-VREF/4。可分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。在该模式下,DAC的满量程输出电压和共模电压均与外部基准成正比。例如,若VREFIN增加10%(最大值),则DAC的满量程输出电压也增加10%或达到%26;#177;440mV,同时共模电压也将增加10%。

3.3 输入/输出耦合电路

通常,MAX5865在全差分输入信号下可提供比单端信号更好的SFDR与THD性能,尤其是在高输入频率的情况下。在差分模式下,当输入IA+、I-A-、QA+、QA-对称时,偶次谐波会更低,并且每路ADC输入仅需要单端模式信号摆幅的一半。而通过非平衡变压器可为单端信号源至全差分信号的转换提供出色的解决方案,并可获得极佳的ADC性能。当然,在没有非平衡变压器的情况下,也可以使用运放来驱动MAX5865的ADC,此时,MAXIM公司的MAX4353/MAX4454等运放便可提供高速、带宽、低噪声与低失真性能,以保持输入信号的完整性。

3.4 线路板布线

MAX5865需要采用高速电路布线设计技术,电路布局可以参考MAX5865评估板数据资料。所有旁路电容应尽可能靠近器件安装,并与器件位于电路板的同侧,同时应该选用表贴器件以减小电感。可用0.1μF陶瓷电容与2.2μF电容并联,以将VDD旁路到GND;也可用0.1μF陶瓷电容与2.2μF电容并联将OVDD旁路到OGND;同时分别用0.33μF陶瓷电容将REFP、REFN与COM旁路到GND;而用0.1μF电容将REFIN旁路到GND。

通过具有独立地平面与电源平面层的多层板可以获得最佳的信号完整性。模拟地(GND)与数字输出驱动地(OGND)应采用独立的地平面,并分别与器件封装上的物理位置相匹配,MAX5865裸露的背面焊盘接到GND平面,两个地平面应单点相连,以使噪声较大的数字地电流不会影响模拟地平面。两个地平面之间空隙上的一点通常是单点共地的最佳位置,可以用一个低阻值的表贴电阻(1Ω至5Ω)、磁珠或直接短路来完成该连接。如果该地平面与所有噪声较大的数字系统地平面如后续输出缓冲器或DSP地平面充分隔离,也可以使所有接地引脚共享同一个地平面。此外,高速数字信号布线应远离敏感的模拟信号布线,以确保模拟输入与相应的转换器隔离,减小通道间的串扰。同时应确保所有信号引线尽可能短,并应避免90%26;#176;转角。

3.3 输入/输出耦合电路

通常,MAX5865在全差分输入信号下可提供比单端信号更好的SFDR与THD性能,尤其是在高输入频率的情况下。在差分模式下,当输入IA+、I-A-、QA+、QA-对称时,偶次谐波会更低,并且每路ADC输入仅需要单端模式信号摆幅的一半。而通过非平衡变压器可为单端信号源至全差分信号的转换提供出色的解决方案,并可获得极佳的ADC性能。当然,在没有非平衡变压器的情况下,也可以使用运放来驱动MAX5865的ADC,此时,MAXIM公司的MAX4353/MAX4454等运放便可提供高速、带宽、低噪声与低失真性能,以保持输入信号的完整性。

3.4 线路板布线

MAX5865需要采用高速电路布线设计技术,电路布局可以参考MAX5865评估板数据资料。所有旁路电容应尽可能靠近器件安装,并与器件位于电路板的同侧,同时应该选用表贴器件以减小电感。可用0.1μF陶瓷电容与2.2μF电容并联,以将VDD旁路到GND;也可用0.1μF陶瓷电容与2.2μF电容并联将OVDD旁路到OGND;同时分别用0.33μF陶瓷电容将REFP、REFN与COM旁路到GND;而用0.1μF电容将REFIN旁路到GND。

通过具有独立地平面与电源平面层的多层板可以获得最佳的信号完整性。模拟地(GND)与数字输出驱动地(OGND)应采用独立的地平面,并分别与器件封装上的物理位置相匹配,MAX5865裸露的背面焊盘接到GND平面,两个地平面应单点相连,以使噪声较大的数字地电流不会影响模拟地平面。两个地平面之间空隙上的一点通常是单点共地的最佳位置,可以用一个低阻值的表贴电阻(1Ω至5Ω)、磁珠或直接短路来完成该连接。如果该地平面与所有噪声较大的数字系统地平面如后续输出缓冲器或DSP地平面充分隔离,也可以使所有接地引脚共享同一个地平面。此外,高速数字信号布线应远离敏感的模拟信号布线,以确保模拟输入与相应的转换器隔离,减小通道间的串扰。同时应确保所有信号引线尽可能短,并应避免90%26;#176;转角。

编辑: 引用地址:低功耗模拟前端电路设计

1 MAX5865的工作原理

图1所示为MAX5865内部结构原理框图,其中,ADC采用七级、全差分、流水线结构,可以在低功耗下进行高速转换。每半个时钟周期对输入信号进行一次采样。包括输出锁存延时在内,通道I的总延迟时间为5个时钟周期,而通道Q则为5.5个时钟周期,图2给出了ADC时钟、模拟输入以及相应输出数据之间的时序关系。ADC的满量程模拟输入范围为VREF,共模输入范围为VDD/2%26;#177;0.2V。VREF为VREFP与VREFN之差。由于MAX5865中的ADC前端带有宽带T/H放大器,因此,ADC能够跟踪并采样/保持高频模拟输入>奈魁斯特频率。使用时可以通过差分方式或单端方式驱动两路ADC输入IA+ QA+ IA-与QA-。为了获得最佳性能,应该使IA+与IA-以及QA+与QA-间的阻抗相匹配,并将共模电压设定为电源电压的一半VDD/2。ADC数字逻辑输出DA0~DA7的逻辑电平由OVDD决定,OVDD的取值范围为1.8V至VDD,输出编码为偏移二进制码。数字输出DA0~DA7的容性负载必须尽可能低<15pF,以避免大的数字电流反馈到MAX5865的模拟部分而降低系统的动态性能。通过数字输出端的缓冲器可将其与大的容性负载相隔离。而在数字输出端靠近MAX5865的地方串联一个100Ω电阻,则有助于改善ADC性能。

MAX5865的10位DAC可以工作在高达40MHz的时钟速率下,两路DAC的数字输入DD0~DD9将复用10位总线。电压基准决定了数据转换器的满量程输出。DAC采用电流阵列技术,用1mA1.024V基准下满量程输出电流驱动400Ω内部电阻可得到%26;#177;400mV的满量程差分输出电压。而采用差分输出设计时,将模拟输出偏置在1.4V共模电压,则可驱动输入阻抗大于70kΩ的差分输入级,从而简化RF正交上变频器与模拟前端电路的接口。RF上变频器需要1.3V至1.5V的共模偏压,内部直流共模偏压在保持每个发送DAC整个动态范围的同时可以省去分立的电平偏移设置电阻,而且不需要编码发生器产生电平偏移。图2(b)给出了时钟、输入数据与模拟输出之间的时序关系。一般情况下,I通道数据ID在时钟信号的下降沿锁存,Q通道数据QD则在时钟信号的上升沿锁存。I与Q通道的输出同时在时钟信号的下一个上升沿被刷新。

3线串口可用来控制MAX5865的工作模式。上电时,首先必须通过编程使MAX5865工作在所希望的模式下。利用3线串口对器件编程可以使器件工作在关断、空闲、待机、Rx、Tx或Xcvr模式下,同时可由一个8位数据寄存器来设置工作模式,并可在所有六种模式下使串口均保持有效。在关断模式下,MAX5865的模拟电路均被关断,ADC的数字输出被置为三态模式,从而最大限度地降低了功耗;而空闲模式时,只有基准与时钟分配电路上电,所有其它功能电路均被关断,ADC输出被强制为高阻态。而在待机状态下,只有ADC基准上电,器件的其它功能电路均关断,流水线ADC亦被关断,DA0~DA7为高阻态。

图2

2 MAX5865的典型应用

MAX5865能以FDD或TDD模式工作在各种不同的应用中如在WCDMA-3GPP FDD与4G技术的FDD应用中工作于Xcvr模式,或在TD-SCDMA、WCDMA-3GPPTDD、IEEE802.11a/b/g及IEEE 802.16等TDD应用中在Tx与Rx模式间切换等。在FDD模式下,ADC和DAC可同时工作,且当fCLK 为 40MHz时,消耗的功率为75.6mW。实际上,ADC总线与DAC总线是分开的,并与数字基带处理器通过18位(8位ADC与10位DAC)并行总线进行连接。而在TDD模式下,ADC与DAC交替工作,ADC与DAC总线共享,它们一起构成10位并行总线连到数字基带处理器,并可通过3线串行接口选择Rx模式以启用ADC或选择Tx模式启用DAC。由于在Rx模式下,DAC内核被禁用而不能发送;而Tx模式下,ADC总线为高阻态,从而消除了杂散辐射,同时也避免总线冲突。在TDD模式下,当fCLK为40MHz时,Rx模式下的功耗为63mW,Tx模式下的DAC功耗为38.4mW。

图3所示是MAX5865工作在TDD模式的应用电路,该方案提供了完整的802.11b射频前端解决方案。由于MAX5865的DAC采用共模电压为1.4V的全差分模拟输出,而ADC具有较宽的输入共模范围,可以直接与RF收发器接口,因此可省去电平转换电路所需要的分立元件和放大器。同时,由于内部产生共模电压免除了编码发生器的电平偏移或由电阻电平偏移引起的衰减,DAC保持了全动态范围。MAX5865的ADC具有1VP-P满量程范围,可接受VDD/2 %26;#177;200mV的输入共模电平。由于可以省去分立的增益放大器与电平转换元件,因此简化了RF正交解调器与ADC之间的模拟接口。

3 设计注意事项

3.1 系统时钟输入(CLK)

MAX5865芯片的ADC与DAC共享同一CLK输入,该输入接受由OVDD设定的CMOS兼容信号电平,范围为1.8V至VDD。由于器件的级间转换取决于外部时钟上升沿和下降沿的重复性,因此,设计时应采用具有低抖动、快速上升和下降(<2ns)的时钟。特别是在时钟信号的上升沿进行采样时,其上升沿的抖动更应尽可能地低。任何明显的时钟抖动都会影响片上ADC的SNR性能。

实际上,欠采样应用对时钟抖动的要求更严格,由于此时有可能将时钟输入作为模拟输入对待,因此,布线时应避开任何模拟输入或其它数字信号线。MAX5865的时钟输入工作在OVDD/2电压阈值下,能接受50%%26;#177;15%的占空比。

3.2 基准配置

MAX5865内部具有精密的1.024V内部带隙基准,该基准可在整个电源供电范围与温度范围内保持稳定。在内部基准模式下,REFIN接VDD时的VREF是由内部产生的0.512V。COM、REFP、REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/2、VREFN=VDD/2-VREF/2。分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。

在外部基准模式下,在REFIN引脚一般应施加1.024V%26;#177;10%的电压。该模式下,COM、REFP与REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/4、VREFN=VDD/2-VREF/4。可分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。在该模式下,DAC的满量程输出电压和共模电压均与外部基准成正比。例如,若VREFIN增加10%(最大值),则DAC的满量程输出电压也增加10%或达到%26;#177;440mV,同时共模电压也将增加10%。

1 MAX5865的工作原理

图1所示为MAX5865内部结构原理框图,其中,ADC采用七级、全差分、流水线结构,可以在低功耗下进行高速转换。每半个时钟周期对输入信号进行一次采样。包括输出锁存延时在内,通道I的总延迟时间为5个时钟周期,而通道Q则为5.5个时钟周期,图2给出了ADC时钟、模拟输入以及相应输出数据之间的时序关系。ADC的满量程模拟输入范围为VREF,共模输入范围为VDD/2%26;#177;0.2V。VREF为VREFP与VREFN之差。由于MAX5865中的ADC前端带有宽带T/H放大器,因此,ADC能够跟踪并采样/保持高频模拟输入>奈魁斯特频率。使用时可以通过差分方式或单端方式驱动两路ADC输入IA+ QA+ IA-与QA-。为了获得最佳性能,应该使IA+与IA-以及QA+与QA-间的阻抗相匹配,并将共模电压设定为电源电压的一半VDD/2。ADC数字逻辑输出DA0~DA7的逻辑电平由OVDD决定,OVDD的取值范围为1.8V至VDD,输出编码为偏移二进制码。数字输出DA0~DA7的容性负载必须尽可能低<15pF,以避免大的数字电流反馈到MAX5865的模拟部分而降低系统的动态性能。通过数字输出端的缓冲器可将其与大的容性负载相隔离。而在数字输出端靠近MAX5865的地方串联一个100Ω电阻,则有助于改善ADC性能。

MAX5865的10位DAC可以工作在高达40MHz的时钟速率下,两路DAC的数字输入DD0~DD9将复用10位总线。电压基准决定了数据转换器的满量程输出。DAC采用电流阵列技术,用1mA1.024V基准下满量程输出电流驱动400Ω内部电阻可得到%26;#177;400mV的满量程差分输出电压。而采用差分输出设计时,将模拟输出偏置在1.4V共模电压,则可驱动输入阻抗大于70kΩ的差分输入级,从而简化RF正交上变频器与模拟前端电路的接口。RF上变频器需要1.3V至1.5V的共模偏压,内部直流共模偏压在保持每个发送DAC整个动态范围的同时可以省去分立的电平偏移设置电阻,而且不需要编码发生器产生电平偏移。图2(b)给出了时钟、输入数据与模拟输出之间的时序关系。一般情况下,I通道数据ID在时钟信号的下降沿锁存,Q通道数据QD则在时钟信号的上升沿锁存。I与Q通道的输出同时在时钟信号的下一个上升沿被刷新。

3线串口可用来控制MAX5865的工作模式。上电时,首先必须通过编程使MAX5865工作在所希望的模式下。利用3线串口对器件编程可以使器件工作在关断、空闲、待机、Rx、Tx或Xcvr模式下,同时可由一个8位数据寄存器来设置工作模式,并可在所有六种模式下使串口均保持有效。在关断模式下,MAX5865的模拟电路均被关断,ADC的数字输出被置为三态模式,从而最大限度地降低了功耗;而空闲模式时,只有基准与时钟分配电路上电,所有其它功能电路均被关断,ADC输出被强制为高阻态。而在待机状态下,只有ADC基准上电,器件的其它功能电路均关断,流水线ADC亦被关断,DA0~DA7为高阻态。

图2

2 MAX5865的典型应用

MAX5865能以FDD或TDD模式工作在各种不同的应用中如在WCDMA-3GPP FDD与4G技术的FDD应用中工作于Xcvr模式,或在TD-SCDMA、WCDMA-3GPPTDD、IEEE802.11a/b/g及IEEE 802.16等TDD应用中在Tx与Rx模式间切换等。在FDD模式下,ADC和DAC可同时工作,且当fCLK 为 40MHz时,消耗的功率为75.6mW。实际上,ADC总线与DAC总线是分开的,并与数字基带处理器通过18位(8位ADC与10位DAC)并行总线进行连接。而在TDD模式下,ADC与DAC交替工作,ADC与DAC总线共享,它们一起构成10位并行总线连到数字基带处理器,并可通过3线串行接口选择Rx模式以启用ADC或选择Tx模式启用DAC。由于在Rx模式下,DAC内核被禁用而不能发送;而Tx模式下,ADC总线为高阻态,从而消除了杂散辐射,同时也避免总线冲突。在TDD模式下,当fCLK为40MHz时,Rx模式下的功耗为63mW,Tx模式下的DAC功耗为38.4mW。

图3所示是MAX5865工作在TDD模式的应用电路,该方案提供了完整的802.11b射频前端解决方案。由于MAX5865的DAC采用共模电压为1.4V的全差分模拟输出,而ADC具有较宽的输入共模范围,可以直接与RF收发器接口,因此可省去电平转换电路所需要的分立元件和放大器。同时,由于内部产生共模电压免除了编码发生器的电平偏移或由电阻电平偏移引起的衰减,DAC保持了全动态范围。MAX5865的ADC具有1VP-P满量程范围,可接受VDD/2 %26;#177;200mV的输入共模电平。由于可以省去分立的增益放大器与电平转换元件,因此简化了RF正交解调器与ADC之间的模拟接口。

3 设计注意事项

3.1 系统时钟输入(CLK)

MAX5865芯片的ADC与DAC共享同一CLK输入,该输入接受由OVDD设定的CMOS兼容信号电平,范围为1.8V至VDD。由于器件的级间转换取决于外部时钟上升沿和下降沿的重复性,因此,设计时应采用具有低抖动、快速上升和下降(<2ns)的时钟。特别是在时钟信号的上升沿进行采样时,其上升沿的抖动更应尽可能地低。任何明显的时钟抖动都会影响片上ADC的SNR性能。

实际上,欠采样应用对时钟抖动的要求更严格,由于此时有可能将时钟输入作为模拟输入对待,因此,布线时应避开任何模拟输入或其它数字信号线。MAX5865的时钟输入工作在OVDD/2电压阈值下,能接受50%%26;#177;15%的占空比。

3.2 基准配置

MAX5865内部具有精密的1.024V内部带隙基准,该基准可在整个电源供电范围与温度范围内保持稳定。在内部基准模式下,REFIN接VDD时的VREF是由内部产生的0.512V。COM、REFP、REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/2、VREFN=VDD/2-VREF/2。分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。

在外部基准模式下,在REFIN引脚一般应施加1.024V%26;#177;10%的电压。该模式下,COM、REFP与REFN均为低阻输出,电压分别为VCOM=VDD/2、VREFP=VDD/2+VREF/4、VREFN=VDD/2-VREF/4。可分别用0.33μF电容作为REFP、REFN与COM引脚的旁路电容,并用0.1μF电容将REFIN旁路到GND。在该模式下,DAC的满量程输出电压和共模电压均与外部基准成正比。例如,若VREFIN增加10%(最大值),则DAC的满量程输出电压也增加10%或达到%26;#177;440mV,同时共模电压也将增加10%。

3.3 输入/输出耦合电路

通常,MAX5865在全差分输入信号下可提供比单端信号更好的SFDR与THD性能,尤其是在高输入频率的情况下。在差分模式下,当输入IA+、I-A-、QA+、QA-对称时,偶次谐波会更低,并且每路ADC输入仅需要单端模式信号摆幅的一半。而通过非平衡变压器可为单端信号源至全差分信号的转换提供出色的解决方案,并可获得极佳的ADC性能。当然,在没有非平衡变压器的情况下,也可以使用运放来驱动MAX5865的ADC,此时,MAXIM公司的MAX4353/MAX4454等运放便可提供高速、带宽、低噪声与低失真性能,以保持输入信号的完整性。

3.4 线路板布线

MAX5865需要采用高速电路布线设计技术,电路布局可以参考MAX5865评估板数据资料。所有旁路电容应尽可能靠近器件安装,并与器件位于电路板的同侧,同时应该选用表贴器件以减小电感。可用0.1μF陶瓷电容与2.2μF电容并联,以将VDD旁路到GND;也可用0.1μF陶瓷电容与2.2μF电容并联将OVDD旁路到OGND;同时分别用0.33μF陶瓷电容将REFP、REFN与COM旁路到GND;而用0.1μF电容将REFIN旁路到GND。

通过具有独立地平面与电源平面层的多层板可以获得最佳的信号完整性。模拟地(GND)与数字输出驱动地(OGND)应采用独立的地平面,并分别与器件封装上的物理位置相匹配,MAX5865裸露的背面焊盘接到GND平面,两个地平面应单点相连,以使噪声较大的数字地电流不会影响模拟地平面。两个地平面之间空隙上的一点通常是单点共地的最佳位置,可以用一个低阻值的表贴电阻(1Ω至5Ω)、磁珠或直接短路来完成该连接。如果该地平面与所有噪声较大的数字系统地平面如后续输出缓冲器或DSP地平面充分隔离,也可以使所有接地引脚共享同一个地平面。此外,高速数字信号布线应远离敏感的模拟信号布线,以确保模拟输入与相应的转换器隔离,减小通道间的串扰。同时应确保所有信号引线尽可能短,并应避免90%26;#176;转角。

3.3 输入/输出耦合电路

通常,MAX5865在全差分输入信号下可提供比单端信号更好的SFDR与THD性能,尤其是在高输入频率的情况下。在差分模式下,当输入IA+、I-A-、QA+、QA-对称时,偶次谐波会更低,并且每路ADC输入仅需要单端模式信号摆幅的一半。而通过非平衡变压器可为单端信号源至全差分信号的转换提供出色的解决方案,并可获得极佳的ADC性能。当然,在没有非平衡变压器的情况下,也可以使用运放来驱动MAX5865的ADC,此时,MAXIM公司的MAX4353/MAX4454等运放便可提供高速、带宽、低噪声与低失真性能,以保持输入信号的完整性。

3.4 线路板布线

MAX5865需要采用高速电路布线设计技术,电路布局可以参考MAX5865评估板数据资料。所有旁路电容应尽可能靠近器件安装,并与器件位于电路板的同侧,同时应该选用表贴器件以减小电感。可用0.1μF陶瓷电容与2.2μF电容并联,以将VDD旁路到GND;也可用0.1μF陶瓷电容与2.2μF电容并联将OVDD旁路到OGND;同时分别用0.33μF陶瓷电容将REFP、REFN与COM旁路到GND;而用0.1μF电容将REFIN旁路到GND。

通过具有独立地平面与电源平面层的多层板可以获得最佳的信号完整性。模拟地(GND)与数字输出驱动地(OGND)应采用独立的地平面,并分别与器件封装上的物理位置相匹配,MAX5865裸露的背面焊盘接到GND平面,两个地平面应单点相连,以使噪声较大的数字地电流不会影响模拟地平面。两个地平面之间空隙上的一点通常是单点共地的最佳位置,可以用一个低阻值的表贴电阻(1Ω至5Ω)、磁珠或直接短路来完成该连接。如果该地平面与所有噪声较大的数字系统地平面如后续输出缓冲器或DSP地平面充分隔离,也可以使所有接地引脚共享同一个地平面。此外,高速数字信号布线应远离敏感的模拟信号布线,以确保模拟输入与相应的转换器隔离,减小通道间的串扰。同时应确保所有信号引线尽可能短,并应避免90%26;#176;转角。

上一篇:AGC中频放大器设计

下一篇:数字控制可变增益放大器AD8370及其应用

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LTC6252CS6#PBF

LTC6252CS6#PBF

京公网安备 11010802033920号

京公网安备 11010802033920号