引言

节电是各种电池供电设备所需考虑的首要因素。为防止用户忘记关机,一些设备采用了自动关机电路。此外,许多设备中使用一个开/关按键控制开启或关断电源,即使微处理器(MPU)正在处理关键程序,按键按下时,系统也会关断,造成重要数据的丢失。本文仅使用一个D触发器设计了一种结构简单,使用方便可靠的开/关机电路。

电路设计

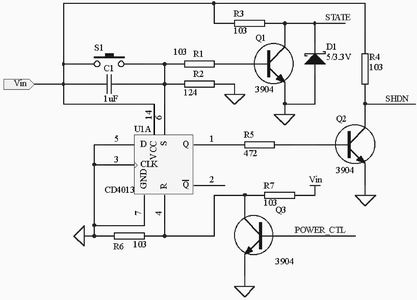

实际设计的自动开/关机电路如图1所示。其中U1A为双D触发器CD4013,外接电池电源由Vin输入。Q输出通过阻值为472W的R5、103W的R4和NPN型三极管Q2反向驱动后,与开关电源芯片的开关引脚相连。以MAX1626为例,当SHDN为高时关闭电源,SHDN为低时打开系统电源。

复位式按键S1为系统电源开/关键。C1和R2组成RC网络,使得在S1按下后,保证R有12×104×10-3=120ms的延迟时间处于高电平。CD4013的D、CLK端接输入电源地,保证其处于低电平。置位引脚R一端通过103W的电阻接电源地,另一端通过三极管Q3与MPU的I/O口相连。S1的右端与阻值为103W的R1相连,控制Q1开通。Q1的集电极与地之间接通稳压管,稳压管的输出与MPU的I/O口相连。

图1 自动开/关机电路原理图

设计原理

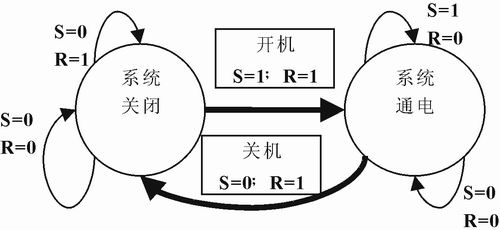

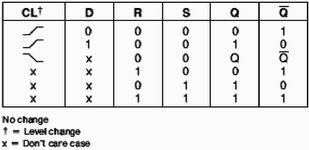

开/关机电路的核心器件是一个D型触发器,型号为CD4013。其真值表如表1所示。观察其真值表可已看出,无论CLK为何种状态,S为0时,输出Q为0;R为0时,输出Q为1;而当R、S均为1时,输出Q为1;当R和S均为0时,只要CLK不产生上升沿脉冲,输出Q会保持前一输出状态。本电路正是利用R、S均为零时的状态保持特性来实现开/关机功能的。

由于本电路处于开/关电源前端,在电池接入状态下,无论系统电源是否打开,都处于工作状态。CD4013的输入电压范围为3~15V,因此本电路可以保证在宽电压输入范围内稳定工作。

系统开机原理

当按下开机按钮S1时,S与高电平接通,S=1。查阅真值表可得,当R=1,S=1时,输出Q应稳定输出1,经过三极管反向后,电源控制引脚SHDN为低电平,打开系统电源。通常MPU进行初始化时会将I/O引脚置为高电平,由于RC网络的延迟作用,S1按下后可以保证S端约有120ms处于高电平(保证开机稳定条件:RC网络的延迟时间>系统上电复位并将POWER_CTL状态稳定为1的时间)。经过三极管Q3反向,此时S=1,R=0,Q端输出1,系统电源处于打开状态。

MPU延迟后读取STATE引脚的状态。如果此时STATE为低电平,则确认Q1导通,S1曾按下,确认用户开机程序正常运行。如果此时STATE为高电平,则表明Q1截止,开机信号为误动作,程序执行关机程序。

当RC网络的延迟时间过后,S端由1转为0,此时S=0,R=0,查阅真值表得出此时输出Q应该维持前一输出状态,即保持系统开通电源状态。

系统关机原理

作为节电产品,如果在规定时间内系统没有工作,系统会自动转入关机程序,在保存重要数据后,自动关闭系统。

当用户手动关机,按下S1时,Q1打开,STATE的状态由高电平转变为低电平,MPU检测到STATE的状态变化后,经过延时再次检测STATE状态,如仍为低电平,则确认为关机指令,程序将保存重要数据,关闭所有中断,然后将I/O引脚POWER_CTL置为低电平,程序进入循环等待关机状态。此时,I/O口状态经过Q3反相后使触发器R=1,S=0,查阅真值表可得Q端应该稳定输出0,经过三极管Q2反向驱动后,电源控制引脚SHDN为高电平,关闭系统电源。

电源芯片关闭后,随着电容放电,MPU的供电电压不断下降,引脚POWER_CTL变为不定状态,但查阅真值表,无论此时R端电位高或低,输出Q都为低电平,稳定的使系统处于关机状态。

随着电容继续放电,I/O引脚POWER_CTL稳定为低电平,此时触发器引脚R=1,S=0,稳定维持输出Q为低电平,保证系统电源的稳定关断。

设计的改进

实际使用中发现,当更换供电电源时,触发器初始上电,D、CLK和R端下拉至地,保持稳定状态为0。而由于电容C1的充电作用,有可能使S=1,查阅真值表,当S=1,R=1时,输出Q为高电平,致使Q2导通,SHDN为高电平,打开系统。

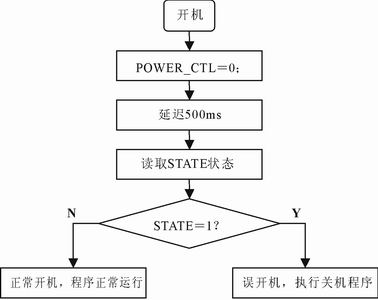

为了解决更换电源时系统有可能自动开机问题,在系统上电程序开始执行并延迟500ms后重新读取STATE状态。初始阶段,Q1导通,STATE状态为低电平。而随着RC网络的延迟时间过后,S端电位由高电平变为低电平,Q1由导通变为截止,STATE状态由低电平重新转换为高电平。MPU延时后读取的STATE如果为高电平,则认为是误开机,程序执行关机程序,重新关闭系统电源。如果STATE仍为低电平,则确认是开机指令,程序正常执行。因此要求用户在开机时,按下S1并保持500ms以上。

MPU开机初始化程序流程如图2所示。

图2 MPU开机初始化程序流程图

结语

本电路相对其它电路结构简单,使用器件较少。配合软件处理,能够实现自动开/关机功能,对一般应用来说是较好的选择。

上一篇:一种神经信号调理电路的设计

下一篇:一种简易的自动开/关机电路设计

推荐阅读最新更新时间:2023-10-12 20:11

很全的电子元器件基础知识讲义

很全的电子元器件基础知识讲义 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号