0 引 言

光纤通信具有高速、大容量、长距离、低损耗、强抗干扰能力等特点,适合多种综合数据业务,是未来宽带网络的发展方向。我国的信息化建设正处于大发展时期,对光纤、光缆、高速光电器件及光传输设备的需求量很大,市场前景广阔,国内已建的2.5 Gbit/s(STM-16)SDH骨干网已经不能满足爆炸增长的信息需求,10 Gbit/s(STM-64)光传输系统成为我国近期产业化的重点。为了提高信道利用率,使多个信号沿同一信道传输而互相不干扰,高速复接器的设计对于高速光纤传输系统的实现至关重要。复接器的速度是影响整个光纤传输系统速度的一个关键因素。在10Gbit/s速率以上,复接电路涉及到一系列高速电路,在电路设计、测试、封装等方面都有很大的挑战性。

CMOS工艺具有价格便宜、集成度高、功耗低的特点。随着CMOS工艺的发展,器件特征频率大幅提高,采用CMOS工艺实现超高速集成电路成为可能。本文给出了使用CMOS工艺设计的单片集成超高速4:1复接器。

1 系统结构

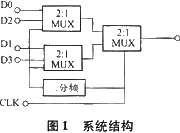

复接器有串行、并行、和树形3种基本结构。N:1串行结构复接器结构简单,容易实现,但是工作在高速状态的器件多,它的速度受到了限制。由于需要大电流来支持高速度,所以串行结构的电路功耗较大。N:1并行结构复接器需要N个不同相位的时钟,N个相位准确的时钟的产生难度高,对于N≥4的高阶复接器,因为或门的扇入系数大,导致或门速度降低,所以工作速率的大幅度提高比较困难。树形结构复接器中工作在最高速率的电路只有最后一级2:1复接器和第1级分频器,其他电路均工作在较低速状态,所以功耗比较小。但电路规模在3种结构的电路中最大。树形结构复接器的速度取决于最后一级2:1复接器的速度,所以通过优化最后一级2:1复接器的电路参数可以获得很高的比特率。本次设计选用树形结构,系统结构图如图1所示。

图1中树形结构的4:1复接器是由3个2:1高速复接器级联而成,结构如图2所示。

主要模块包括MS-FF(主-从D触发器)、MSM-FF(主-从-主D触发器)、2:1选择器、时钟和数据的输入缓冲电路。为了获得足够大的相位裕度,最理想的状态是使数据选择器在时钟的正半周期时在D1(或D2)的中心采样,而在时钟的负半周期时在D2(或D1)的中心采样,这样就可以避免由于时钟的细小误差而产生毛刺或逻辑错误,也给分频器的设计创造了有利条件。为了达到这种理想状态,两个并行通道的输人数据(D1和D2)速率相同,D1经过MS-FF到达选择器,而D2经过MSM-FF到达选择器,其中MSM-FF和MS-FF均工作在时钟的上升沿。这样在选择器的输入端的两路数据之间将产生半个时钟周期的延时差。

本设计复接器速度达到了10 Gbit/s,系统中最低时钟频率都达到2.5 GHz,因此有必要讨论系统时钟分配的问题。时钟布线采用驱动器树,在分配路径中放置驱动器来控制时钟偏差。为了满足树的对称性,在分配树有最高优先权的地方通常有必要提供一层互连金属层。如果做不到这一点,可以用不同的互连层来设计树,但布线路径应当相同。树的每个端点处尽可能采用电气上相同的接收或驱动电路。

2 主要单元电路结构

基本的单元电路如锁存器、选择器、时钟的输入缓冲器等都使用了源极耦合场效应管逻辑(SCFL)电路。SCFL电路的传输延时受晶体管特性(如阈值电压等)的影响较小,这有利于减小由晶体管的非线性导致的时钟信号的畸变。同时,SCFL逻辑电路输出信号摆幅大,输入的负载电容小,所以容易提高工作速度,与CMOS逻辑相比,在高速的条件下也有低功耗的优势。

2.1 锁存器和D触发器

输入级的差分对起着采样的作用,反馈级的差分对则起着锁存的作用,两者分别在时钟的上升沿和下降沿工作。减小锁存器输出端的负载电容可以有效地提高锁存器的工作速度。因此,通过调节输入级差分对管和反馈级差分对管的栅宽的比值,可以调节锁存器工作的最佳频率范围。将两个锁存器级联即成D触发器,如图3所示。

2.2 选择器

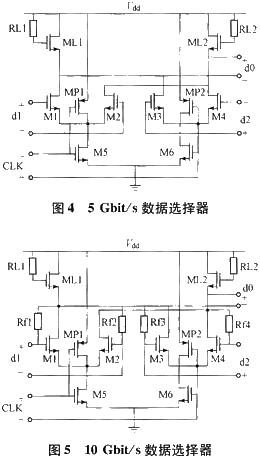

复接单元的选择器是整个设计速度提高的一个难点。图4和图5分别是速度为5 Gbit/s和10 Gbit/s的两个选择器。

在电路中采用了有源电感对电路频率进行补偿,以提高选择器的工作速度和驱动能力。考虑到电源电压比较低,选择器电路中没有使用电流源。通常在设计中会在数据选择器后加一级源极跟随器,以减小输出管的负载电容,调整直流电平并为后级电路提供驱动。但由于0.18μm CMOS工艺的供电电压只有1.8 V,如果使用源极跟随器,会使得信号电平下降过多而无法与后级电路电平匹配,因此设计中省略了源极跟随器。确定PMOS管和NMOS管恰当的尺寸关系,保证选择器正常工作。栅极直接与时钟信号相连的两个PMOS管和两个NMOS管组成了时钟控制开关。选择合适的工作点使得在时钟信号周期的正、负半周,时钟控制开关正常切换两组数据信号(d1和d2)。这样经过缓冲到达的时钟信号就能准确控制时钟开关,在一个周期的正、负半周分别选出经过MS-FF到达的信号d1和经过MSM-FF到达的信号d2。

在整个复接系统中,最后一级复接单元的速度起决定性作用,所以在图6的选择器中采用了负反馈扩展了系统的带宽。

2.3 数据输出缓冲器

本设计的输出级采用了普通差分放大器和容性耦合电路组合而成的宽带放大电路,如图6所示。复接器的多级输出缓冲得到了大的电流驱动能力,用来通过焊盘驱动片外50 Ω负载。

3 电路仿真和版图设计

本次设计采用TSMC 0.18μm CMOS工艺。电路仿真在Agilent公司的ADS上实现。图7是4路2.5 Gbit/s的随机信号复接成一路10 Gbit/s信号的输出信号眼图。图8是4路3.375 Gbit/s的矩形脉冲信号复接成一路13.5 Gbit/s信号的输出信号眼图。

因为本次设计采用的是SCFL电路,所以应充分发挥全差分结构的优势,电路版图尽量设计得对称,以保持电路平衡、抑制共模信号和工艺参数波动带来的不利影响。在设计中主要考虑高频线走向、连线长度和宽度、版图对称以及芯片面积的折中。特别在分频器版图设计中采样部分和保持部分尺寸不同,合理布局使版图对称,并且使各部分连接容易,同时还要使反馈线尽可能短。整个芯片的版图如图9所示。

复接器芯片在TSMC 0.18μm CMOS工艺下进行后仿真,图10是复接器输出数据为10 Gbit/s的后仿真眼图,可以看出眼图较为清晰,张开度较大。

4 结束语

采用TSMC 0.18μm CMOS工艺设计的树形结构SCFL电路的复接器实现了10 Gbit/s的高速数字复接功能,最高仿真速度达到13.5 Gbit/s。

感谢东南大学射频与光电集成电路研究所提供的工艺库支持。

上一篇:无锁相环电压全周期过零检测电路的仿真与设计

下一篇:基于SystemView的调频信号的调制解调仿真

推荐阅读最新更新时间:2023-10-12 20:13

【得捷电子Follow me第2期】日历时钟项目代码及依赖库

【得捷电子Follow me第2期】日历时钟项目代码及依赖库 电子电路识图、应用与检测 (韩雪涛)

电子电路识图、应用与检测 (韩雪涛) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号