干货 | 实例分析AC/DC 降压转换器电路讲解

最新更新时间:2021-09-04 03:38

阅读数:

诸如智能电表或者功率监控器的离线设备都有一些要求10W以下非隔离DC电源的电子元件。到目前为止,通过一个AC电源提供低功耗DC电源的唯一实用方法仍然是在整流器后面使用一个效率极低、未经调节的电阻/电容分压器,或者一个难以设计的反向DC/DC转换器。

MOSFET 技术的一些进展以及创新的磁滞降压控制器栅极带来了一种超低成本DC电源。

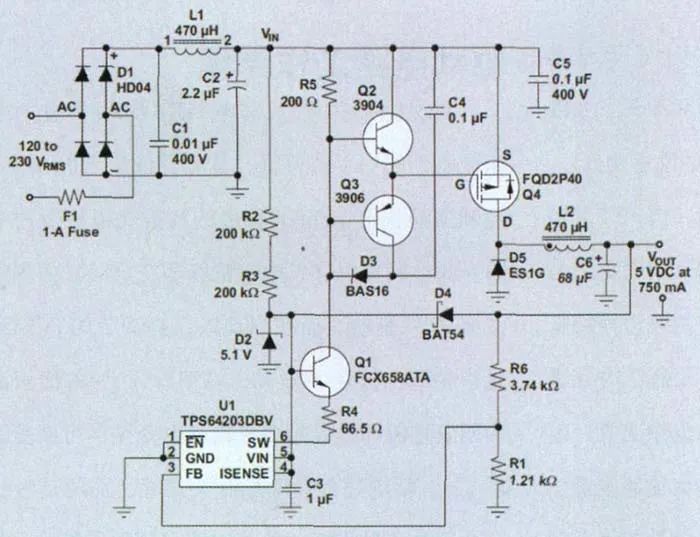

图 1 显示了完整的转换器。整流器电路使用一个标准、快速开关整流器二极管桥接 (D1) 和一个LC滤波器(L1和C2),我们将对其余组件进行更加详细的介绍。

图 1 AC/DC 降压转换器电路

基本降压转换器

TPS64203是一款磁滞降压转换器,专为驱动高端pFET 而设计,拥有最小导通和断开开关时间要求。传统的磁滞转换器有随负载电流变化的开关频率,与其不同的是,最小导通和断开时间在转换器以高输出功耗电平在连续导通模式下运行时,从根本上控制开关频率。TPS6420x 系列中的其他一些转换器可主动避免在声频范围内进行开关操作,从而有效地获得最大导通和断开时间。TPS6420x系列起初是为电池供电型应用而设计,拥有1.8V~6.5V的输入电压范围,以及非常低的静态电流(最大为 35 μA)。在启动期间,TPS64203被齐纳二极管D2以及高压电阻R2和R3偏置。5V电压上升以后,肖特基二极管D4允许5V输出驱动控制器。

功率FET Q4必须具有足够高的VDS电压额定值,以使其不会被输入电压损坏,同时还要有足够高的电流额定值以处理IPMOS(RMS) = IOUT(max) ×√Dmax。它的封装还必须能够驱散PCond = (IOUT(max) × √Dmax)2 × RDS(on)。一般来说,高压P通道FET有一个过大的栅极电容或者导通/断开时间,过高的漏-源电阻 (RDS(on)),过大的阈值电压 (VTH),以和/或制造图1所示实际电路时的过高成本(即足够的成本效益)。由于230VRMS + 10%容差的高压线来自350VPK AC线,因此FET、滤波器和输入电容需要根据400V设定额定值。

FQD2P40相对较新,即400V P通道MOSFET。利用10V栅极驱动的5.0Ω RDS(on) 以及小于13nC的总选通电极充电,借助于由Q2、Q3、C4和D3组成的创新驱动电路,该FET可轻松地通过控制器开关拥有比老式FET相对更少的导电和开关损耗。我们选择转换器的整流肖特基二极管D5,因为它拥有可阻止输入电压的电压额定值、稍高于输出电压的峰值电流额定值,以及IDiode(Avg) =(1 – D) × IOUT(max)的平均电流额定值。利用Dmax 5 V/120 V = 0.04 以及如此低的输出功率,峰值电流额定值和功耗在两种开关中都不成问题。

降压功率级的LC滤波器如TPS6420x系列产品说明书中介绍那样设计。利用高于输出电压的输入电压,所有TPS6420x控制器将运行在最小导通时间模式下。方程式(1)计算高线压下的建议降压转换器电感,其假设电感纹波电流系数的 K=0.4。

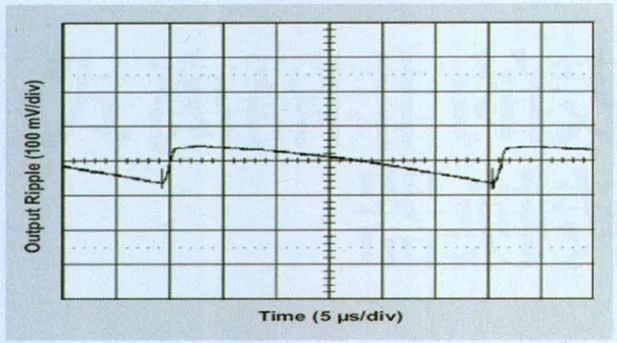

相对较高的K值最小化了电感值,并且经证明是可以接受的,因为这种特殊应用的稳态输出纹波要求小于0.02 × VOUT,即高负载时的100mVPP。磁滞后,TPS6420x控制器一般在输出电压有一些纹波时工作效果最佳,建议使用至少 50mΩ ESR的输出电容可产生ΔVPP(ESR) = ΔIL × RESR的纹波电压,其一般远超出电压纹波的电容分量。图2显示了该应用测得纹波。

图 2 VIN=250 VDC 和 IOUT=500mA 的输出纹波

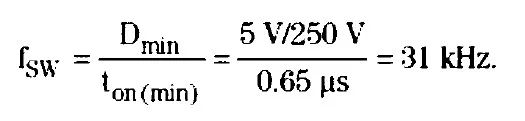

由于 TPS64203为磁滞型,因此在其运行在脉冲频率模式下时,其输出电压在更低输出功率下将会有更高的纹波。测得转换器的工作频率约为 32 kHz,其与下列预计值一致:

工作原理

双极型晶体管Q1和电阻R4及R5构成一个恒流驱动的电平位移器,其允许低压 TPS64203控制器操作由Q2和Q3构成的离散式栅极驱动电路。同控制器一样,电平位移器在启动时由齐纳二极管D2驱动,而在启动以后经调节的5V则通过肖特基二极管D4驱动。功率FET Q4的栅极必须刚好过驱动,以为要求输出电流提供可接受的RDS(on)。驱动过多会增加开关损耗,而驱动过少又会增加传导损耗。检查一些实验和误差后,我们选择了 VGS ≈12 V。

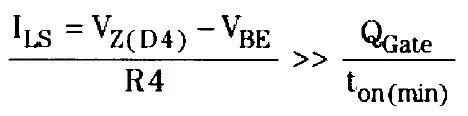

电容C4和二极管D3对驱动电路的功能至关重要。通过选择电阻R5来将12V栅极驱动电平设置在整流器输出电压以下。二极管D3将电容C4限定在这一电平。特别是,当U1的开关引脚输出一个低信号来开启功率FET时,信号被电平位移到Q3的基极。晶体管Q3开启,并快速地将Q4的栅—源电容CGS充电至 12V。如果没有C4和D3的话,关闭Q4会让Q3成为一种漏极接地的昂贵的高压双极型晶体管。当U1的开关引脚输出一个高信号来关闭功率FET时,该信号被电平位移至Q2的基极。Q2开启,有效地将Q4的栅极与输入电压连接。在没有起到本地电源作用的电容C4的情况下,晶体管Q2和Q3无法提供快速(且因此而高效地)上拉或下拉Q4栅极电容所必需的快速电流峰值,注意到这一点很重要。另外,由R4设定的电平位移器电流ILS必须足够高,以在ton(min) 期间移动Q4的栅极电荷QGate。也就是说:

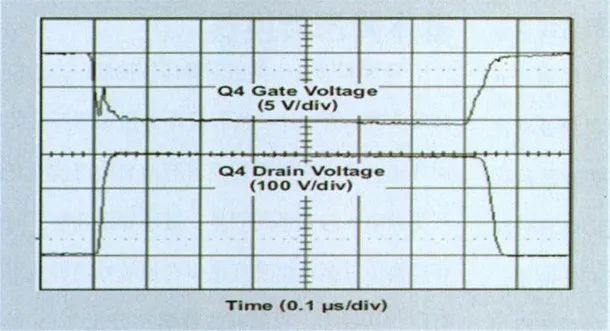

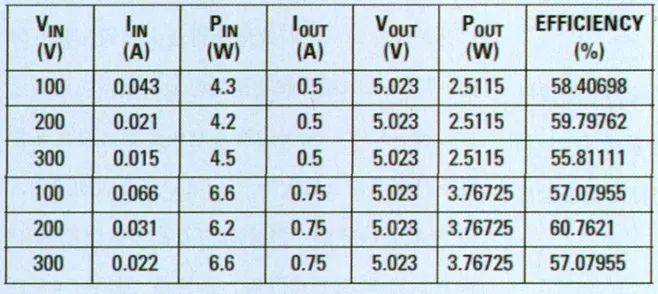

电容C4值设定大于Q4的栅极电容,但其必须足够小,以便在更短控制器最小导通与断开时间期间能够得到再充电。图3显示了300V和500mA负载输入电压下,一个开关周期的栅极和漏极导通/断开时间。表1显示了测得的转换效率。

图 3 一个开关周期的Q4栅极和漏极电压

表 1 测得的转换效率:

电流限制与软启动

在许多低压应用中,TPS6420x使用一个高端限流电路,旨在将安装在VIN和 ISENSE引脚之间的电流检测电阻的压降同基准参考电压进行对比。如果检测电阻的电压超出该电压,则电路关闭开关,从而实现逐脉冲电流限制。高压应用中, ISENSE引脚上没有过电压时无法使用限流电路,因此ISENSE引脚高位连接至VIN。图1所示电路没有电流限制,推荐使用高端保险丝来提供短路保护。

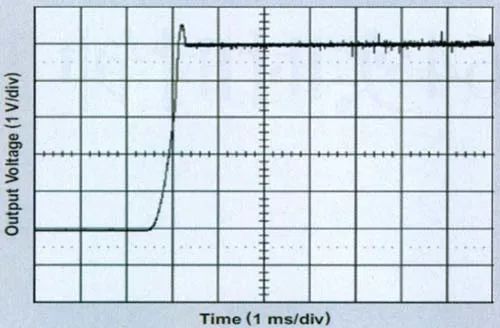

在一些典型的启动应用中,TPS64203限流值慢慢上升,以提供限流的受控软启动。在这种应用中,限流电路和软启动均无效;因此,启动浪涌电流会很大,而输出电压会稍稍过冲,如图 4 所示。

图4 VIN=300V时10Ω负载启动

结论

使用一个电平转换器和栅极驱动器以及一个局部电源可以实现使用一个低压降压转换器通过AC电源来提供DC电压,使用一个简单的电路在没有变压器的情况下就可以获得近60%的转换效率。这种电路也可以用于DC/DC转换,其输入 DC电压高于TPS6420x 的最大额定值。

在公众号内回复您想搜索的任意内容,如问题关键字、技术名词、bug代码等,就能轻松获得与之相关的专业技术内容反馈。快去试试吧!

由于微信公众号近期改变了推送规则,如果您想经常看到我们的文章,可以在每次阅读后,在页面下方点一个「赞」或「在看」,这样每次推送的文章才会第一时间出现在您的订阅列表里。

或将我们的公众号设为星标。进入公众号主页后点击右上角「三个小点」,点击「设为星标」,我们公众号名称旁边就会出现一个黄色的五角星(Android 和 iOS 用户操作相同)。

聚焦行业热点, 了解最新前沿

敬请关注EEWorld电子头条

https://www.eeworld.com.cn/mp/wap

复制此链接至浏览器或长按下方二维码浏览

以下微信公众号均属于

EEWorld(www.eeworld.com.cn)

欢迎长按二维码关注!

EEWorld订阅号:电子工程世界

EEWorld服务号:电子工程世界福利社

推荐帖子

京公网安备 11010802033920号

京公网安备 11010802033920号