半导体器件包含数以亿计在极端温度和恶劣环境下工作的晶体管,因此,许多器件不能正常工作或寿命有限也就不足为奇了。有些器件永远出不了实验室,还有很多器件死在晶圆厂里。人们希望大多数放到产品中的器件都能存活下来,直到它们过时,但很多事情可能会导致它们走不了那么远。即使是运行正常的器件也可能受到损害,以至于无法提供正确的结果。

常见危害及其原因不可胜数。它们通常分为几个类别,下面将对此进行详细说明。

死于设计

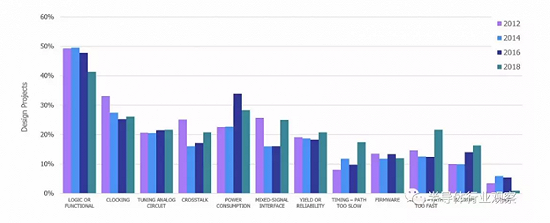

根据Mentor/Wilson的功能验证研究,2018年,只有26%的ASIC实现了一次流片成功,低于此前的研究结果。成功率低的部分原因是新技术节点增加了尚未完全理解的挑战。已经存在了一段时间的问题被纳入到工具和流程中,从而使那些已知的问题不再是威胁。然而,2018年,混合信号接口、串扰、时序和IR drop,这些已知的问题导致了重新流片的增加。

图1:导致重新流片的ASIC缺陷类型。 (来源:Wilson Research Group和西门子Mentor事业部,“2018年功能验证研究”)

Synopsys的产品经理Kenneth Chang表示:“一些客户的芯片失败,是因为他们的设计过程更加特殊。一位客户进行了block级功耗分析,然后进行了整合。 他们认为可以在这个阶段修复问题。但问题是不可修复的,芯片已经失败了。芯片失败的原因在于旧方法不再适用于新的先进技术。”

失败不一定是不能正常工作。Cadence公司Digital和Signoff部门产品管理总监Jerry Zhao表示:“失败可能是因为它没能达到性能目标,如果芯片的运行速度比预期低10%,那么它在市场上可能没有竞争力。”

电源正在成为一项挑战,特别是当电源在片上的时候。Arm公司物理设计部门高级解决方案营销经理Lisa Minwell表示:“电源供电网络(PDN)是一个分布式RLC网络,可以分为三个部分:片上、封装和电路板。片上需要更快的时钟频率、更低的工作电压、更高的晶体管密度。虽然先进的finFET技术已经实现了持续的性能提升,增加的功率密度使IR drop闭合成为一项挑战。准确建模和最小化电压裕度是平衡电源效率和鲁棒性的关键。”

但裕度可能是悲观的,从而限制了竞争力。尽管发现了问题,但一些公司还是冒险继续前进。Kenneth Chang表示:“一家大型存储器公司的流片出现了已知的大量IR drop问题。只要看上去不太糟糕,他们就会流片,因为日程表对他们来说更重要。客户正在学习,在这种情况下,他们的芯片并没有失败。如果他们没有失败,他们就会继续做正在做的事情。当他们到达更先进的节点时,他们会更加被指标驱动,并且需要执行EMIR分析。”

越来越多的问题也开始同时出现。例如,功率、IR drop、发热、时序、电迁移都是相关的,但是对于其中大部分问题的分析是分开进行的。Jerry Zhao表示:“电源噪音是一个问题。供电电压正在下降,同时用户希望获得更高的性能。你无法从电池获得太多的驱动功率,或许850 mV,但你仍然想要3GHz的性能。电源噪声会产生重大影响,特别是当裸片有变化的情况下,这种(噪声)会随着时间和位置而变化。因此,不同位置的同一电池可能会因电压下降而失效,从而导致时序延迟。你必须在电压下降的背景下分析电池,并进行静电电压感应时序分析。有些路径对电压变化非常敏感。”

随着问题得到更好的理解,工具可以进行更好的分析,并且可以使用设计方法来规避问题。Moortec公司营销副总裁Ramsay Allen解释道:“复杂性导致了更大的功率密度,而这反之又在芯片内部产生了局部热点。栅极密度的增加还会导致供给电路的电源电压下降更大。在整个设计过程中,高精度的温度传感器和电源监控器使系统能够管理和适应这些条件,通过提供热管理和供电异常检测的解决方案,提高器件的可靠性和优化性能。这一点在数据中心和人工智能设计中尤为重要,在这些设计中,性能要求的提高使设计在温度和电压方面承受了巨大的压力。”

死于制造

半导体器件的制造涉及到测量仅几纳米的结构。作为参照,人类DNA链直径为2.5nm,而人头发直径则为80,000至100,000nm。一粒尘埃可以摧毁晶圆片上的几个裸片。如果裸片的尺寸变大,随机失效的可能性就会增加。对于成熟的工艺节点,产率可能在80%到90%之间。然而,对于较新的节点,产率可能大大低于50%,尽管实际数字是严格保密的。

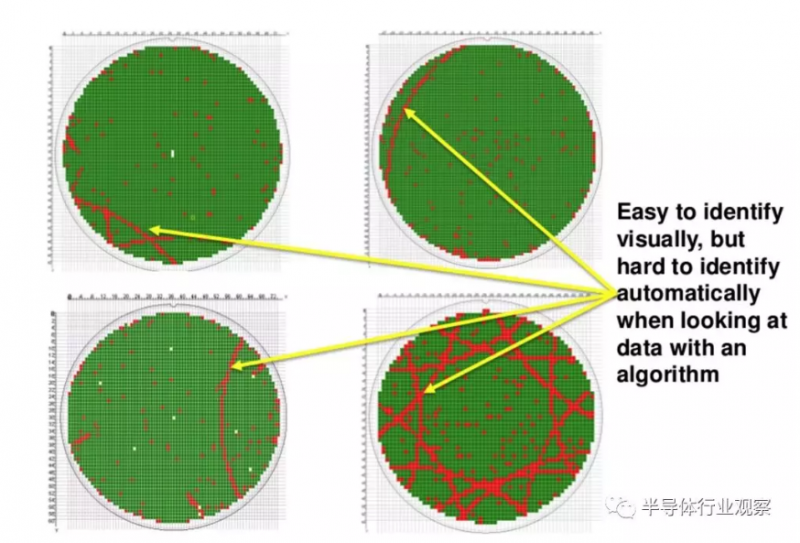

图2. 晶圆缺陷图案。(来源:Marvell Semiconductor,ITC 2015)

即使裸片没有受到灾难性的影响,也不能被认为是可操作的。制造步骤不完善,哪怕一个原子的工艺变化也会产生显着的差异。虽然这可能不会对设计的某些部分产生影响,但如果工艺变化恰好与关键时序路径吻合,则可能会使器件不符合规格。

ANSYS公司ESD/heat /reliability产品经理Karthik Srinivasan解释说:“随着设计逐渐演变成采用先进封装的深亚微米技术,现有的仿真工具和设计方法无法很好地反映变化及其对可靠性的影响。这会导致设计流程出现漏洞,从而导致一些失败。”

设计流程越来越多地允许在开发早期就考虑到变化,以最大限度地减少其影响,而冗余等设计技术可以减少需要丢弃的“几乎可以工作”的芯片的数量。“几乎可以工作”的芯片对于大型存储器阵列非常常见。分类(Binning)是经常用于处理器的另一种做法,以较高频率运行的优良器件可以以较高价格出售,而那些只有在低频时才能成功工作的器件则以折扣价出售。

测试的作用是找出哪些裸片功能完全。那些临界的裸片通常会被丢弃,但一些无功能的裸片确实存在漏检,并最终成为产品。

死于触摸

杀死芯片有多种方法。请考虑,施加在芯片外部的0.5V电压在1nm的介质上产生0.5mV/m的电场。这足以导致高压电弧。现在考虑一下当你触摸芯片的引脚时会发生什么。

Jerry Zhao解释说:“通常情况下,它是一个高电压,根据引脚的接触方式,会有不同的模型,如人体模型或电荷分布模型(CDM)。这些模型定义了电流如何流入引脚。这是一个随时间变化的波形。”

通常,芯片会包含静电放电(ESD)保护。ANSYS公司的Srinivasan指出:“对于封装内的单个裸片,他们的目标是2kJ这样的标准。多芯片解决方案,例如HBM,标准略低。使用2.5D或3D IC的一个原因是为了性能,而ESD则是性能的障碍。你试图最小化ESD,甚至在这些Wide I/O接口或任何类型的多芯片接口通道上消除它,这意味着你无法按照你针对单芯片的相同标准对每个芯片进行真正的测试。它们必须经过更专业的测试,因为它们的ESD保护很小,或者可能没有ESD保护。”

即使在运行期间,ESD事件也可能导致问题。Arm公司的Minwell说:“在便携式电子产品中,ESD可以导致许多类型的软错误。在ESD事件期间,电源供电网络(PDN)上可能会引起噪声,原因在于某些IC(振荡器IC、CPU和其他IC)的灵敏度,或是PDN的场耦合。”

死于关联问题

Helic公司营销副总裁Magdy Abadir说:“软错误可能以多种方式发生,如果错误是系统上的,它可能会使芯片看起来好像不工作。3D IC正在增加对电磁感应设计方法的需求。这是因为产生的功率密度更高和堆叠层数的增加,这就增加了产生天线的风险,它会放大整个设计过程中产生的磁场。”

电力供应不足也会造成问题。Jerry Zhao说:“芯片的功能取决于晶体管开关。这取决于供电电压。如果它在1V下工作,它可能会下降10%或20%并仍然可以正常工作。但时序会有所不同,因此可能需要降低最大时钟频率。”

由于电压降低,电路更容易受到噪声的影响。ANSYS公司半导体事业部首席技术专家Norman Chang说:“电磁干扰(EMI)是芯片向环境发出的噪声。噪声源来自有源电路,它会在电源/地线和信号线上产生电流。电源线/地线将通过封装到PCB,如果它看到封装或PCB上有天线结构,就会引起空气辐射,然后通过天线结构辐射到环境中产生干扰。”

但出去的东西也会进来。Norman Chang表示:“电磁敏感性(EMS)是人们不得不担心的新问题。能量注入测试是从150kHz开始注入1W能量,一直到1GHz。在每个频率,你会向系统注入1W的能量。如果你没有足够的保护,就会破坏沿路径进入芯片的电路。我们的目标不是破坏芯片,而是测试这种噪声是否会影响电路。或者引脚上的电压可能过高,如果电压太高,就会产生过电应变(electrical over-strain)。”

死于操作

此时,芯片已经到达现场并被认为是可操作的。Microchip模拟电源和接口部门首席产品营销工程师Fionn Sheerin说:“可靠性是个大问题。在很多情况下,糟糕的热设计并不会导致瞬间灾难性的故障,甚至不会导致产品平庸。但器件寿命会变短。观察layout中的热点或最佳layout实践以及良好的层次规划可能会产生不同的效果。这也是验证和可靠性测试真正重要之处,也是汽车应用中的功能安全问题。”

西门子Mentor事业部的产品营销总监Joe Davis对此表示赞同:“发热带来的问题不仅仅是手机在口袋里变热。它会导致晶体管和它们之间的连接退化。这可能会影响性能和可靠性。”

热量产生于两个来源。Jerry Zhao表示:“首先是路由层。这是与导线中的电流有关的热量。模拟电路比数字电路有更大的电流。因此,模拟设计者不得不担心温度过高是否会使连线融化。第二个来源是晶体管。当我们迁移到finFET时,一个新的现象是自热。热量沿着弱电阻路径运动,从晶体管的鳍片垂直发散。这就增加了连线中的热量。”

当大电流和热量聚集在一起时,电迁移效应会慢慢损坏连线。类似地,诸如负偏置温度不稳定性(NBTI)之类的物理效应,当你有很大的电荷时,会对器件造成压力,如果持续足够长的时间会导致永久性损坏。

结论

芯片在恶劣环境中运行,半导体行业已经学会了如何应对这些挑战。但是随着制造尺寸变小以及采用新的封装技术时,新问题出现了。有时,这些新效应会导致器件失败。但从历史上看,行业很快就学会了要么规避新问题,要么将问题最小化的方法。

上一篇:英特尔CPU供货短缺,PC厂加码冲标案

下一篇:更直观,更高效,意法半导体STM32CubeMX MCU引入多面板GUI

推荐阅读最新更新时间:2024-05-03 03:21

图解入门——半导体制造设备基础与构造精讲

图解入门——半导体制造设备基础与构造精讲

京公网安备 11010802033920号

京公网安备 11010802033920号