——翻译自DDC官网

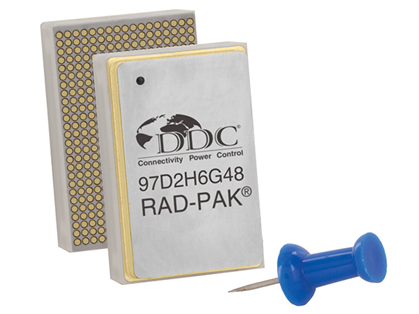

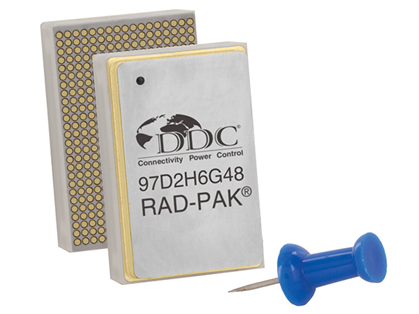

美国数据设备公司(DDC)推出首个用于太空领域的CCGA封装的抗辐射DDR2 SDRAM,此款产品是对DDC高密度空间级陶瓷密封存储器的最新补充,其中包括闪存NAND/NOR、SDRAM、SRAM和EEPROM解决方案。新款DDR2(97D2H)在一个紧凑的CCGA封装中提供高达8GB的SDRAM,为长期使用和易于设计提供了一个高度可靠和灵活的内存解决方案。密封陶瓷封装的辐射容错剂量TID(>100 krad orbit/mission dependent),以及在单粒子效应中(无闩锁效应[1])提供了出色的辐射耐受能力,而通用封装提供多种密度和数据宽度选项,以简化电路板设计、系统集成和错误纠正。

特点:

·高性能

提供更高速度的SDRAM (400mhz),以增加内存吞吐量和最大限度地提高应用程序效率

·高可靠性

密封陶瓷CCGA封装,使用时间长、易于设计;

出色的辐射耐受容错量(>100 krad** dependent on mission)和单粒子效应(无闩锁效应);

完整的模具批次可追溯性和模具批次TID测试可确保每个零件的一致,可靠的性能;从“工程类”到“飞行类”的筛选流程提供了多种选择,使用户的预算任务需求上得到相应的匹配;

灵活性的设计/易用性

适用于多种密度和数据宽度的通用紧凑型封装,简化了电路板设计和系统集成;

在单独的CCGA封装中最多可达8GB,占用空间小(1.1英寸x 0.717英寸)和325 in);

宽数据总线选项(x8, x16, x32, x48, x64, x80),用于简单的连接到抗辐射的 FPGA, ASIC和处理器,支持实现各种纠错方案;

“DDC的密封陶瓷DDR2代表了下一代空间级SDRAM,提供了最高辐射容错(>100 krad),同时具有广泛的数据总线选项。”——DDC业务经理Dan Veenstra介绍。

[1] Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流;随着IC制造工艺的发展, 封装密度和集成度越来越高,产生Latch up的可能性会越来越大;Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路;Latch up 产生的过度电流量可能会使芯片产生永久性的破坏, Latch up 的防范是IC Layout 的最重要措施之一。

关键字:DDC SDRAM 陶瓷封装

引用地址:

首款应用于太空领域的陶瓷密封DDR2内存问市

推荐阅读最新更新时间:2024-11-06 07:17

DRAM SRAM SDRAM内存精华问题汇总

问题1:什么是DRAM、SRAM、SDRAM? 答:名词解释如下 DRAM--------动态随即存取器,需要不断的刷新,才能保存数据,而且是行列地址复用的,许多都有页模式 SRAM--------静态的随机存储器,加电情况下,不需要刷新,数据不会丢失,而且一般不是行列地址复用的 SDRAM-------同步的DRAM,即数据的读写需要时钟来同步 问题2:为什么DRAM要刷新,SRAM则不需要? 答:这是由RAM的设计类型决定的,DRAM用了一个T和一个RC电路,导致电容会漏电和缓慢放电,所以需要经常刷新来保存数据 问题3:我们通常所说的内存用的是什么呢?这三个产品跟我们实际使用有什么关系?

[电源管理]

高功率LED封装比较:K1导线架与陶瓷封装

随着单位 亮度 不断增加, LED 在照明领域的应用愈来愈广。为了持续增加LED的亮度,提高单颗磊芯片的面积以及使用 功率 势不可免,但如此一来亦拌随着高热量的产生。 在陶瓷封装尚未普及前,以Lumileds所提出的K1封装形式,在1W(或以上)的LED的领域己成为大家所熟知的产品。但是随着市场对产品特性要求的提升,封装厂仍不断地改良自家产品。而利用薄膜平板陶瓷基板 (DPC Ceram ic Substrate) 再加上molding直接制作 光学 镜片 的陶瓷封装方式的引进,使得高功率 LED封装 产品又多了一种选择。然而这几年的实际产品验证,让国际大厂不约而同地往陶瓷封装这个方向靠拢,其中的原因值得仔细思考。

[电源管理]

STM32学习之:FMC-扩展外部SDRAM

参考资料:《STM32F4xx 参考手册 2》、《STM32F4xx 规格书》、库帮助文档《stm32f4xx_dsp_stdperiph_lib_um.chm》。 关于 SDRAM 存储器,请参考前面的“常用存储器介绍”,实验中 SDRAM 芯片的具体参数,请参考其规格书《IS42-45S16400J》来了解。 1、 SDRAM 控制原理 STM32 控制器芯片内部有一定大小的 SRAM 及 FLASH 作为内存和程序存储空间,但当程序较大,内存和程序空间不足时,就需要在 STM32 芯片的外部扩展存储器了。 STM32F429 系列芯片扩展内存时可以选择 SRAM 和 SDRAM,由于 SDRAM 的“容量/价格”比较

[单片机]

S3C2440通过J-Link直接往SDRAM中烧程序

由于S3C2440核心板以及主板均为实验室自制,使用友善之臂的H-Jtag不能操作,因此使用J-Link来测试焊接完的核心板是否工作正常 步骤: 1. 连接好核心板,并开电 2. 使用J-Link自带的J-Link commander(安装J-Link时已经安装了) 启动J-Link commander,如果没检测到CPU,执行usb命令连接JLink,注意,S3C2440 CPU的ID是:0x0032409D 3. 在J-Link commander下载运行特制的程序 对于S3C2410、S3C2440处理器,它们内部有4K的SRAM,当使用Nor Flash启动时,地址为0x40000000;当使用Nan

[单片机]

DDR SDRAM在嵌入式系统中的应用

引 言 很多嵌入式系统,特别是应用于图像处理与高速数据采集等场合的嵌入式系统,都需要高速缓存大量的数据。DDR(Double Data Rate,双数据速率)SDRAM由于其速度快、容量大,而且价格便宜,因此能够很好地满足上述场合对大量数据缓存的需求。但DDR SDRAM的接口不能直接与现今的微处理器和DSP的存储器接口相连,需要在其间插入控制器实现微处理器或DSP对存储器的控制。 随看密度与性能的不断提升,现场可编程门阵列(FPGA)已被广泛应用于各种嵌入式系统中。而且,现在很多的FPGAs都提供了针对DDR SDRAM的接口特性:其输入输出引脚都与SSTL一II电气特性相兼容,内部提供了DDR触发器、锁相环等硬件资

[单片机]

MINI2440裸机实验之SDRAM

程序编写 本次实验将实现初始化SDRAM并将程序自身复制到SDRAM中然后跳转至SDRAM中继续执行流水灯。 依然是在上次程序的基础上进行修改,本次需要修改的文件包括”start.S”和”Makefile”,修改后的文件内容如下: /* start.S */ .text .global _start _start: #define MDIV 0x7f 12 #define PSDIV 0x21 ldr r0, =0x53000000 mov r1, #0x00 str r1, /* disable the watchdog timer */ bl mpll_setup bl mem_setup

[单片机]

S3C2440裸机------SDRAM

1.配置内存控制器的寄存器 我们的S3C2440在访问SDRAM的时候,首先发出地址,然后内存控制器首先根据地址范围发出片选信号nGCS6,然后根据片选信号的类型得知是SDRAM,然后拆分地址为 bank地址,行地址和列地址,具体应该怎么把地址拆分成bank地址,行地址,列地址则由我们配置的SDRAM寄存器决定,然后开始读数据。 1.1BWSCON寄存器设置 由于我们的SDRAM只连接到了片选6上面,所以我们只看该寄存器的与6相关的几项,由于我们使用了两篇SDRAM组成32位的,所以DW6我们设置成10,WS6表示是否使用wait信号,wait信号是指如果内存芯片的速度很慢,当cpu发出读写命令之后,内存控制器开始驱动相关

[单片机]

使用Verilog实现基于FPGA的SDRAM控制器

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键词:SDRAM;控制器;Verilog;状态机

引言

---在基于FPGA的图象采集显示系统中,常常需要用到大容量、高速度的存储器。而在各种随机存储器件中,SDRAM的价格低、体积小、速度快、容量大,是比较理想的器件。但SDRAM的控制逻辑比较复杂,对时序要求也十分严格,使用很不方便,这就要求有一个专门的控制器,使系统用户能很方便地操作SDRAM。为此,本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制

[应用]

集成电路芯片封装技术 (李可为)

集成电路芯片封装技术 (李可为) CADENCE高速电路板设计与仿真:原理图与PCB设计

CADENCE高速电路板设计与仿真:原理图与PCB设计

京公网安备 11010802033920号

京公网安备 11010802033920号