摘要:通过使用Achronix Speedster7t FPGA中的机器学习加速器MLP72,开发人员可以轻松选择浮点/定点格式和多种位宽,或快速应用块浮点,并通过内部级联可以达到理想性能。

神经网络架构中的核心之一就是卷积层,卷积的最基本操作就是点积。向量乘法的结果是向量的每个元素的总和相乘在一起,通常称之为点积。此向量乘法如下所示:

图 1 点积操作

该总和S由每个矢量元素的总和相乘而成,因此s=a1b1+a2b2+a3b3+...本文讲述的是使用FP16格式的点积运算实例,展示了MLP72支持的数字类型和乘数的范围。

此设计实现了同时处理8对FP16输入的点积。该设计包含四个MLP72,使用MLP内部的级联路径连接。每个MLP72将两个并行乘法的结果相加(即aibi+ai+1bi+1),每个乘法都是i_a输入乘以i_b输入(均为FP16格式)的结果。来自每个MLP72的总和沿着MLP72的列级联到上面的下一个MLP72块。在最后一个MLP72中,在每个周期上,计算八个并行FP16乘法的总和。

最终结果是多个输入周期内的累加总和,其中累加由i_first和i_last输入控制。 i_first输入信号指示累加和归零的第一组输入。 i_last信号指示要累加和加到累加的最后一组输入。最终的i_last值可在之后的六个周期使用,并使用i_last o_valid进行限定。两次运算之间可以无空拍。

表 1 FP16点积配置表

表 2 FP16点积端口说明表

图 2 FP16点积时序图

其中,

那么,以上运算功能如何对应到MLP内部呢?其后的细节已分为MLP72中的多个功能阶段进行说明。

首先请看下图,MLP之间的进位链结构,这是MLP内部的专用走线,可以保证级联的高效执行。

图 3 MLP进位链

下图是MLP中浮点乘法功能阶段,其中寄存器代表一级可选延迟。

图 4 MLP乘法功能阶段框图

MLP72浮点乘法级包括两个24位全浮点乘法器和一个24位全浮点加法器。两个乘法器执行A×B和C×D的并行计算。加法器将两个结果相加得到A×B + C×D。

乘法阶段有两个输出。下半部分输出可以在A×B或(A×B + C×D)之间选择。上半部分输出始终为C×D。

乘法器和加法器使用的数字格式由字节选择参数以及和参数设置的格式确定。

浮点输出具有与整数输出级相同的路径和结构。MLP72可以配置为在特定阶段选择整数或等效浮点输入。输出支持两个24位全浮点加法器,可以对其进行加法或累加配置。 进一步可以加载加法器(开始累加),可以将其设置为减法,并支持可选的舍入模式。

最终输出阶段支持将浮点输出格式化为MLP72支持的三种浮点格式中的任何一种。 此功能使MLP72可以外部支持大小一致的浮点输入和输出(例如fp16或bfloat16),而在内部以fp24执行所有计算。

图 5 MLP浮点输出阶段框图

需要强调的是本设计输入和输出都是FP16格式,中间计算过程,即进位链上的fwdo_out和fwdi_dout 都是FP24格式。具体逻辑框图如下所示:

图 6 FP16点积逻辑框图

MLP内部数据流示意图:

图 7 FP16点积在MLP内部数据流图

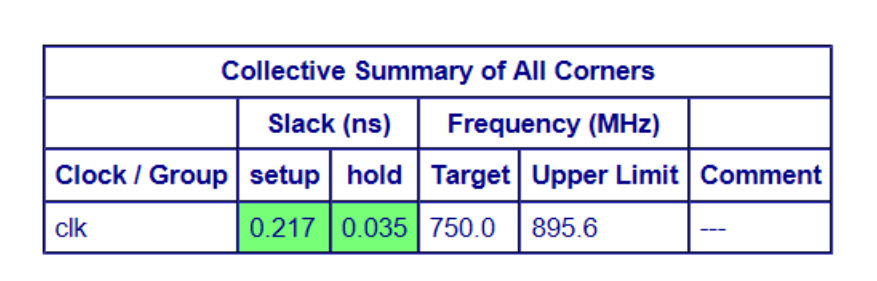

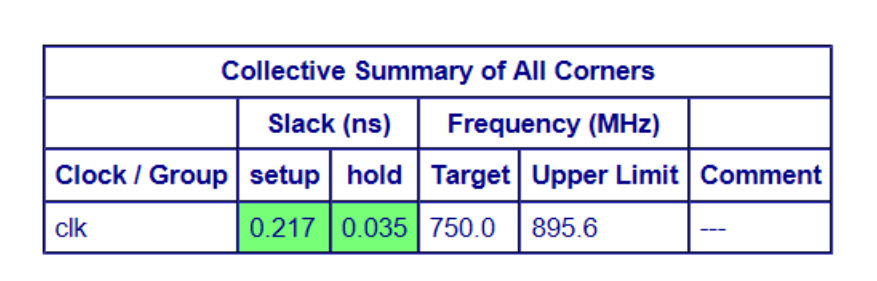

最终ACE的时序结果如下:

关键字:FPGA Achronix

引用地址:

技术文章:详解FPGA如何实现FP16格式点积级联运算

推荐阅读最新更新时间:2024-11-17 03:54

一种基于FPGA技术的虚拟逻辑分析仪的研究与实现

摘 要: 逻辑分析仪的现状、发展趋势及研制虚拟逻辑分析仪的必要性,论述了基于FPGA技术的虚拟逻辑分析仪的设计方案及具体实现方法,介绍了其中控制器的设计原理。将先进的FPGA技术引入硬制版的设计中,为研制PC虚拟仪器提出了一种新思路;充分利用硬件软化的思想,将仪器的诸多功能集成在软件中实现,利用面向对象、窗口等技术,实现了灵活、通用的虚拟仪器面板功能。

关键词: 虚拟仪器 虚拟逻辑分析仪(FVLA)现场可编程门阵列(FPGA)面向对象技术 控制器

电子技术的迅速发展从客观上要求测试仪器向自动化及柔性化方向发展,基于微计算机的虚拟测试仪器的出现和广泛使用,将对测试仪器产生极为

[测试测量]

在FPGA上建立一个UWB脉冲发生器

用大多数FPGA都可以实现一个数字UWB(超宽带)脉冲发生器。本设计可以创建一个两倍于FPGA时钟频率的脉冲信号(图1)。以前的设计要采用异步延迟,才能制造出所需频率的脉冲。不过该设计需要一只支持三态上拉的FPGA,如Xilinx公司的Virtex 2(参考文献1)。这种方案亦需要手工布局与布线。今天的FPGA都不支持三态上拉。另外,异步延迟会随温度而变化。本例采用了一种有多时钟相位组合的同步延迟方案。这一设计可以实现于所有类别的FPGA上。 本设计中的主要限制因素是DCM(数字时钟管理器)以及触发器的主时钟频率。例如,Xilinx公司Virtex 4的DCM不能超过400 MHz。一片FPGA可以生成频

[嵌入式]

一种基于STM32和FPGA的多轴运动控制器的设计与实现

引言 数控系统在工矿领域已得到广泛应用,计算机数控系统通过对数字化信息的处理和运算,并转化成脉冲信号,实现对电机的控制,进而控制数控机床动作和零件加工。随着嵌入式技术的发展,我们可以设计规模更小,成本更低,功能更特定的嵌入式系统来完成传统计算机数控系统所完成的工作。 1、设计方案 本系统以嵌入式处理器STM32和FPGA芯片为核心,运动控制方案中的处理部分都放在FPGA内部实现。这是1种硬件软化的方案,即具有软件可编程、可重构的特点,又有硬件那样高性能、高可靠、高一致性的优点。其系统原理框图如图1所示。 图1 系统原理 STM32从SD卡中读取数据文件并进行相关算法处理,通过键盘扫描电路设置系统加减速的初始速度、最大速度、

[单片机]

利用FPGA实现用户自定义测量控制系统

NI LabVIEW是一个开放而灵活的开发环境,能够与多种工业硬件无缝连接,将基于配置的开发方式和编程语言紧密结合起来。而结合可编程逻辑控制器(PLC)可靠性、PC处理能力以及可自定义硬件FPGA的灵活性的NI可编程自动化控制器(PAC),则是NI工业自动化平台的核心构件。NI中国技术市场工程师称,由NI LabVIEW软件支持的NI高级嵌入式控制和采集系统CompactRIO PAC,能为工业和嵌入式控制应用提供高性能和高可靠性。它结合了开放的嵌入式架构、可靠的FPGA,以及小型、坚固且可热插拔的工业I/O模块,适合测量与控制解决方案的设计、原型和部署。 NI CompactRIO可编程自动化控制器是一款低成本、可重新配

[嵌入式]

支持 FPGA 逻辑的多 Gb ADC/DAC 采样套件

赛灵思推出了新款 Zynq UltraScale+ RFSoC ZCU111 评估套件,用于支持RF 级模拟设计评估,便于广大用户亲身尝试这款颠覆性技术。该套件属于同类首创,采用 Zynq UltraScale+ RFSoC ,整合了多 Gb ADC 和 DAC 采样功能以及 FPGA 逻辑。 同类首创!! 这款套件为什么是首创?所有其他类型 RF-ADC/DAC 均为分离式架构,这就需要购买 FPGA 评估卡外加ADC / DAC 子卡,并通过 FMC 或其他连接器进行连接。分离式实现方案在可用性和设计方面都面临一些挑战。分离式ADC/DAC 解决方案的高速收发器功耗很高,此外 FPGA 和 DAC/ADC 之间的串行连

[焦点新闻]

基于FPGA的二次群分接器的结构分析及实现

1.引言 为了提高传输速率,扩大通信容量,减少信道数量,通常把多路信号复用成一路信号进行传输。在多种复用方式中,时分复用是一种常用的方式。时分复用是多路信号按照时间间隔共享一路信道进行传输。复接是把多路速率相对较低的数字信号通过某种协议复合成一路信号进行传输;而分接正好相反,是把一路速率相比高的信号按照对应的协议分割成发送端对应的速率相对较低的信号。为了规范复接与分接协议,ITU(国际电信联盟)根据传输速率的不同等级,将复接的数字信号为基群、二次群、三次群、四次群等,以我国实际应用为例,速率分别:2.048MHz、8.4.48MHz、34.368MHz、139.264MHz。本文介绍基于FPGA实现二次群数字信号的分接

[嵌入式]

五角大楼强化与英特尔合作研发芯片,逐步从FPGA转换为ASIC

五角大楼的最高研究机构将会进一步加强和英特尔的合作,增加防务系统中广泛使用的安全微芯片的国内产量。 美国《防务新闻》3月19日报道,美国国防部高级研究项目局(DARPA)18日宣布了这一计划,以应对该国微芯片产量不足带来的长期后果。美国在微电子制造方面主要依赖中国台湾地区,报道依然把中国大陆当成“假想敌”,担心中国大陆可能会篡改用于武器和其他重要防务平台的芯片。 SAHARA项目(@五角大楼) 这项公告与全球半导体芯片短缺的现实相吻合。后者促使拜登政府承诺斥资370亿美元加快美国的芯片生产。 DARPA发言人说,DARPA将向英特尔公司支付一笔数额不详的款项,以帮助提高产量,而这个名为“自动实现应用的结构阵列硬件”(SAHA

[手机便携]

一种ARM+DSP协作架构的FPGA验证实现

介绍了以 ARM + DSP 体系结构为基础的FPGA实现。在其上验证应用算法,实现了由ARM负责对整个程序的控制,由DSP负责对整个程序的计算,最大程度地同时发挥了ARM和DSP的各自优势。 ARM通用CPU及其开发平台,是近年来较为流行的开发平台之一,而由ARM+DSP的双核体系结构,更有其独特的功能特点:由ARM完成整个体系的控制和流程操作,由DSP完成具体的算法和计算处理。这样,不但可以充分地发挥ARM方便的控制优势,同时又能最大限度地发挥DSP的计算功能。这在业界已逐渐成为一种趋势。 本文的FPGA的Demo验证,是在基于一款DSP内核处理器的研发基础上,对其功能进行验证的一个小目标识别算法的实现。考虑到软件环

[新品]

无线传感器网络MAC协议分析与实现 (杨志军,谢显杰,丁洪伟著)

无线传感器网络MAC协议分析与实现 (杨志军,谢显杰,丁洪伟著) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号