近年来,嵌入式技术发展迅速,嵌入式应用已经深入到金融、航空航天、电信、网络、工业控制、信息家电等各个领域。嵌入式系统已经无所不在,与人们的日常生活息息相关。嵌入式系统以微处理器为核心,以计算机技术为基础,其主要特征是实时性强。针对嵌入式处理器的应用,Xilinx公司推出了IBM PowerPC 405和MicroBlaze两种32位的嵌入式处理器内核,IBMPowerPC 405是嵌入在现场可编程门阵列(filedprogrammable gate array,FPGA)中的硬核处理器,而MicroBlaze是采用哈佛(Harvard)总线结构的软核处理器,可在可编程器件中进行配置,具有更好的灵活性,适合复杂嵌入式系统的开发。

1 MicroBlaze23软内核内部结构

MicroBlaze软内核是一种针对Xilinx FPGA器件而优化的功能强火的32位微处理器,适用于所有现产的FPGA器件。MicroBlaze软内核和其它外设IP核一起,可以完成可编程系统芯片(SOPC)的设计。MicroBlaze软内核采用RISC(reduced instruction system computer)架构和哈佛(Harvard)结构的32位指令和数据总线,内部有32个通用寄存器R0~R31和2个特殊寄存器程序指针(PC)和处理器状态寄存器(MSR)。MicroBlaze还具有指令和数据缓存,所有的指令长度都是32位,有3个操作数和两种寻址模式,指令功能划分有逻辑运算,算术运算,分支,存储器读/写和特殊指令等,指令执行的流水线是并行流水线,它分为3级流水线:取指,译码和执行。MicroBlaze软内核结构如图1所示。

Microblaze软内核,片上本地存储器,标准总线互连以及基于片上外设总线(OPB)的外围设备构成了MicroBlaze嵌入式系统。

2 MicroBlaze嵌入式系统开发流程

在用Xilinx公司生产的FPGA进行嵌入式设计时,Xilinx公司提供嵌入式开发工具EDK,它由XPS(xilinxplatform studio),SDK(software development kit),creat—import peripheral和XMD(xilinx microprocessordebugger)组成。

其中XPS是主设计程序平台,可以实现嵌入式开发的所有步骤环节,其它的软件工具可以在XPS里面直接调用。SDK是软件开发工具,支持C和C++,主要完成软件的设计。creat—import peripheral工具实现用户IP核和CPU的接口设计。XMD主要完成软件调试。

进行硬件设计时,EDK以IP cote的形式,提供诸如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART中断控制器、定时器及其他一些外围设备接口等资源,利用这些资源,用户能够轻松构建一个完善的嵌入式处理器系统。进行相应的软件设计时,EDK提供了外设IP驱动程序和大量的函数库,板级支持包(BSP:board support package)以及完整的操作系统以帮助用户开发软件平台。

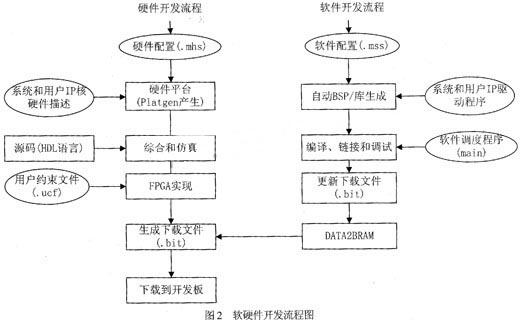

当用户需要定制自己的外设以完成一些特殊功能时,用户可以Xilinx公司提供的Project Navigator ISE环境下,用VerilogHDL或者VHDL代码完成用户IP core的设计,利用XPS中提供的creat—import peripheral工具完成创建和导入用户IP core。利用EDK现有的IP core和用户自定义IP core可以建立一个完善的嵌入式系统。在XPS开发环境下,完整的开发流程如图2所示。

MHS和MSS文件都是由用户根据整个系统的要求通过EDK生成的。其中MHS文件包含了对整个MicroBlaze系统组织的描述(包括处理器、总线、外设等),用户也可以根据自己的实际情况修改MHS文件(例如opb_gpio的输出宽度),完善系统设计。硬件平台生成器(PlatGen)产生整个系统的网表,结合约束文件可最终生成可配置文件(.bit)用以下载。MSS文件包含了所有外设的驱动等信息的描述,库生成器(LibGen)通过它产生所需的驱动,用户根据这些驱动文件完成软件调度程序,再由MB2GCC工具对调度程序进行编译生成可执行程序。最后.bit文件和软件程序合成下载到开发板。若程序执行不理想,可以用 XMD进行软件调试,找出问题所在,解决问题完成设计。

3 AD数据采样与实现

本设计给出了AD数据接收、采样、存储。天线接收到的信号,经过信号斛析,得到了时间信息,产生数字信号,经过30.69MHz 中频调制,送入ad_transmit完战AD采样,存储到嵌入在开发板上的blockram里面,可以通过FPGA调试工具chipscope来观察AD采样数据。

本设计采用的足e元素科技的Virtex4系列开发板,该开发板上有嵌入的两个AD数据接口(adc0,adc1),在本设计采用的是adc0。AD采样是用Verilog代码设计完成的,在ISE环境下仿真验证成功,挂载到OPB总线上。其硬件平台如图3所示。

构建实验的系统资源为:

MicroBlaze:系统的核心模块;

LMB总线:(1)ILMB BRAM Cntrl,DLMBBRAM Cntrl内部BRAM控制接口IP,使得MicroBlaze可以通过LMB总线访问BRAM;(2)BRAM-BLOCK(片内存储模块),可作为系统的程序存储空间或高速缓存;

OPB总线:(1)通信接口IP,通过OPB-UARTLITE(串行通信接口),驱动uart接口转换器完成与外部系统如 PC的数据通信;(2)用户接口IP,通过OPB总线访问 MicroBlaze。

天线等外围设备:天线、信号解析、信号产生器和中频调制完成根据解析出的时间信息产生数字信号,调制为中频模拟信号,中频调制频率为30.69MHz。

Uart端口:通过超级端口观察软件凋度程序的执行过程。

Chipscope核:ila核及icon核用来观察数据,icon核控制ila核,ila核连接所需要观察的信号的端口。

Dcm时钟控制:控制AD采样速率,本设计采样频率为81.84MHz。

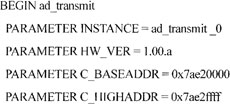

设计中的硬件描述文件(MHS)即为按照上面定制的硬件平台框图中给出的系统资源编写的,其部分内容如下:

给出的MHS文件中,列出了用户IP ad_transmit 地址,时钟还有端口连接情况,其中ad_transmit_0_ad_din设置为外部端口,连接到开发板上FPGA相应的adc0端口。chipscope_ila则列出了通过chipscope观察的信号。

软件描述文什(MSS)列出了所有外设的驱动信息,函数库产生器利用这些配置信息,配置相应的驱动程序函数库。用户根据这些驱动程序来完成软件调度程序,完成软件设计。本设计主要通过硬件来实现,软件调度程序比较简单,流程图如4所示。

完成软件调度程序以后,就可以对源程序进行编泽、汇编和链接,生成可执行义件,通过在XPS中利用工具“data2bram”,将软件设计中生成的程序代码作为存储区的初始化数据,合并到硬件设计中生成的下载配置文件中,最终生成包含软、硬件设计的FPGA下载配置文件“download.Bit”,就可以将其下载到芯片中验证本设计。

通过FPGA调试工具chipscope来观察接收的AD采样数据,本设计中设定了AD数据溢出控制,即AD采样数据在-8192~+8192之间,AD采样数据如图5,图6所示,实现AD数据采样。

本设计将用户IP ad_transimit挂载到OPB总线上,采用chipscope对AD采样数据进行观察,通过观察与分析,可以得出本设计很好的完成了AD数据接收,采样,存储,是一个完整的AD数据采集系统。进一步可以对存储的AD采样数据进行更为复杂的数据处理过程。

上一篇:探究最佳的结构化ASIC设计方法

下一篇:半导体IP市场迈向成熟

推荐阅读最新更新时间:2024-05-02 20:38

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号