要 点

市场的需求驱动将RF 电路集成到SoC (单片系统)中。

保持RF电路做在单独芯片上仍有一些令人信服的理由。

无线电架构的选择,特别是接收器,还远远没有定论。

架构师必须从整个系统考虑,而不能只局限于单个芯片。

无线链路在电子系统中的应用越来越普遍。WiMax 及3G蜂窝网络主导着高速数据传输的无线连接领域,而像ZigBee 及Wibree 等标准则占据了低速数据传输与低能耗市场。但不论哪种情况,市场经济及消费者都期望系统架构师至少能将无线电硬件集成到SoC (单片系统)中。

某些厂商,特别是手机厂商,似乎觉得除了将无线电完全集成到SoC中外,其它都像电子管调谐器一样过时了。然而, 是采用RF 工艺将无线电在单独芯片上实施 ,还是至少以vanilla-CMOS-logic 工艺将部分RF 电路实施到SoC上 ,这一决定并不容易。系统架构师必须考虑市场期望、寿命周期成本、性能需求及项目风险等问题。架构师需要全面分析所有这些因素,才能做出明智的决策。

首先列出的是情感,而不是客观的判断。特别是消费类移动设备市场,成本和形式因素的影响极大,通常的观念是只有单芯片方式可以接受。Broadcom? 无线电技术工程部的高级总监Maryam Rofougaran说:“问题是实施单芯片方案很困难,所以需要采用数字CMOS,”“再说RF-CMOS 工艺的成本也非常高,所以我们把目标对准了数字CMOS 工艺。”

其它经营手机业务的厂商,至少是市场份额较大的厂商,都同意这种观点。Staccato Communications的首席技术官Robert Aiello认为,“对我们来说,单芯片仅仅是一种业务考虑,我们只针对单芯片解决方案开展业务。” “因此,我们必须建立一个有大规模生产集成无线电经验的团队。”

Texas Instruments(TI)或许是这种方式最坚定的支持者,他们已经将其CMOS单芯片无线电架构作为品牌产品DRP (数字射频处理器)推出。“单芯片方案具有明显的优势,” TI无线终端业务首席技术官Bill Krenik解释道,“如今,用于低成本应用的无线电芯片已能采用数字工艺大量地制造了,” Krenik还说:“单芯片架构的设计复杂,开发成本大,因此这种设计需要大的市场以及有着良好预期的市场份额。市场份额较小的产品,如高档手机,不适合采用单芯片架构。”

另一种不容忽视的观点并非来自于客户,而是风险投资界。“如果你是当今的创业者,不管你认为是否合适,你的投资方都会督促你采用数字CMOS进行单芯片设计,”IBM客户经理Teddy O’Connell说,“但是在做出决策前,还是需要考虑某些非常重要的问题。”

许多问题都与方案的成本相关。O’Connell 和其他人指出,在多芯片封装成为主流的情况下, 单芯片相对于多芯片设计的经济性已经有所改变。双芯片组装的预算成本可能比单个封装芯片大,但这种差异只是均差的开始。“单芯片只有20% 的部分为RF电路,成品率明显低于数字部分,”O’Connell 指出,“随着设计转向更精细的几何尺寸, RF 部分将会增大而不是缩小。而且,对RF 性能的要求会推动整个设计迈向更先进的数字工艺节点,而如果采用单个RF 及数字芯片是无法实现的。”

然而成本均差难以捉摸。选择单芯片还是多芯片策略会影响无线电架构的选择,这又对无线电所需外部无源元件的数量和质量产生重大影响。除去元件、空间、插入及测试等成本,这些无源元件会对系统总成本产生较大的影响。

性能要求和设计风险也相互关联。理论上,65nm 或90nm CMOS逻辑工艺最适合RF。“就在几年前,千兆赫范围的RF要采用GaAs(砷化镓) 工艺加工的昂贵晶体管。”Analog Devices的业务开发总监Doug Grant评论说,“但工艺尺寸减小导致寄生电容降低、传输路径缩短以及晶体管预算增加,所有这些都对RF 设计师有利。”

采用这种工艺的晶体管截止频率对于90nm工艺而言能够高于40GHz,采用65nm 工艺的晶体管截止频率还要高。小型器件中较低的串联电阻意味着较低的噪声本底,能稍稍补偿较低的工作电压,其线性度也不错。IBM公司的O’Connell说道:“CMOS中的三阶交调截距要胜过SiGe(硅锗)”。只要电路不要求较高的Q值,就可以制造相当不错的螺旋电感。

工艺和性能

一个合理的原因是频率。“管理需求促使超宽带射频链路向更高波段发展。这种压力要求我们设计的产品在10 GHz 的频率上运行”, Alereon工程与运营副总裁David Shoemaker说,“在该频率下,CMOS的 快速运行特性非常合适。但是,这些频率即使没有大的波动也会对CMOS造成严重问题。例如, VCO(压控振荡器) 容易变得不稳定,并伴有增益平坦度的问题。”分析这些问题后,Alereon 选择了以SiGe 工艺实施RF 前端,这样可以迁移到CMOS。“我们可以选择迁移电路,但目前这种做法不会大量节约成本。”Shoemaker 说道。

除了增益外,架构师们采用CMOS工艺实施 RF还需要考虑线性度问题。无线电对非线性的敏感度取决于应用和调制方案。“标准对于能否以特定的技术制造无线电有很大影响,”Staccato公司的Aiello表示,“例如,我们使用QPSK (正交相位偏移键控)而不是64-QAM (正交调幅),从而可降低对RF 部分线性度的要求。”

另一个采用数字CMOS 的大问题是模型。 数字CMOS器件通常采用高频数字模型,而更少或不涉及小信号模型。 “对于早期的RF 用户,不论是否采用CMOS工艺,模型总是个问题,”Cypress Semiconductor的首席系统架构师Dave Wright说,“我们应用于无线USB 产品的BiCMOS 工艺,最初也是为高速通信电路设计,而不是专为RF设计的。 它有很好的特性,但我们采用了多个运行点而不是一个运行点。”

晶体管模型并不是唯一的问题。噪声模型,特别是通过电源及衬底传播噪声的性能良好的模型非常关键。运行电压较低的任何RF 设计通常会产生噪音。而在诸如具有片上功率放大器的收发器这样的系统中,及出现多个互不相关RF 信号的多天线设计中,情况也是如此。即使模型本身很完善,你会对工艺工程师致力实现大型数字设计的良好成品率牵肠挂肚。他们没有必要注意小信号RF模型参数,而是将他们的工艺集中关注于门电路和SRAM 单元。因此,采用数字CMOS的设计团队,有责任实现自己的模型组并与代工厂建立紧密的关系来校准其模型。

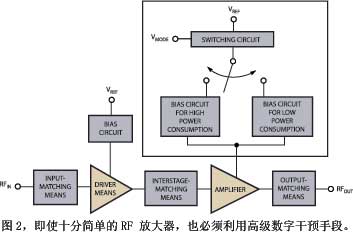

模型的不确定性增加了难于量化的设计风险。 尽管存在这样的困难,设计师们必须在决策中考虑这些风险。 如果不能接受设计存在一种或三种貌似有理的风险,那么有两种选择:一是依赖成功的设计团队和成熟的RF 工艺,二是依赖数字校准RF 电路来补偿模型或变化量的不确定性。 “基本上对于缺少信心的模型我们都会进行补偿。”Analog Devices的Grant说。ADI 设计师为了在工作温度范围内稳定CMOS信号路径,有时在简单的偏置发生器中使用20个或30个额外晶体管,这并不是什么稀罕事。 Analog Devices有时在精密的RF 电路 (图1)旁边增加低压差稳压器来控制CMOS 芯片中的电压变量。 设计师有时也会采用数字技术: 使用 ADC 来快速测量电路的运行点及计算补偿参数,同时加载DAC 来调整偏压电流或补偿电流 (图 2)。 有些设计师甚至开玩笑地说他们正转向一种将 DAC 输出附加在每个RF 晶体管引脚上的设计风格。

“毫无疑问实现无线电的可升级性是一种数字密集型工艺,”TI的 Krenik说,“例如,线性度问题就是一个基本的挑战。传统的设计要求极高线性度的高压前端。但采用现今的工艺已经可以忽略这个问题。现在,我们使用精密的数字控制偏置电流与其它参数,从而实现性能较差电路的线性化。”

所以选择单芯片还是多芯片不可一概而论。某些市场不提供任何实际的选择方案:市场期望单芯片方式,成本限制需要单芯片方式。这些市场中典型的应用恐怕要说基带数字CMOS SoC 集成无线电。而在其它市场中,设计团队 也可以采取多芯片封装,这主要取决于性能和功耗要求、无线电架构的选择、稳定模型的可用性及团队的经验。“如今在宽带CDMA 中既可以看到数字CMOS ,也可以看到SiGe RF,” IBM的O’Connell说。对于一些其它领域,特别是10GHz 和10GHz以上的频率范围,目前还不存在适合接收器的RF 工艺。“WiMax、5GHz 网络及雷达目前仍然是SiGe应用场合,”O’Connell 继续说道。但要注意,SiGe 或GaAs等特殊工艺所需的频率大大低于功率放大器和天线开关的频率,从而需要比接收器更高的功耗。

除了工艺技术的选择外,功率放大器依然存在其它问题。“随着有效通道长度变短,集成功率放大器的问题变得越来越困难,”Rofougaran说。“由于多种原因,比如可靠性和局部发热等,极小型晶体管不能承受较大信号。在某些工作条件下,功率放大器中会有相当大的电流。”尽管如此,Broadcom 还是在蓝牙芯片等某些低功耗的应用中集成了功率放大器。

“从技术角度来说可以集成达到大约10 mW的任何功率放大器,但实际上目前4 mW已经是极限,”Cypress的Wright说道,“超过这一限度,功率放大器的某些结构即使在低功耗模式下也能消耗大量静态功率,从而缩短电池寿命。在更先进的工艺中,电压摆幅也是个问题。”

无线电架构

采用单芯片或双芯片的决策与设计师实施的无线电架构决策相互影响,这些决策包括无线电中接收器和发射器的选择。人们对接收器存在一种偏见,认为越早对信号进行数字处理,效果就越好。某些厂商曾将ADC 置于低噪声放大器的输出端,直接对输入的R F数字化,而在转换器输入与白噪声之间只采用一个带通滤波器。另一极端,某些设计师继续使用可以追溯到电子管无线电年代的超外差接收器架构。而最常采用的直接转换接收器架构介于两者之间。

通常理想的情况是只将一个ADC 置于低噪声放大器中。这种方式基本上消除了RF 设计的问题,同时带来新的可能性。例如,简单数字化整个蜂窝频谱的蜂窝基站可即时对频带进行滤波,并可对多个调制方案选择通道。设计师不需要为每个主动会话分配RF 前端,同时数字域中的滤波质量会超过任何物理滤波器。

“但这种设计的转换器很难实现,需要足够的电流,”O’Connell说。为了采集足够的信号以确保数字处理的成功,转换器需要拥有较大的采样速率和较宽的动态范围, DSP从可以从相邻通道信号及带外噪声抽取少量的输入信号。由于类似的原因,这种方案同时具有出色的线性特点。虽然这种转换器设计目前已有可能,但O’Connell 认为这种转换器设计只适合于高端设计,如基站和多标准的“全球性电话。”

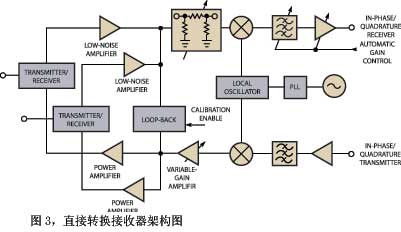

对多数无线电架构师来说直接转换接收器 (图3)是更好的选择。 在这种架构中,RF 信号由低噪声放大器传送至RF 信号与来自本地振荡器的I (同相) 和Q (正交) 信号相乘的混合器。 结果就产生基带频率中的I和Q两个信号。 通常,基带信号通过抗混叠滤波器进入一对ADC中。

这种方式却并不能大大简化问题。直接转换架构出现在电子管无线电早期超外差技术之后,但由于各种各样挑战性的问题,随后被设计师放弃。低噪声放大器和混合器必须为线性,本地振荡器必须清晰稳定,而直接转换架构的适合程度在某种程度上取决于调制方案。“这取决于数据,”Broadcom公司的Rofougaran说道,“我们的2046 蓝牙芯片需要处理数据带宽比较窄、很多信号频谱接近直流的GFSK (高斯滤波频移键控) 等问题。由于直流漂移取消,直接转换架构存在问题,所以,我们使用低IF 超外差结构。与此相反,无线局域网有较宽的数据带宽和较少的接近直流信息,因此我们采用直接转换架构。”

Cypress 还选择了低IF 超外差架构来实施无线USB 设备。“这种架构最适合我们的情况了,”Wright 解释说,“我们良好的电路设计比直接转换架构具有更好的抑制效果。而且,低 IF在逻辑电路中所消耗的功耗并不多。在某些情况下,我们可以转向直接转换,但最好的选择是重新使用现有的架构。”

一个不适合采用超外差的因素是采用这种方法对接收器进行系统集成比较困难。Alereon公司的Shoemaker 指出,IF 部分可生成不必要的频率毛刺 ,虽然不影响超外差接收器本身,但可严重影响系统中的其它接收器。由于当今很多移动设备中包含多个无线电,因此在设计设备之前,系统架构师必须为封装中所有无线电仔细规划频谱 。

发射器方面也有类似决策。这时,最常用的架构是极性环路功率放大器。这种设计包括了振幅和相位信号的回馈环路,具有良好的振幅与相位线性特点,对于类似采用两种数量进行编码信号的QAM等调制方案非常重要。但设计师还讨论了其它方案,包括未来可能的方案,比如以功率DAC直接驱动天线。

所以在对SoC无线电的决策中,终端市场及投资方要求厂商进行单芯片设计的压力日益增长,至少是对小信号的RF 电路采用单芯片设计。然而使用这种方法的设计师需要克服集成过程所遇到的很难对付的困难。许多问题反映了积极使用数字电路进行校准和控制,以及反映了设计经验。但这一行业发展到高频接收器RF 部分采用SoC还有较长的路程,而距离只采用最低功耗的发射器电路则更远。

由于CMOS工艺技术并没有转向更友好的RF 设计,如数年前TI做的一样,集成度的不断提高将意味着在电路设计与无线电架构中实现重大创新。Analog Devices公司的Grant 对设计师如何实现这一进步做出了重要的评论:“在数年前的一个项目中,我们只是观望整个设计。”他说。“我们体会到,RF、数字化及软件设计师之间并没有真正地相互交流。他们都只忙于自己的噪声预算,从而导致系统效率低下。这使我们认识到必须对整个信号链进行优化,不能将各模块彼此分割开来,必须全盘考虑无线电,包括滤波器、数字控制及软件创建的运行模式,而不能只关注芯片。”

附文:高度集成RF的含意

作者:Ajay Khoche, Verigy

消费无线设备市场的爆炸性增长正在促进向更高的性能和集成度发展,入市时间和测试成本也面临着更大的压力。一直以来测试RF设备传统上比测试数字设备要困难。如今,由于多波段、多模式、MIMO (多入多出) 设备的出现, RF测试变得更为复杂。设备端口数的不断增多,收发器复杂性的提高以及先进技术中PVT (工艺/电压/温度) 变量的增加等因素都要求有仔细的设计与测试策略,以满足消费市场的成本压力及创造一个现实的测试环境。

设计师既要确保芯片的性能,还要确保其合适测试策略满足入市时间和成本目标,实现市场成功。例如,今后五年内MIMO 设备的RF 结构将从2×2增加到3×3,甚至到8×8 RF 分支。导致RF 路径在输入与输出间的测试出现大幅增长。传统的单入单出方式由于大大增加了测试时间而变得不切实际。片上DFT (可测性设计) 电路通过片上并行测试或降低外部设备需要,实现高效的多址测试 (参考文献 A和 参考文献B),从而有助于缓和消费无线设备市场爆炸性增长。此外,设计师必须增加片上测试电路,以创建实际的测试环境,这种环境,如果不能从外部创建,是很难建立的。这些条件包括在观察阶段与全局PVT变量平衡中对模拟电路多路径的恒定电流进行加载。尽管RF-BIST (内建自测试) 方式目前应用还不太普遍,但已经开始解决一些问题。

在测试系统方面,工程师仍必须满足基本的精确、稳定、可靠、低噪声本底、高RF及基带性能等要求。此外,这些系统必须具备灵活的系统集成架构,以对设备进行高效测试。集成架构提供了必要的密度和通道数以实现较高的并行测试效率,从而达到最少的测试时间。灵活的架构可以充分利用可行的测试资源。系统应该允许设计师在测试资源要求与可实现的测试时间、及测试成本之间做出折衷,以满足最终产品要求。

某些新的测试方法使用设计的数学模型来测量供选择的参数(参考文献 C及参考文献 D)。这些技术似乎很有应用前景,但目前还处于开发阶段。

参考文献

A. Acar, Erkan, Sule Ozev, and Kevin B Redmond, “A Low-Cost RF MIMO Test Method Using a Single Measurement Set-up,” 25th IEEE VLSI Test Symposium.

B. Srinivasan, G, A Chatterjee, and F Taenzler, “Alternate Loop-Back Diagnostics Tests for Wafer-Level Diagnosis of Modern Wireless Transceivers Using Spectral Signatures,” IEEE VLSI Test Symposium, 2006.

C. Battcharya, C, et al, “Alternate Testing of RF Transceivers Using Optimized Test Stimulus for Accurate Prediction of System Specifications,” Journal of Electronic Testing: Theory and Application, June 2005.

D. Turfillaro, et al, “Model-based Test Methods for Analog Integrated Circuits,” IEEE Instrumentation and Measurement Technology Conference, 2007.

上一篇:基于ARM的智能综合监控基站方案设计

下一篇:超宽带认知无线电的关键技术研究

推荐阅读最新更新时间:2024-05-07 15:59

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Quobly与意法半导体建立战略合作, 加快量子处理器制造进程,实现大型量子计算解决方

- RTI Connext Drive参展CES 2025,以领先通信框架加速SDV开发

- 黑莓 1.6 亿美元甩卖网络安全业务 Cylance,远低于其 14 亿美元的收购价

- eIQ® Time Series Studio简介:简化边缘 AI 开发

- 尺寸更小,性能更强:左蓝微电子发布两款PESAW双工器

- 贸泽开售适用于全球LTE、智能和IoT应用的 Nordic Semiconductor nRF9151-DK开发套件

- 新蓝牙6.0协议扩展应用范围

- 宁德时代巧克力换电生态大会将举行,什么是“巧克力换电”?1.5分钟换电能实现吗?

- 新型生物材料与高端医疗器械广东研究院、远诺技术转移中心加入面向初创企业的 MathWorks

- S5PV210 Linux字符驱动之PWM蜂鸣器驱动

- 尼得科机床新增可实现高效加工的高速主轴产品线

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Bourns推出全新高效能、超紧凑型气体放电管 (GDT) 浪涌保护解决方案

- S5PV210之UBOOT-2011.06启动过程解析

- 六个理由告诉您为什么应该将模拟无线麦克风更换为数字无线麦克风

- S5PV210启动过程分析

《汽车电路维修》复习题

《汽车电路维修》复习题 新能源电路分析及常见故障与诊断

新能源电路分析及常见故障与诊断 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号