摘要:简要介绍了Ethernet over SDH(EoS)系统的结构原理,阐述和分析了EoS的LAPS协议核心技术,给出了使用FPGA完成SDH网络和以太网的连接,从而实现EoS的嵌入式系统设计方案。

关键词:EoS;以太网;SDH;嵌入式系统

随着波分复用技术和高速以太网技术的发展,骨干网的带宽呈几何级数增长,已达到了吉比特甚至更高的水平。而连接骨干网和用户网的接入网的速率却没有太大的提高,已成为网络发展的瓶颈。要想实现高速、可靠的接入,使终端用户充分利用骨干网的巨大容量,必须采用新的高速接入技术。SDH技术已非常成熟,其安全性好,可靠性高;用SDH传输网络承载以太网IP包以实现网络用户的远程接入或异地局域网互连,是一种非常方便的实现方案。

1 EoS系统结构

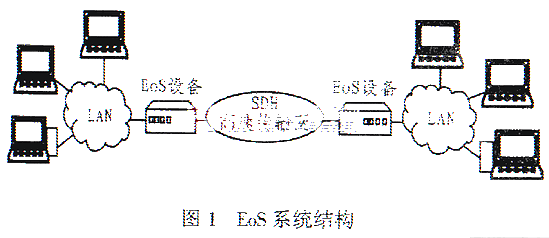

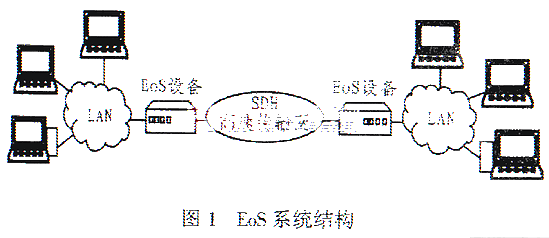

Ethernet over SDH系统的结构如图1所示。

Ethernet over SDH系统是以以太网IP数据包交换为基础的光广域网,它本质上采用的是面向无连接的机制,内在的全网状连接适合于分布式通信的无连接网络,它将以太网的交换灵活性和资源优化能力与现有SDH光网络的大容量、高带宽效率和低协议开销相结合,是一种高速、经济的数据接入系统。Ethernet over SDH系统实现的关键是在SDH设备上增加以太网接口设备或者以太网协议转换设备,以提供帧映射和VC级联等功能。本文将使用FPGA和相关芯片构建图1中所示的以太网协议转换设备。

2 EoS协议的层次模型

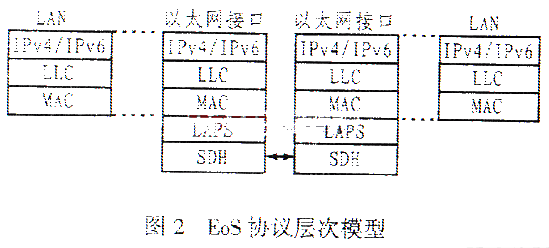

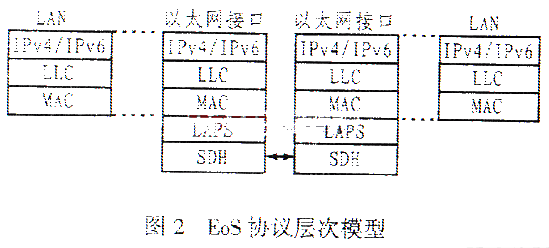

Ethernet over SDH协议的层次模型如图2所示,该协议分为三层:其中网络层为TCP和IPv4/IPv6;链路层由LLC/MAC/LAPS三个子层组成物理层为SDH传输网。

Ethernet over SDH按照ITU-X.86的规定采用LAPS对以太网IP数据包进行链路层封装,从而将以太网帧映射到SDH帧中,其协议层次模型为IP/Ethernet/LAPS/SDH。

1 EoS系统结构

Ethernet over SDH系统的结构如图1所示。

Ethernet over SDH系统是以以太网IP数据包交换为基础的光广域网,它本质上采用的是面向无连接的机制,内在的全网状连接适合于分布式通信的无连接网络,它将以太网的交换灵活性和资源优化能力与现有SDH光网络的大容量、高带宽效率和低协议开销相结合,是一种高速、经济的数据接入系统。Ethernet over SDH系统实现的关键是在SDH设备上增加以太网接口设备或者以太网协议转换设备,以提供帧映射和VC级联等功能。本文将使用FPGA和相关芯片构建图1中所示的以太网协议转换设备。

2 EoS协议的层次模型

Ethernet over SDH协议的层次模型如图2所示,该协议分为三层:其中网络层为TCP和IPv4/IPv6;链路层由LLC/MAC/LAPS三个子层组成物理层为SDH传输网。

Ethernet over SDH按照ITU-X.86的规定采用LAPS对以太网IP数据包进行链路层封装,从而将以太网帧映射到SDH帧中,其协议层次模型为IP/Ethernet/LAPS/SDH。

3 EoS的帧格式

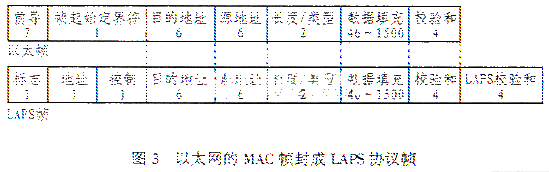

LAPS(Link Access Procedure SDH,SDH上的链路接入规程)协议帧是 HDLC协议帧的一种变体,它可提供数据链路服务及协议规范,并可专门对SDH网络所需传送的IP数据包进行封装以便对封装后的以太网帧进行定界(采用标志定界)。

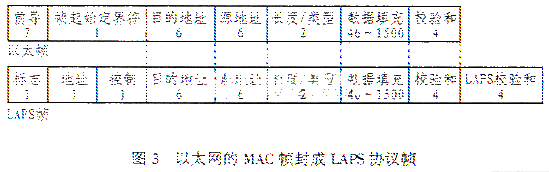

使用 LAPS实现Ethernet over SDH时其帧映射过程分两步:一是将以太网的MAC帧封装成LAPS协议帧;二是将LAPS协议帧映射到SDH帧中。

将以太网的MAC帧封装成LAPS协议帧的过程如图3所示。通过LAPS可将MII接口接收到的MAC帧使用RS(协调子层)去掉前导(Preamble)码、帧起始定界符(SFD)和扩展字段(Extension),然后封装入LAPS协议帧。

4 EoS的嵌入式系统设计

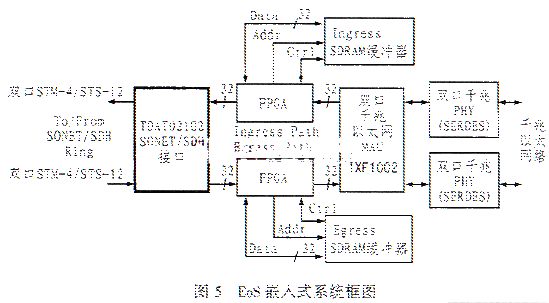

EoS嵌入式系统通常应该包含以下三部分:以太网接口部分、协议转换部分、光接口部分。其中以太网接口部分用于接收以太网数据,并对本地网络进行流量控制;协议转换部分负责帧结构转换,同时协调三部分的运作;而光接口部分则使用成帧器实现SDH网络数据的上下路。

4.1 以太网接口部分

以太网接口部分使用的是双口千兆以太网控制芯片IXF1002。IFX1002提供有两个全双工的独立高性能千兆以太网接口,支持GPCS层的接口管理。当IFX1002设置SNMP和RMON管理计数后,便可通过MCU8/16接口进行访问操作。每一个MAC接口包括一个4k字节的接收FIFO和一个2k字节的发送FI-FO,所有数据都可以在公共的高性能IXBUS总线上传输。此外,IFX1002芯片完全兼容IEEE 802.3和IEEE802.3z标准,支持自协商和流量控制。

3 EoS的帧格式

LAPS(Link Access Procedure SDH,SDH上的链路接入规程)协议帧是 HDLC协议帧的一种变体,它可提供数据链路服务及协议规范,并可专门对SDH网络所需传送的IP数据包进行封装以便对封装后的以太网帧进行定界(采用标志定界)。

使用 LAPS实现Ethernet over SDH时其帧映射过程分两步:一是将以太网的MAC帧封装成LAPS协议帧;二是将LAPS协议帧映射到SDH帧中。

将以太网的MAC帧封装成LAPS协议帧的过程如图3所示。通过LAPS可将MII接口接收到的MAC帧使用RS(协调子层)去掉前导(Preamble)码、帧起始定界符(SFD)和扩展字段(Extension),然后封装入LAPS协议帧。

4 EoS的嵌入式系统设计

EoS嵌入式系统通常应该包含以下三部分:以太网接口部分、协议转换部分、光接口部分。其中以太网接口部分用于接收以太网数据,并对本地网络进行流量控制;协议转换部分负责帧结构转换,同时协调三部分的运作;而光接口部分则使用成帧器实现SDH网络数据的上下路。

4.1 以太网接口部分

以太网接口部分使用的是双口千兆以太网控制芯片IXF1002。IFX1002提供有两个全双工的独立高性能千兆以太网接口,支持GPCS层的接口管理。当IFX1002设置SNMP和RMON管理计数后,便可通过MCU8/16接口进行访问操作。每一个MAC接口包括一个4k字节的接收FIFO和一个2k字节的发送FI-FO,所有数据都可以在公共的高性能IXBUS总线上传输。此外,IFX1002芯片完全兼容IEEE 802.3和IEEE802.3z标准,支持自协商和流量控制。

IXF1002可以通过对以太网数据包包头的处理达到提前过滤地址的目的;在包的传输中,芯片具有IEEE P802.1Q的VLAN标签添加、删除和替代功能;而当包发生错误时,它会提供忽略或停止发送的选择;同时,还提供可编程的无效数据包自动过滤功能;当FIFO上出现无效数据包的时候,芯片可以发出通知信号。

本设计中, IXF1002的IXBUS工作在Split(双向32位传输)模式(如图4所示),它使用fps rxf、sop rxf、eop rxf.、fps txf、sop txf、eop txf信号线进行握手控制,使用双向32位数据总线进行数据传输,并可以通过访问fbe l7:0来查询当前传输的数据是否有效。

4.2 协议转换部分

协议转换部分可通过高速FPGA实现。本设计选择两片Altera公司的APEX20K200E(Ingress数据和Egress数据各一片)来管理不同方向的数据;同时为每一片FPGA配备了一块片外SDRAM以做为单向FIFO数据缓冲器。本部分的主要功能有:

●通过以太网控制芯片的接口总线IXUS获取和发送数据;

●可按照标准速率及总线宽度将数据传送给SDH成帧器,同时接收成帧器的数据;

●发送、接收、处理网络控制芯片以及成帧器的握手信号;

IXF1002可以通过对以太网数据包包头的处理达到提前过滤地址的目的;在包的传输中,芯片具有IEEE P802.1Q的VLAN标签添加、删除和替代功能;而当包发生错误时,它会提供忽略或停止发送的选择;同时,还提供可编程的无效数据包自动过滤功能;当FIFO上出现无效数据包的时候,芯片可以发出通知信号。

本设计中, IXF1002的IXBUS工作在Split(双向32位传输)模式(如图4所示),它使用fps rxf、sop rxf、eop rxf.、fps txf、sop txf、eop txf信号线进行握手控制,使用双向32位数据总线进行数据传输,并可以通过访问fbe l7:0来查询当前传输的数据是否有效。

4.2 协议转换部分

协议转换部分可通过高速FPGA实现。本设计选择两片Altera公司的APEX20K200E(Ingress数据和Egress数据各一片)来管理不同方向的数据;同时为每一片FPGA配备了一块片外SDRAM以做为单向FIFO数据缓冲器。本部分的主要功能有:

●通过以太网控制芯片的接口总线IXUS获取和发送数据;

●可按照标准速率及总线宽度将数据传送给SDH成帧器,同时接收成帧器的数据;

●发送、接收、处理网络控制芯片以及成帧器的握手信号;

●实现LAPS帧映射,包括自扰码和速率匹配;

●将经过处理的数据存储于相应的外部存储器内,等待发送;

●提供与MCU的接口,接受管理控制;

●进行各种流量统计,实施流量控制。

下面是流量控制功能的具体实现过程。其中:Ingress表示以太网到SDH方向,Egress表示SDH到以太网方向。

1以太网控制芯片接收本地以太网内针对本设备发出的PAUSE帧,并告知In-gressFPGA,FPGA将此帧进行复制,并在不经IngressFIFO列队的情况下直接送入SDH网络,然后PAUSE帧以最快速度到达远端设备,以中止远端以太网中用户的数据发送。同样,如果本地E-gressFIFO缓冲器数据满,IngressFPGA构造的PAUSE帧也不经IngressFIFO列队而直接向远端发送。

2 当本地IngressFIFO缓冲器数据满时,E-gressFPGA向本地以太网控制芯片发送PAUSE通知,以太网控制芯片接收到通知后,向本地以太网用户发送PAUSE帧以停止其数据发送。同样,如果是从SDH网络上接收到PAUSE帧,则EgressFPGA立即发送PAUSE通知到本地以太网控制芯片,再由以太网控制芯片的PAUSE帧中止用户发送的数据。

3 在MCU控制下,EgressFPGA和IngressFPGA都具有XON/XOFF控制功能,可使整个流量控制更加快捷、合理,有利于保证数据的完整和正确。

本设计中,两片FPGA都可以对SDRAM进行控制,并对其存储数据的容量进行计数,同时生成数据存储位置列表,指示数据包在存储器中的位置以提供给MCU查询。

4.3 光接口部分

光接口部分选用杰尔系统公司(Agere System)的成帧器 TDAT021G2。该成帧器与FPGA的接口为UTOPIA。成帧器支持净荷的上下路,同时可为其发送处理的数据生成CRC-16/32校验或检查接收数据的校验和是否有效。在SDH网络侧支持四路的STS-3/STM-1或者两路的STS-12/STM-4,本设计中采用后者。

●实现LAPS帧映射,包括自扰码和速率匹配;

●将经过处理的数据存储于相应的外部存储器内,等待发送;

●提供与MCU的接口,接受管理控制;

●进行各种流量统计,实施流量控制。

下面是流量控制功能的具体实现过程。其中:Ingress表示以太网到SDH方向,Egress表示SDH到以太网方向。

1以太网控制芯片接收本地以太网内针对本设备发出的PAUSE帧,并告知In-gressFPGA,FPGA将此帧进行复制,并在不经IngressFIFO列队的情况下直接送入SDH网络,然后PAUSE帧以最快速度到达远端设备,以中止远端以太网中用户的数据发送。同样,如果本地E-gressFIFO缓冲器数据满,IngressFPGA构造的PAUSE帧也不经IngressFIFO列队而直接向远端发送。

2 当本地IngressFIFO缓冲器数据满时,E-gressFPGA向本地以太网控制芯片发送PAUSE通知,以太网控制芯片接收到通知后,向本地以太网用户发送PAUSE帧以停止其数据发送。同样,如果是从SDH网络上接收到PAUSE帧,则EgressFPGA立即发送PAUSE通知到本地以太网控制芯片,再由以太网控制芯片的PAUSE帧中止用户发送的数据。

3 在MCU控制下,EgressFPGA和IngressFPGA都具有XON/XOFF控制功能,可使整个流量控制更加快捷、合理,有利于保证数据的完整和正确。

本设计中,两片FPGA都可以对SDRAM进行控制,并对其存储数据的容量进行计数,同时生成数据存储位置列表,指示数据包在存储器中的位置以提供给MCU查询。

4.3 光接口部分

光接口部分选用杰尔系统公司(Agere System)的成帧器 TDAT021G2。该成帧器与FPGA的接口为UTOPIA。成帧器支持净荷的上下路,同时可为其发送处理的数据生成CRC-16/32校验或检查接收数据的校验和是否有效。在SDH网络侧支持四路的STS-3/STM-1或者两路的STS-12/STM-4,本设计中采用后者。

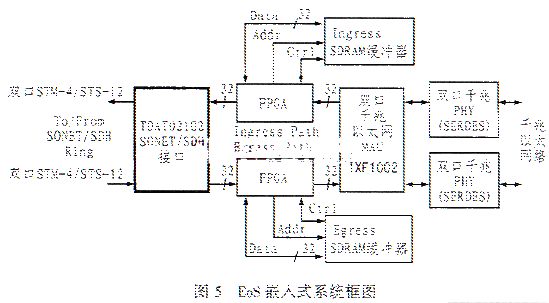

EoS嵌入式系统框图见图5,需要说明的是,整个系统各个部分均有MCU接口,可以使用一块低成本的51单片机80C320进行整个系统的协调控制。

5 结束语

本文所提出的嵌入式系统可用作各种通用和专用SDH网络和以太网设备的连接,如果在系统中加入解密加密功能,还可以构建基于EoS技术的虚拟网VPN,具有很好的应用前景。

EoS嵌入式系统框图见图5,需要说明的是,整个系统各个部分均有MCU接口,可以使用一块低成本的51单片机80C320进行整个系统的协调控制。

5 结束语

本文所提出的嵌入式系统可用作各种通用和专用SDH网络和以太网设备的连接,如果在系统中加入解密加密功能,还可以构建基于EoS技术的虚拟网VPN,具有很好的应用前景。

引用地址:实现Ethernet over SDH的嵌入式系统研究

1 EoS系统结构

Ethernet over SDH系统的结构如图1所示。

Ethernet over SDH系统是以以太网IP数据包交换为基础的光广域网,它本质上采用的是面向无连接的机制,内在的全网状连接适合于分布式通信的无连接网络,它将以太网的交换灵活性和资源优化能力与现有SDH光网络的大容量、高带宽效率和低协议开销相结合,是一种高速、经济的数据接入系统。Ethernet over SDH系统实现的关键是在SDH设备上增加以太网接口设备或者以太网协议转换设备,以提供帧映射和VC级联等功能。本文将使用FPGA和相关芯片构建图1中所示的以太网协议转换设备。

2 EoS协议的层次模型

Ethernet over SDH协议的层次模型如图2所示,该协议分为三层:其中网络层为TCP和IPv4/IPv6;链路层由LLC/MAC/LAPS三个子层组成物理层为SDH传输网。

Ethernet over SDH按照ITU-X.86的规定采用LAPS对以太网IP数据包进行链路层封装,从而将以太网帧映射到SDH帧中,其协议层次模型为IP/Ethernet/LAPS/SDH。

1 EoS系统结构

Ethernet over SDH系统的结构如图1所示。

Ethernet over SDH系统是以以太网IP数据包交换为基础的光广域网,它本质上采用的是面向无连接的机制,内在的全网状连接适合于分布式通信的无连接网络,它将以太网的交换灵活性和资源优化能力与现有SDH光网络的大容量、高带宽效率和低协议开销相结合,是一种高速、经济的数据接入系统。Ethernet over SDH系统实现的关键是在SDH设备上增加以太网接口设备或者以太网协议转换设备,以提供帧映射和VC级联等功能。本文将使用FPGA和相关芯片构建图1中所示的以太网协议转换设备。

2 EoS协议的层次模型

Ethernet over SDH协议的层次模型如图2所示,该协议分为三层:其中网络层为TCP和IPv4/IPv6;链路层由LLC/MAC/LAPS三个子层组成物理层为SDH传输网。

Ethernet over SDH按照ITU-X.86的规定采用LAPS对以太网IP数据包进行链路层封装,从而将以太网帧映射到SDH帧中,其协议层次模型为IP/Ethernet/LAPS/SDH。

3 EoS的帧格式

LAPS(Link Access Procedure SDH,SDH上的链路接入规程)协议帧是 HDLC协议帧的一种变体,它可提供数据链路服务及协议规范,并可专门对SDH网络所需传送的IP数据包进行封装以便对封装后的以太网帧进行定界(采用标志定界)。

使用 LAPS实现Ethernet over SDH时其帧映射过程分两步:一是将以太网的MAC帧封装成LAPS协议帧;二是将LAPS协议帧映射到SDH帧中。

将以太网的MAC帧封装成LAPS协议帧的过程如图3所示。通过LAPS可将MII接口接收到的MAC帧使用RS(协调子层)去掉前导(Preamble)码、帧起始定界符(SFD)和扩展字段(Extension),然后封装入LAPS协议帧。

4 EoS的嵌入式系统设计

EoS嵌入式系统通常应该包含以下三部分:以太网接口部分、协议转换部分、光接口部分。其中以太网接口部分用于接收以太网数据,并对本地网络进行流量控制;协议转换部分负责帧结构转换,同时协调三部分的运作;而光接口部分则使用成帧器实现SDH网络数据的上下路。

4.1 以太网接口部分

以太网接口部分使用的是双口千兆以太网控制芯片IXF1002。IFX1002提供有两个全双工的独立高性能千兆以太网接口,支持GPCS层的接口管理。当IFX1002设置SNMP和RMON管理计数后,便可通过MCU8/16接口进行访问操作。每一个MAC接口包括一个4k字节的接收FIFO和一个2k字节的发送FI-FO,所有数据都可以在公共的高性能IXBUS总线上传输。此外,IFX1002芯片完全兼容IEEE 802.3和IEEE802.3z标准,支持自协商和流量控制。

3 EoS的帧格式

LAPS(Link Access Procedure SDH,SDH上的链路接入规程)协议帧是 HDLC协议帧的一种变体,它可提供数据链路服务及协议规范,并可专门对SDH网络所需传送的IP数据包进行封装以便对封装后的以太网帧进行定界(采用标志定界)。

使用 LAPS实现Ethernet over SDH时其帧映射过程分两步:一是将以太网的MAC帧封装成LAPS协议帧;二是将LAPS协议帧映射到SDH帧中。

将以太网的MAC帧封装成LAPS协议帧的过程如图3所示。通过LAPS可将MII接口接收到的MAC帧使用RS(协调子层)去掉前导(Preamble)码、帧起始定界符(SFD)和扩展字段(Extension),然后封装入LAPS协议帧。

4 EoS的嵌入式系统设计

EoS嵌入式系统通常应该包含以下三部分:以太网接口部分、协议转换部分、光接口部分。其中以太网接口部分用于接收以太网数据,并对本地网络进行流量控制;协议转换部分负责帧结构转换,同时协调三部分的运作;而光接口部分则使用成帧器实现SDH网络数据的上下路。

4.1 以太网接口部分

以太网接口部分使用的是双口千兆以太网控制芯片IXF1002。IFX1002提供有两个全双工的独立高性能千兆以太网接口,支持GPCS层的接口管理。当IFX1002设置SNMP和RMON管理计数后,便可通过MCU8/16接口进行访问操作。每一个MAC接口包括一个4k字节的接收FIFO和一个2k字节的发送FI-FO,所有数据都可以在公共的高性能IXBUS总线上传输。此外,IFX1002芯片完全兼容IEEE 802.3和IEEE802.3z标准,支持自协商和流量控制。

IXF1002可以通过对以太网数据包包头的处理达到提前过滤地址的目的;在包的传输中,芯片具有IEEE P802.1Q的VLAN标签添加、删除和替代功能;而当包发生错误时,它会提供忽略或停止发送的选择;同时,还提供可编程的无效数据包自动过滤功能;当FIFO上出现无效数据包的时候,芯片可以发出通知信号。

本设计中, IXF1002的IXBUS工作在Split(双向32位传输)模式(如图4所示),它使用fps rxf、sop rxf、eop rxf.、fps txf、sop txf、eop txf信号线进行握手控制,使用双向32位数据总线进行数据传输,并可以通过访问fbe l7:0来查询当前传输的数据是否有效。

4.2 协议转换部分

协议转换部分可通过高速FPGA实现。本设计选择两片Altera公司的APEX20K200E(Ingress数据和Egress数据各一片)来管理不同方向的数据;同时为每一片FPGA配备了一块片外SDRAM以做为单向FIFO数据缓冲器。本部分的主要功能有:

●通过以太网控制芯片的接口总线IXUS获取和发送数据;

●可按照标准速率及总线宽度将数据传送给SDH成帧器,同时接收成帧器的数据;

●发送、接收、处理网络控制芯片以及成帧器的握手信号;

IXF1002可以通过对以太网数据包包头的处理达到提前过滤地址的目的;在包的传输中,芯片具有IEEE P802.1Q的VLAN标签添加、删除和替代功能;而当包发生错误时,它会提供忽略或停止发送的选择;同时,还提供可编程的无效数据包自动过滤功能;当FIFO上出现无效数据包的时候,芯片可以发出通知信号。

本设计中, IXF1002的IXBUS工作在Split(双向32位传输)模式(如图4所示),它使用fps rxf、sop rxf、eop rxf.、fps txf、sop txf、eop txf信号线进行握手控制,使用双向32位数据总线进行数据传输,并可以通过访问fbe l7:0来查询当前传输的数据是否有效。

4.2 协议转换部分

协议转换部分可通过高速FPGA实现。本设计选择两片Altera公司的APEX20K200E(Ingress数据和Egress数据各一片)来管理不同方向的数据;同时为每一片FPGA配备了一块片外SDRAM以做为单向FIFO数据缓冲器。本部分的主要功能有:

●通过以太网控制芯片的接口总线IXUS获取和发送数据;

●可按照标准速率及总线宽度将数据传送给SDH成帧器,同时接收成帧器的数据;

●发送、接收、处理网络控制芯片以及成帧器的握手信号;

●实现LAPS帧映射,包括自扰码和速率匹配;

●将经过处理的数据存储于相应的外部存储器内,等待发送;

●提供与MCU的接口,接受管理控制;

●进行各种流量统计,实施流量控制。

下面是流量控制功能的具体实现过程。其中:Ingress表示以太网到SDH方向,Egress表示SDH到以太网方向。

1以太网控制芯片接收本地以太网内针对本设备发出的PAUSE帧,并告知In-gressFPGA,FPGA将此帧进行复制,并在不经IngressFIFO列队的情况下直接送入SDH网络,然后PAUSE帧以最快速度到达远端设备,以中止远端以太网中用户的数据发送。同样,如果本地E-gressFIFO缓冲器数据满,IngressFPGA构造的PAUSE帧也不经IngressFIFO列队而直接向远端发送。

2 当本地IngressFIFO缓冲器数据满时,E-gressFPGA向本地以太网控制芯片发送PAUSE通知,以太网控制芯片接收到通知后,向本地以太网用户发送PAUSE帧以停止其数据发送。同样,如果是从SDH网络上接收到PAUSE帧,则EgressFPGA立即发送PAUSE通知到本地以太网控制芯片,再由以太网控制芯片的PAUSE帧中止用户发送的数据。

3 在MCU控制下,EgressFPGA和IngressFPGA都具有XON/XOFF控制功能,可使整个流量控制更加快捷、合理,有利于保证数据的完整和正确。

本设计中,两片FPGA都可以对SDRAM进行控制,并对其存储数据的容量进行计数,同时生成数据存储位置列表,指示数据包在存储器中的位置以提供给MCU查询。

4.3 光接口部分

光接口部分选用杰尔系统公司(Agere System)的成帧器 TDAT021G2。该成帧器与FPGA的接口为UTOPIA。成帧器支持净荷的上下路,同时可为其发送处理的数据生成CRC-16/32校验或检查接收数据的校验和是否有效。在SDH网络侧支持四路的STS-3/STM-1或者两路的STS-12/STM-4,本设计中采用后者。

●实现LAPS帧映射,包括自扰码和速率匹配;

●将经过处理的数据存储于相应的外部存储器内,等待发送;

●提供与MCU的接口,接受管理控制;

●进行各种流量统计,实施流量控制。

下面是流量控制功能的具体实现过程。其中:Ingress表示以太网到SDH方向,Egress表示SDH到以太网方向。

1以太网控制芯片接收本地以太网内针对本设备发出的PAUSE帧,并告知In-gressFPGA,FPGA将此帧进行复制,并在不经IngressFIFO列队的情况下直接送入SDH网络,然后PAUSE帧以最快速度到达远端设备,以中止远端以太网中用户的数据发送。同样,如果本地E-gressFIFO缓冲器数据满,IngressFPGA构造的PAUSE帧也不经IngressFIFO列队而直接向远端发送。

2 当本地IngressFIFO缓冲器数据满时,E-gressFPGA向本地以太网控制芯片发送PAUSE通知,以太网控制芯片接收到通知后,向本地以太网用户发送PAUSE帧以停止其数据发送。同样,如果是从SDH网络上接收到PAUSE帧,则EgressFPGA立即发送PAUSE通知到本地以太网控制芯片,再由以太网控制芯片的PAUSE帧中止用户发送的数据。

3 在MCU控制下,EgressFPGA和IngressFPGA都具有XON/XOFF控制功能,可使整个流量控制更加快捷、合理,有利于保证数据的完整和正确。

本设计中,两片FPGA都可以对SDRAM进行控制,并对其存储数据的容量进行计数,同时生成数据存储位置列表,指示数据包在存储器中的位置以提供给MCU查询。

4.3 光接口部分

光接口部分选用杰尔系统公司(Agere System)的成帧器 TDAT021G2。该成帧器与FPGA的接口为UTOPIA。成帧器支持净荷的上下路,同时可为其发送处理的数据生成CRC-16/32校验或检查接收数据的校验和是否有效。在SDH网络侧支持四路的STS-3/STM-1或者两路的STS-12/STM-4,本设计中采用后者。

EoS嵌入式系统框图见图5,需要说明的是,整个系统各个部分均有MCU接口,可以使用一块低成本的51单片机80C320进行整个系统的协调控制。

5 结束语

本文所提出的嵌入式系统可用作各种通用和专用SDH网络和以太网设备的连接,如果在系统中加入解密加密功能,还可以构建基于EoS技术的虚拟网VPN,具有很好的应用前景。

EoS嵌入式系统框图见图5,需要说明的是,整个系统各个部分均有MCU接口,可以使用一块低成本的51单片机80C320进行整个系统的协调控制。

5 结束语

本文所提出的嵌入式系统可用作各种通用和专用SDH网络和以太网设备的连接,如果在系统中加入解密加密功能,还可以构建基于EoS技术的虚拟网VPN,具有很好的应用前景。

上一篇:一种多协议串行通信接口的设计方法

下一篇:用模拟电视传输发射设备传送数字电视

- 热门资源推荐

- 热门放大器推荐

MCP639T-E/ML

MCP639T-E/ML

京公网安备 11010802033920号

京公网安备 11010802033920号