上世纪90年代中期,英特尔决定把SRAM整合到自己的处理器中,这给世界各地的独立式SRAM供应商带来“灭顶之灾”。最大的SRAM市场(PC高速缓存)一夜之间销声匿迹,只留下少数细分市场应用。SRAM的“高性能存储器(访问时间短、待机功耗小)”价值主张因其较高的价格和容量限制(目前的最高容量是288Mb)而高度受限。由于SRAM每个单元有四到六个晶体管,几乎无法与DRAM和闪存竞争(这两种存储器每个单元只有1个晶体管);每个单元的晶体管数越少就意味着板容量和成本越低。因此,对构成98%的市场总额的传统存储应用而言,SRAM是一种不切现实的解决方案。

关键字:SRAM IoT 可穿戴 赛普拉斯

引用地址:SRAM在新一代IoT和可穿戴嵌入式设计中的作用

自英特尔开始嵌入SRAM以来,大多数SRAM供应商已经做出相应调整,或关闭工厂,或丰富SRAM之外的其它产品组合。对SRAM的运用则转向要求高性能的专门应用,主要包括工业、汽车和国防领域。SRAM的整体市场在2002年到2013年间的年均复合增长率(CAGR)为-13%。然而,若认为这种技术已经日薄西山还为时尚早。实际上,由于种种因素的作用,在未来几年我们预计将会看到长期被冷落的SRAM东山再起。在本文中,我们将探讨让SRAM重获新生的技术进步以及使之能够满足未来需求的SRAM技术发展趋势。

SRAM回归主流嵌入式设计

SRAM回归主流设计的动力非常耐人寻味,力图取代SRAM的潮流忽然发生逆转。英特尔决定嵌入SRAM,这在当时是个非常英明的决策。SRAM不仅成本效益更高,而且还是技术一流的解决方案。与外部SRAM相比,嵌入式SRAM的存取时间更为出色,要知道对于高速缓存存储器而言,存取时间是最关键的因素。

自那时起到现在,处理器功能变得更加强大,而且尺寸越来越小。随着处理器的功能日渐强大,它们要求高速缓存存储器性能也要有大幅改善。但与此同时,随着每一代新工艺节点的问世,不断增大嵌入式高速缓存存储器的容量成为一项越来越艰巨的挑战。SRAM拥有六晶体管架构(逻辑区一般为四晶体管/单元)。这意味着随着工艺节点的缩小,每平方厘米的晶体管数量将会极高。这样的高晶体管容量可能导致许多问题,包括:

发生软错误的几率增大:随着工艺技术从130nm缩小到22nm,软错误率预计将增长七倍。

产量降低:由于晶体管容量增大,加上位单元不断缩小,SRAM的面积更容易受工艺变化所造成的瑕疵的影响。这种瑕疵会降低处理器芯片的总产量。

功耗增加:如果SRAM位单元必须与逻辑位单元的大小相同,那么SRAM晶体管的尺寸就需要缩小到小于逻辑晶体管。而晶体管尺寸的缩小会导致漏电流增大,最终导致待机功耗增大。

有两种途径可以解决这个问题。一种方法是为处理器中或片上系统中的SRAM面积和逻辑面积采用不同的工艺技术节点。但这样做的后果则是处理器的大部分面积由SRAM构成。如果是这样,缩小处理器芯片的理由就无法成立。另一种方法则是把SRAM与处理器或控制器分开。有一些技术创新实际上正在加快这种替代方案的实现。

可穿戴电子产品中的SRAM

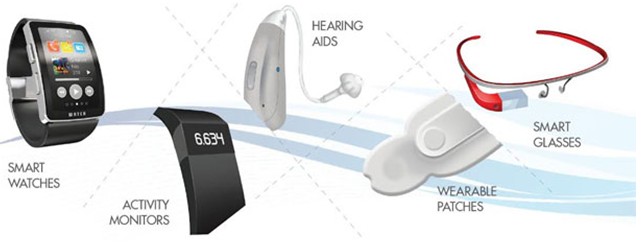

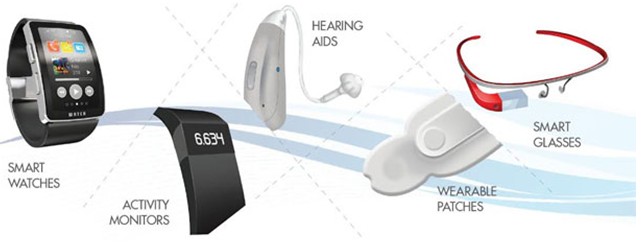

当今世界的微控制器(MCU)已经广泛应用于各种设备中。我们现今正在经历一个重大电子产品发展趋势,那就是可穿戴电子产品(图1)。对于智能手表和健康腕带这样的可穿戴产品来说,尺寸和功耗是关键因素。由于电路板尺寸受限,MCU必须精简小巧,并且能够借助便携式电池提供的微弱电力运行。

图1:可穿戴电子产品的要求正在推动SRAM的复兴

在上述要求下,片上高速缓存的容量相当有限。在将来的几代产品中,我们预计会看到可穿戴产品的功能将得到进一步丰富。这样一来,片上高速缓存的容量将不敷使用,从而带来对外部高速缓存的需求。在所有可用的存储器中,SRAM是用作外部高速缓存的最佳选择。因为它与DRAM相比待机电流消耗较低,而且其存取时间也比DRAM和闪存更短。

但是,要装配到微小的可穿戴产品电路板上,SRAM将需要进一步发展。对现有的并行SRAM而言,存在下列问题:

· 与MCU通信所需的引脚数过多;

· 尺寸过大,不适合PCB。

物联网和SRAM

过去几十年里,SRAM领域已衍生出两个不同的产品线:高速率和低功耗。每个产品线都有着各自特有的功能、应用和价格。需要使用SRAM的设备要么需要它的高速特性,要么需要它的低功耗特性,但从来不是两者兼具。然而,对采用便携式电源供电并用以执行复杂操作的高性能低功耗设备的需求正在不断增长。这种需求背后的动力来自新一代医疗设备、手持设备、消费类电子产品、通信系统以及工业控制器,这些设备均受物联网(IoT)驱动。

IoT正朝着两个不同的方向发展:智能可穿戴产品和自动化技术。正如前文我们所讨论的,可穿戴产品使用低功耗的小尺寸SRAM最为适合。同时,物联网的发展还会影响到工业、商业和大规模运营以及个人住宅、大型工厂乃至整个城市的自动化。SRAM采用小型封装,能够在降低功耗的同时保持高速性能,其将为IoT应用带来重要价值。

许多主要厂商提供的微控制器通过诸如深度低功耗(Deep Power-Down)和深度休眠(Deep-Sleep)等特殊的低功耗模式,已经能够满足对此类跨界设备的不断变化的需求。在这些模式下,外设和存储器模块也有望节省功耗。因此,要成为IoT设计的优先选择,SRAM的发展必须能够让客户不必在性能和功耗之间权衡取舍。

SRAM的发展如此之快,很明显只要独立式SRAM制造商能够通过创新让自己的产品满足新一代应用需求,激动人心的时刻就在未来等待着他们。SRAM的主要创新领域包括:

缩小芯片尺寸:这要求工艺技术的进步和封装技术的创新;

减少引脚数量:目前大多数SRAM使用并行接口。市场上的串行SRAM只有低容量产品。需要生产容量更高的串行SRAM;

功耗更低的高性能芯片;

片上软错误校正。

在下面的章节中,我们将介绍SRAM设计的一些关键创新,这些设计创新促使嵌入式系统开发人员考虑把SRAM用于嵌入式可穿戴产品、IoT和其它嵌入式系统应用。

芯片级封装

芯片级封装(CSP)[4]是一种缩小芯片尺寸的强大技术。根据规格要求(J-STD-012),要满足“芯片级”要求,整体封装部分的面积不能超过晶片面积的1.5倍,并且线性尺寸不能超过晶片尺寸的1.2倍。相比之下,对于采用标准封装的晶片,整体芯片面积可以是晶片面积的十倍。因此芯片级封装有助于缩小芯片的尺寸。另外通过压缩工艺节点也可以实现类似的尺寸缩小。但就SRAM而言,转而采用较小的工艺节点会带来风险,具体在上文中已作解释。

面积的缩小可通过取消第一级封装来实现,其中包括引脚框架、管芯连接、焊线以及铸模化合物。CSP芯片大多采用晶圆级封装,将封装材料直接堆放在晶圆片上。引脚分布类似于球栅阵列封装(BGA),封装上的焊接凸点起引脚作用。通过缩小工艺节点可获得类似的尺寸缩小效果。

对于可穿戴应用中空间有限的电路板来说,CSP SRAM明显将是最佳选择。与仅次于它的备选方案(购买一块SRAM管芯,然后使用高级多芯片封装(MCP)技术将它与MCU管芯封装在一起)相比,将CSP SRAM纳入设计要便捷得多。目前,CSP SRAM还没有投入量产,有些供应商将其作为定制选项提供,可能是因为目标市场(可穿戴)还没有超越嵌入式领域。不过在 SRAM 市场中,大多数主要厂商都可为他们的很多其它产品提供CSP选项。例如,赛普拉斯半导体已针对其PSoC等产品系列提供了CSP版本。因此,对于制造商来说,将这种功能延伸至SRAM应该不难。

引脚数更少

在SRAM的功耗低于闪存和DRAM时,使用SRAM进行存储器扩展的主要问题是其并行接口。尽管并行接口能实现更快的读写速度,但有太多的IO需要连接。例如,如果将一个1Mb SRAM (64Kb x16) 与一个MCU连接,所需的IO数量将会是32个(16个地址,16个数据)。进行多路复用可将该数字减少至24。但容量每增加一级(2M、4M、8M等),引脚数就会增加1个。

极小可穿戴电路板上用来连接SRAM的IO数量有限,因为小型MCU的封装引脚数量少。要与这些MCU连接,SRAM必须突破传统的并行接口。串行闪存和EEPROM等的成功增强了串行存储器选项的市场需求。MCU使用嵌入式高速缓存已有很多年了,因此对于串行SRAM的需求直到最近几年才被发觉。串行SRAM可实现更便捷的接口连接,更少的引脚使用(单路SPI用两个,双路SPI用两个,四路SPI用四个)。此外,所需的IO数量不会随容量增加而增多。

目前,我们的串行SRAM容量低,存取速度相对较慢(存取时间达25ns,容量为1M)。在不久的将来,我们将有望刷新这两个参数。随着可穿戴产品进入全新时代,我们可能会希望MCU完成更为复杂的工作。在这种情况下,具有更高吞吐量的更高容量高速缓存/高速暂存存储器会十分有用。因此,串行SRAM向更高速和更高容量的方向发展将对该市场十分有利。使用CSP封装缩小尺寸再加上串行接口,SRAM将会成为可穿戴产品中高速缓存及高速暂存存储器的强大选项。

高性能,低功耗

当前有两个不同系列的异步SRAM:快速SRAM(支持高速存取)和低功耗SRAM(低功耗)。从技术角度看,这种权衡是合理的。在低功耗SRAM中,通过采用特殊栅诱导漏极泄漏(GIDL)控制技术控制待机电流来控制待机功耗。这些技术需要在上拉或下拉路径中添加额外的晶体管,因此会加剧存取延迟,而且在此过程中会延长存取时间。在快速SRAM中,存取时间占首要地位,因此不能使用这些技术。此外,要减少传播延迟,需要增大芯片尺寸。芯片尺寸增大会增大漏电流,从而增加整体待机功耗。

到目前位置,典型SRAM应用接受这种权衡:电池供电应用使用低功耗SRAM(降低性能),有线工业高性能应用则使用快速SRAM。不过,对于物联网及其它众多高级应用来说,这种权衡不再适用。主要原因是对于大部分这些应用而言,不仅高性能很重要,同时还必须限制待机功耗,因为这些应用大多采用电池供电工作。非常幸运的是,SRAM正在缩小这两个系列之间的性能差距,正逐渐发展成具有这两种优势的单芯片产品。

微控制器很久以前就有了深度睡眠工作模式。这种工作模式有助于为大部分时间都处于待机状态下的应用省电。该控制器可在正常工作中全速运行,但事后则进入低功耗模式,以便节省电源。使所连接的SRAM也具有类似的工作模式很重要。具有深度睡眠工作模式[5]的异步快速SRAM是这类应用的理想选择。这种SRAM芯片有一个附加输入引脚,有助于用户在不同的工作模式(正常、待机和深度睡眠)间切换。因此可在不影响性能的情况下管理低功耗。http://www.cypress.com/?docID=48906。

片上纠错功能

存储器工艺技术的提高可改进性能与功耗,因此更低的电压和更小的节点电容会让这些器件更容易出现软错误。如今,CMOS 工艺已经缩小了尺寸,地外辐射和芯片封装都会导致越来越多的故障。一般使用纠错码(ECC)软件或冗余(即多个SRAM存储相同的数据)方式应对软错误,特别是在可靠性一直都极为重要的系统中,例如医疗、汽车和军事系统。然而,这种方式非常昂贵,需要额外的电路板空间。

主要SRAM制造商现已开始直接在芯片上实施纠错特性[6]。要在现代芯片级半导体存储器上限制软错误影响,可使用两种架构增强方法:片上ECC和位交错。通过片上ECC,便可将用于实施错误检测和单个位错误校正的软件硬编码在SRAM中。有些制造商甚至还提供一个额外的错误引脚选项,用以指出单个位错误的检测与校正情况。

另一方便,位交错可用来限制多位错误的影响(即单个能量粒子翻转多个位)。位交错的工作方式是将相邻的位线安排至不同的字寄存器。这样可将多位错误转换为多个单个位错误,随后可通过片上ECC进行校正(进一步了解如何减少和校正软错误)。

SRAM与未来

SRAM技术将迎来激动人心的全新时代。技术趋势与发展都有利于该技术回暖,扭转多年来使用量下降的颓势。支持ECC功能的芯片现已投入量产。支持片上电源管理的快速SRAM也已上市。此外,串行SRAM也已投入量产,但大多数都支持低容量应用,因此目前在速度上还无法与并行方案相匹敌。不过,串行市场的现有厂商(Microchip和On-semi)恰好主要都是MCU制造商。传统SRAM公司尚未推出串行SRAM。随着更多公司进入该市场,我们将有望看到创新技术的快速出现。

关于产品生命周期的传统市场观点是:产品成熟期过后就是衰退,然后是消亡。从SRAM每年的负复合增长率以及大多数供应商退出该市场的事实来看,该产品应划为“衰退”期。然而不管是今天我们目睹的SRAM复兴,还是针对未来预测的,都需要我们重新审视普通产品生命周期的传统理念。

参考资料

1. 维基百科:半导体器件制造

2.《22nm工艺对SRAM内中子引起的软错误的影响》作者:Eishi Ibe、Hitoshi Taniguchi、Yasuo Yahagi、Ken-ichi、Shimbo和Tadanobu Toba

3.《漏电流:摩尔定律遇到静态功耗》,摘自《IEEE 计算机》2009年1月刊

4. 应用手册AN69601《赛普拉斯晶圆级芯片级封装指南》

5. 应用手册AN89371《赛普拉斯异步PowerSnooze SRAM帮助节省电源》

6. 应用手册AN88889《用赛普拉斯异步SRAM减少单事件翻转》

Reuben George在赛普拉斯半导体公司的存储器产品部从事产品市场营销工作。他在印度拉贾斯坦邦皮拉尼的贝拉理工学院 (BITS)获得电气电子工程学士学位。

Anirban Sengupta现任赛普拉斯半导体公司的定价经理。他分别在印度国家技术学院(National Institute of Technology)和印度普纳管理与人力资源开发合作关系中心(SCMHRD)获得电气工程学士学位和市场营销MBA。

上一篇:美高森美推出基于SLC的最高容量安全固态硬盘

下一篇:PMC隆重亮相2015美国闪存峰会(FMS) 展示新一代NVMe方案

推荐阅读最新更新时间:2024-05-03 14:56

Nordic 蜂窝物联网SiP通过认证助力中国电信NB-IoT发展

Nordic Semiconductor宣布其屡获殊荣并且集成了LTE-M/NB-IoT调制解调器和GPS的nRF9160低功耗系统级封装(SiP)产品已经通过认证,可用于中国电信的NB-IoT网络。根据全球行业机构GSMA的数据,中国电信目前通过40多万个NB-IoT基站为超过5,000万客户提供服务,这相当于接近98%的全国覆盖率。这项认证使得部署了nRF9160 SiP的产品设计能够为中国电信客户实现NB-IoT连接。 nRF9160是经认证用于全球蜂窝物联网应用的低功耗SiP器件,其紧致封装中包含了集成RF前端(RFFE)的多模式LTE-M/NB-IoT调制解调器、GPS和电源管理,其中的64 MHz处理器带有1 MB

[网络通信]

物联网部署形式下:MCU将迎来三大发展趋势

物联网将是下一个推动世界高速发展的“重要生产力”,是继通信网之后的另一个万亿级市场。物联网行业的快速发展是驱动MCU发展的一大动力。

其中又因为汽车驾驶信息系统、油门控制系统、自动泊车、先进巡航控制、防撞系统等ADAS系统对于32位MCU的大规模需求,将刺激32位MCU的大幅增长。此外,物联网领域的智能应用正方兴未艾,比如医疗电子用品(如智能血糖机、电子血压计等)、个人健康监测产品(如智能手环、智慧手表、智能衣、心率带等等)这些需要低功耗、长时间使用、无线通信的产品,也必须倚赖MCU来实现。微控制器(MCU)作为物联网的核心零组件,无论在市场规模上还是技术上都将获得进一步发展,那么,在当前物联网快速部署的大形势下MCU自身发展

[单片机]

爱立信:2018 年物联网装置将超过手机

爱立信的行动网路报告指出物联网的趋势,依照爱立信掌握到数据推估,2021 年物联网装置数量将达到 160 亿,而到了 2018 年手机数量和物联网装置数量将会黄金交叉。

每半年推出的爱立信行动趋势报告,可说是电信领域相当权威的行动网路应用报告,这次 2016 年上半年的调查的成果是第 10 次发布。报告中手机网路的基本资讯,2016 年 Q1 有 74 亿的行动电话门号数,其中行动宽频有 37 亿,智慧型手机有 34 亿。至于全球使用者有 50 亿人,增加最多的国家则是印度,有 2,100 万人。

▲ 这次爱立信行动趋势报告的重点。

2015 到 2021 年之间,物联网将以 23% 的

[手机便携]

IEEE:AI、机器学习、5G、IoT成了2021年最重要技术

近日,IEEE(电气电子工程师学会)发布了《IEEE全球CIO、CTO访问调研:2021年的机遇和挑战,以及关键的科技趋势》。本次调研在美国、英国、中国、印度和巴西五个国家进行,共对350名CIO(首席信息官)和CTO(首席技术官)进行访问。 据IEEE全球CIO、CTO调研结果显示,32%的受访者认为人工智能和机器学习,将成为全方位影响2021产业发展的关键技术。超过一半(56%)的中国受访者认为,人工智能和机器学习技术在全球新冠疫情恢复中发挥着最关键的作用。20%的全球受访者认为5G将会是2021年最重要的科技,物联网(14%)紧随其后。 IEEE会上,上海科技大学杨旸教授表示,5G和物联网技术2021年将在千行百业的数字化转

[手机便携]

透气可穿戴皮肤传感器 未来用于长期的健康监测

可穿戴 电极用于监测心率和其它的关键健康信号近年来取得了进展,新一代的设备会采用更轻盈、更有伸缩性的材料直接粘附在皮肤上,以便有更好的敏感度,提供更精确的测量。然而,尽管使用在这种设备上的超薄膜和橡胶板虽然也可以很好的贴合皮肤,但是这些材料的透气性较差,并且被认为长期使用是不够安全的。皮肤测试表明优质的、可拉伸的材料可以防止出汗、皮肤不透气、以及刺激或炎症,这些不良反应会产生持续的生理或心理影响。下面就随网络通信小编一起来了解一下相关内容吧。 日本东京大学发布了一款防过敏电子传感器,可以佩戴在手背的皮肤上,持续数周而不会有任何的不适感,因为它会轻薄到你忘记了它的存在。这款可拉伸的电极由透气的纳米网络组成,为开发可以在一

[网络通信]

Google X掌门:价格影响可穿戴设备普及

上个月在《Vanity Fair》举办的会议上发言时,谷歌秘密的Google X研究实验室掌门Astro Teller表示,说服人们在脸上或身体其他部位佩戴智能设备是件难事。 他说,厂商需要使智能设备对用户有用,才能吸引用户佩戴。但还有另外一个问题:包括从智能眼镜到智能手表在内的可穿戴设备需要足够便宜——相当便宜,才能被主流用户接受。 Teller在谷歌总部接受采访时说,“产品价格每下调一半,认真考虑购买的人就会增长约10倍”,这意味着,对于大多数可穿戴设备来说,要成为对用户有吸引力的产品,需要“两次把价格削减一半”。 他表示,对于一些产品,例如价格为30或40美元(约合人民币184或246元)的计步器,大幅下

[物联网]

物联网身陷发展困局 地方政府逃避责任

物联网是一个比互联网规模更大的万亿级产业,然而《经济参考报》记者在北京、上海、江苏等地调研时发现,从事物联网产业推广的中国企业尚未敲开这座富矿,并没有尝到物联网发展给他们带来的甜蜜,体验更多的反倒是苦苦寻求市场突破的艰难。

业内人士分析,究其原因主要有“三难”:传统思维下新技术应用难、高成本供给与小规模需求对接难、条块分割市场切入难。从更深层次来说,主要是由于政府未能在产业尚未成熟时期给以需求牵引和政策支持,助推幼小产业突破发展瓶颈。

地方政府普遍存不信任

“一些地方政府的视野非常狭隘,只支持已经做成了的事情,政府就喜欢等着摘桃子。因为这样没有风险,不用承担责任。”

北京天地互连信息技术有限公司

[网络通信]

三星半导体方案实现SRAM器件高可靠性运行及微缩化

集微网消息,微缩技术可以用于提高半导体器件的密度,并逐渐发展了各式各样的多栅极晶体管,这种晶体管通常具有鳍形状和纳米线形状的多沟道有源图案,图案形成于芯片衬底上,在有源图案上还设置有栅极结构。 由于这种多栅极晶体管利用三维沟道来实现,因此比较容易进行微缩。此外,即使不增加多栅极晶体管的栅极长度也可以提高电流控制能力,并可以有效地抑制沟道区的电势受漏极电压影响的短沟道效应(SCE)。 而随着目前2~3nm芯片技术的深入研究以及半导体器件的节距尺寸减小,需要确保半导体器件中的接触之间的电容减小和电稳定性。为此,三星在2021年7月6日申请了一项名为“半导体器件”的发明专利(申请号:202110761662.0),申请人为三星电子株式会

[手机便携]

小广播

热门活动

换一批

更多

最新手机便携文章

- 消息称苹果、三星超薄高密度电池均开发失败,iPhone 17 Air、Galaxy S25 Slim手机“变厚”

- 美光亮相2024年进博会,持续深耕中国市场,引领可持续发展

- Qorvo:创新技术引领下一代移动产业

- BOE独供努比亚和红魔旗舰新品 全新一代屏下显示技术引领行业迈入真全面屏时代

- OPPO与香港理工大学续约合作 升级创新研究中心,拓展AI影像新边界

- 古尔曼:Vision Pro 将升级芯片,苹果还考虑推出与 iPhone 连接的眼镜

- 汇顶助力,一加13新十年首款旗舰全方位实现“样样超Pro”

- 汇顶科技助力iQOO 13打造电竞性能旗舰新体验

- BOE(京东方)全新一代发光器件赋能iQOO 13 全面引领柔性显示行业性能新高度

更多精选电路图

更多每日新闻

更多往期活动

11月13日历史上的今天

厂商技术中心

基于物联网技术的现代物流管理研究

基于物联网技术的现代物流管理研究 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号