1 系统概述

本设计利用DSP开发板的强大运算能力,实现了多种需要进行大量运算的信息安全算法。实现了开机用户认证、语音保密通信[1][2]、文字信息加密传输、信息隐藏传输[3]、跳频通信[4]、信息安全存储备份、定时锁机和终端销毁,七项安全功能。整个设计基于ICETEK-VC5509-A开发板,系统的硬件部分还外加了无线射频模块nRF24L01[5]、8×8键盘和128×64蓝屏液晶。芯片ZLG7289B[6]用于键盘扫描管理,液晶的驱动采用MEGA16[7]单片机,整个系统不但实现了高质量的保密语音通信,还具有良好的人机交互功能。

系统利用上电到输入密码时间的不确定性,随机生成用户私钥,通过Diffie-Hellman[8]密钥交换体制(ECC实现)生成会话密钥。为了提高保密通信的安全性和灵活性,系统实现了可供选择4种加密算法AES[9]、RC5[10]、IDEA[11]、KASUMI[12]和可配置参数的LSB[13]信息隐藏算法。我们自主开发实现了USB驱动[14],使得开发板能够和PC机直接通信,这也为信息存储备份提供了便捷。除此之外,系统能够设定自动锁机的时间。

整个系统的信号传输模型如图1-1所示。

图1-1 系统传输模型

2 方案设计与比较

2.1 系统安全方案

方案一:预置密钥,定期更换密钥,用对称密码体制进行数据加密。PC机通过USB向终端预置密钥,通信时采用预置的密钥进行对称加密。统的安全性在一定程度上依赖于密钥的更新周期,而在实际应用中,缩短密钥的更新周期比较麻烦。

方案二:密钥交换基于公钥密码体制,数据加密基于对称密码体制。PC机通过USB向终端写入公钥算法的参数。开机后,A、B随机生成自己的私钥,计算得到自己的公钥,并向对方公开自己的公钥。A使用自己的私钥和B的公钥生成会话密钥,B通过自己的私钥和A 的公钥生成会话密钥,且会话密钥相同。通信结束后清除该次生成的私钥、公钥和会话密钥,下次开机则重复上述会话密钥的生成过程。

方案二的实现较方案一更为复杂。但考虑到方案二的安全性更高,且方案二在保证会话密钥安全性的前提下,有效的缩短了会话密钥的生存期,提高通信的安全性。另外,还可以通过PC机定期更新公钥参数。再加上方案二更适合于无线移动通信,符合我们的设计背景,因此我们采用方案二。

2.2 语音编码方案

方案一:采用G.721编码[15][16]。它结合了ADM的差分信号与PCM的二进制码方法,是一种性能较好的波形编码。ADPCM的复杂度较低,编码前后的压缩比为4比1,其主要思想是用差值代替绝对值。

方案二:采用基于码激励线性预测算法的开源语音编解码Speex[17][18]。Speex主要面向Internet上的VoIP(Voice over Internet Protocol)语音通信。其主要设计目标是为了提供高质量和低比特率的语音编码。Speex可以在同一个比特流中对语音信号实现窄带(8kHz)、宽带(16kHz)和超宽带(32kHz)的压缩;压缩比能够达到16比1。Speex虽然有诸多优点,但是Speex编解码算法复杂,运行该算法需要的硬件配置较高。

我们所用的射频模块的传输码速率为2Mbps,且信道完全能够保证通信质量,从理论上说,上述2种方案都适用。我们在DSP开发板上实现了speex和G.721的编解码,实际测试发现speex编解码会带来很大的延迟,原因在于speex编解码算法比较复杂。虽然我们已经最大程度的精简了speex算法,比如:将算法的复杂度置为最低、设置编解码质量参数为最低、关闭了VBR变波特率特性、关闭了知觉增强特性和AEC回声消除等特性,都不能解决延迟很大的问题。除此之外,speex编解码需要大量的浮点计算,我们使用的开发板为TIC55XX系列的定点DSP,实现speex编解码耗时较多;再者,speex编/解码所能处理的最小帧长为160个样点,因此,会带给系统很大的延迟。G.721编解码能够实现基本的语音通信,但通信质量一般,再考虑到本系统以语音信号作为信息隐藏的载体,经语音编解码之后不能还原隐藏信息,因此我们最终选用PCM编码。

3 系统的实现

3.1 硬件实现

3.1.1 系统硬件架构

终端的硬件架构图如图4-1所示,主要由ICETEK—VC5509—A评估板、nRF24L01射频模块、128×64液晶、8×8键盘、MEGA16单片机控制模块组成。

图4-1 硬件架构图

3.1.2 射频收发模块

射频模块采用nRF24L01,其电路图如图4-2所示。

图4-2 射频模块电路图

3.1.3 键盘扫描电路

我们使用键盘扫描管理芯片ZLG7289B[18]来进行键盘的管理。ZLG7289B可同时扫描多达64只按键。其电路图如图4-3所示。

图4-3 键盘扫描电路图

3.2 软件实现

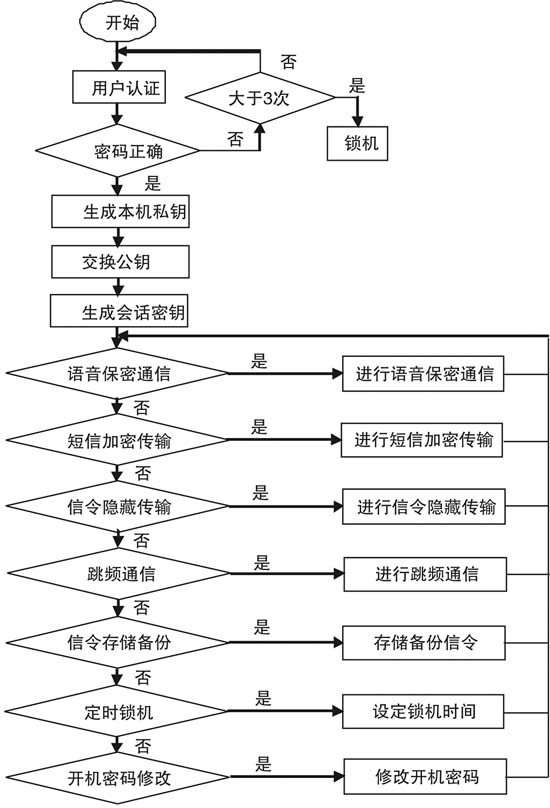

系统的软件设计采用C语言,所有的程序在CCStudio v3.3环境下开发的。软件由主程序和一些子程序构成,子程序主要包括USB驱动程序、键盘扫描程序、液晶驱动程序和射频通信程序。主程序流程图如图4-4所示。

图4-4 主程序流程图

4 特色与创新

①60位私钥的ECC算法实现Diffie-Hellman密钥交换

②一键即通的语音保密通信

③4种加密算法任意选择的保密通信

④实现键盘编辑短信并加密传输

⑤可配置参数的信息隐藏传输

⑥收发机动态协商进行跳频通信

⑦实现了USB的驱动,PC机和开发板直接通信

⑧蓝色液晶屏幕显示,人机界面友好

⑨射频收发模块实现了2.4G的无线通信

上一篇:IDC预计2009年亚洲PC销量将停止增长

下一篇:SiliconBlue宣布65纳米iCE65 FPGA量产

推荐阅读最新更新时间:2024-05-02 20:46

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

无线通信中的智能天线 (J.C. Liderti, Rappaport)

无线通信中的智能天线 (J.C. Liderti, Rappaport) 控制之美(卷1)——控制理论从传递函数到状态空间

控制之美(卷1)——控制理论从传递函数到状态空间

京公网安备 11010802033920号

京公网安备 11010802033920号