在信号处理过程中,经常采用DSP+FPGA协同处理的方法。是因为DSP虽然可以实现较高速率的信号采集,但其指令更适于实现算法而不是逻辑控制,其外部接口的通用性较差。而FPGA时钟频率高、内部延时小,全部控制逻辑由硬件完成,速度快、效率高,适合于大数据量的传输控制,可以集成外围控制、译码和接口电路,在高速数据采集方面有着DSP以及单片机无法比拟的优势,但缺点是难以实现一些复杂的算法。因此,若采用DSP+FPGA协同处理的方法,便可以使DSP的高速处理能力与FPGA的高速、复杂的组合逻辑和时序逻辑控制能力相结合,达到互补,使系统发挥最佳性能。

在目前的信号采集及测试系统中,由于应用背景的复杂,经常需要对多路信号进行采集,有的甚至需要对多路单端及差分信号进行采集,在某些情况下,为测试分析的方便,还需要对采样率进行改变。文中介绍了一种采用DSP+FPGA协同处理的方法,并主要利用ADS8517这一A/D转换芯片来实现多路可以选择单端或差分输入的信号采集系统的设计方法。

1 系统实现功能

该系统可以实现32个通道单端信号或16个通道差分信号的采集输入,由DSP控制输入信号是单端信号还是差分信号,以及各自使能输入的通道,其中单端信号最多使能输入32个通道,差分信号最多使能输入16个通道。A/D在各个使能通道间采用类似时分复用的方法进行轮寻采样,A/D采样频率200 kHz,DSP可设置采样率分频值,对采样率进行改变,假如DSP设置采样分频值为D,使能输入通道数为N,则每个通道实际采样率为200 kHZ/(D·N)。

2 系统硬件设计

根据以上功能要求,整个系统的设计思路如图1所示。其中DSP采用TI公司的TMS3206713B,FPGA采用Altera公司的CycloneIII系列,A /D采用TI公司的ADS8517。ADS8517的主要性能:(1)16位分辨率;(2)采样频率:200 kHz;(3)模拟输入范围±10 V;(4)输出有串行和并行两种方式。

在整个系统中,FPGA根据DSP对各个通道是单端或者差分的设置,以及各个通道使能与否和采用率分频值的设置,控制ADS8517以及多路选择器,将A/D输入的数据以及其对应的通道存入一个FIFO中,当FIFO半满时向DSP发送中断,由DSP读取FIFO中A/D的采样数据及其对应的通道号。可以看出,设计重点主要集中在多路选择器的设计以及FPGA中硬件逻辑的设计。

2.1 多路选择模块设计

根据系统要实现的功能,多路选择模块的设计采用如图2所示的设计思路,其中16选1多路器和4选1多路器分别采用ADI公司的ADG1206和ADG1204。由FPGA控制这些多路选择器来选择通道以及单端/差分模式,在设计选择差分信号时,为方便,只支持A0~A15通道和A16~A31通道依次对应的差分,而不支持A0~A15通道中任意一个通道和A16~A31通道中任意一个通道的差分。

2.2 FPGA部分的设计

2.2 FPGA部分的设计

由于DSP数据总线为32位双向总线,所以在FPGA中需要设计一个总线的三态控制器,来控制总线的输入输出,这部分设计较简单,模式相对固定,应用已成熟。

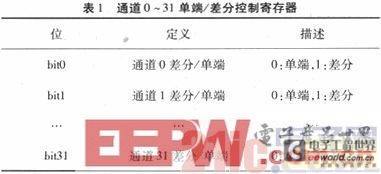

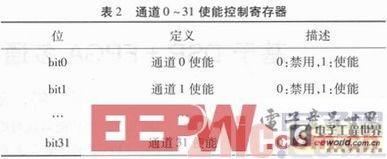

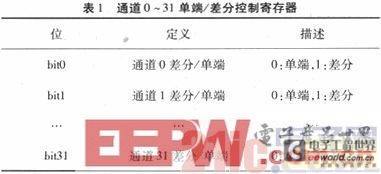

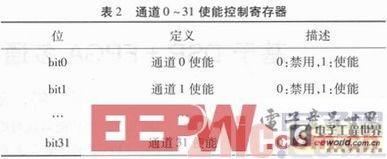

对于DSP发出的各个通道单端/差分控制,各个通道使能控制以及采样率分频值设置这些控制信息,由在FPGA中开辟出的3个32位寄存器来存储。通道单端/差分控制寄存器和通道使能寄存器的定义如表1和表2所示,采样率分频值设置寄存器中的32位无符号2进制整数表示相应的分频值。

当DSP的控制信息设置好以后,根据通道单端/差分控制寄存器以及通道使能控制寄存器中的内容,建立一个使能通道索引表,索引表中字的个数等于使能的通道数,每一个字的字长为6位,依次将使能的通道号转换成二进制无符号数后放入表中各个字的低5位,每个字的高位记录相应的通道是单端还是差分,‘0’表示单端,‘1’表示差分。

设计采用ADS8517并行输出的工作模式,按照图3所示的并行输出方式时序图对其进行控制,其中

和BYTE信号为ADS8517的输入控制信号,

和BYTE信号为ADS8517的输入控制信号, 的下降沿表示一次采样的开始,

的下降沿表示一次采样的开始, 为高电平时表示可以读取A/D的输出数据,输出为并行8位输出,当BYTE信号为低电平时输出高8位,反之则输出低8位,从而完成16位分辨率的输出。

为高电平时表示可以读取A/D的输出数据,输出为并行8位输出,当BYTE信号为低电平时输出高8位,反之则输出低8位,从而完成16位分辨率的输出。 为ADS8517输出信号,为低电平时则表示本次A/D转换正在进行,为高电平时表示本次转换完成,因此当

为ADS8517输出信号,为低电平时则表示本次A/D转换正在进行,为高电平时表示本次转换完成,因此当 和

和 同时为高电平时,便可以读取本次A/D采样转换后的数据。

同时为高电平时,便可以读取本次A/D采样转换后的数据。

ADS8517控制以及通道切换控制模块在按照图3所示的时序控制过程中,要根据采样率分频值设置寄存器中的值控制两次采样之间的时间间隔,即控制两个相邻

信号下降沿之间的时间间隔,从而改变采样率。在控制多路选择模块进行通道切换时,根据建立的索引列表依次切换通道,切换要在图3中两个相邻信号低脉冲之间进行,这样才能确保当A/D采样时,通道已经切换完毕,输入信号已稳定,从而保证采样的准确性。

除此之外,在FPGA中开辟一个字长为32位的FIFO,低16位存入A/D采样的数据,高16位存入该数据对应的通道号,FIFO半满,则给DSP发中断,由DSP将A/D采样后的数据读出,以便后续处理。要注意的是,FIFO深度不能设置得太浅,否则会很快达到半满,导致DSP对中断响应不过来。

3 结果验证

按照以上设计思路,完成硬件电路、FPGA内逻辑和DSP的程序设计,使用QuartusII中的在线逻辑分析仪SignalTapII Logic Analyzer对结果进行采样分析,图4所示为在DSP设置使能通道为30和31,并且均为单端的条件下采到的结果,与期望结果一致,类似这样通过多次改变控制条件采样分析发现,该系统可以正确地实现之前所描述的功能,从而验证了该设计的合理正确性。

4 结束语

由于DSP+FPGA协同工作平台的优越性,使其在信号处理中的应用越来越广泛。文中介绍了一种基于DSP+FPGA的平台,并利用ADS8517构成的一个具有多通道单端/差分的A/D信号采集系统。该系统的使能通道数可选,单端/差分方式可设置,采样率可改变,机动灵活,可以应用在诸多信号采集以及测试系统中。

关键字:FPGA DSP

引用地址:

基于FPGA+DSP的多通道单端/差分信号采集系统设计

推荐阅读最新更新时间:2024-05-02 23:04

瑞萨全新PMIC参考设计加速FPGA和SoC产品问市

全球领先的半导体解决方案供应商瑞萨电子株式会社宣布推出三款易于使用的电源管理IC(PMIC)参考设计,用于为Xilinx Artix-7、Spartan-7系列FPGA以及Zynq-7000 SoC的多个电源轨供电,并可选配DDR存储器。瑞萨与Xilinx紧密合作,提供低风险且易于开发的电源解决方案,以加速FPGA和SoC设计。该参考设计可加快各种工业及运算类应用的电源研发速度,其中包括电机控制、机器视觉摄像头、可编程逻辑控制器(PLC)、家庭网关与家电、便携式医疗和无线设备等。 瑞萨高效PMIC参考设计提供了用户友好的交钥匙解决方案,使单个设计能够支持不同的Xilinx速度等级和DDR存储器类型,包括DDR3、DDR3

[嵌入式]

通过JTAG口对DSP外部Flash存储器的在线编程

引言

在采用TI数字信号处理器(DSP)的嵌放式硬件系统开发完成,软件也有CCS2.0集成开发环境下仿真测试通过后,怎样将编译、链接后生成的可执行文件(.Out),经过转换后的十六进制文件(.Hex)写入硬件系统的Flash存储器中,让系统脱机运行,这是许多DSP开发人员及初学者遇到并需要解决的问题。

从JTAG接口对DSP外部Flash的编程方法不只一种。本文以TMS320C6711-150 DSK板为例,介绍“在线仿真状态下”对Flash的编程。

1 Flash存储器的擦除

Flash编程之前,应对Flash进行擦除,使其每个数据位都恢复为1状态,即全FF状态。对Flash的擦除操作需要6个总线周期,总线时

[单片机]

基于MCU+FPGA的LED大屏幕控制系统的设计

引言 只要在现在的市场上走一圈就会发现,大部分的中小规模 LED显示系统,采用的是传统的单片机作为主控芯片。但是内部资源较少、运行速度较慢的单片机,很难满足LED大屏幕的显示屏,因为系统要求数据传输量大,扫描速度要快。以FPGA作为控制器,一方面,FPGA采用软件编程实现硬件功能,可以有效提高运行速度;另一方面,它的引脚资源丰富,可扩展性强。因此,用单片FPGA和简单的外围电路就可以实现大屏幕LED显示屏的控制,具有集成度高、稳定性好、设计灵活和效率高等优点。 1 系统总体结构 LED大屏幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED显示屏的行列驱动电路等模块组成,如图1所示。上位机负责汉字、字符等数

[单片机]

基于DSP的软件无线电基频发射机的设计与仿真

引言 软件无线电突破了传统的无线电台以功能单一、可扩展性差的硬件为核心的设计局限,强调以开放性最简硬件为通用平台,尽可能地使用可升级、可重配置的应用软件来实现各种无线电功能。用户在同一硬件平台上可以通过配置不同的应用软件来满足不同时间、不同环境下的不同功能需求,具有很强的灵活性和开放性。 DSP(数字信号处理器)凭着灵活性、精确性、稳定性、可重复性、体积小、功耗小、易于大规模集成,特别是可编程性和易于实现自适应处理等特点,给数字信号处理带来了巨大的发展机遇。 基于上述优点,用DSP实现基于软件无线电技术的基频发射机,不仅降低了产品的成本,减小了设备体积,满足系统的需要,而且随着DSP处理速度的不断提高,可将内插等复杂运算集成

[嵌入式]

FPGA系统的供电要求和最新DC/DC稳压器解决方案

随着FPGA制造工艺尺寸持续缩小、设计配置更加灵活,以及采用FPGA的系统的不断发展,原来只采用微处理器和ASIC的应用现在也可以用FPGA来实现了。最近FPGA供应商推出的新型可编程器件进一步缩小了FPGA和ASIC之间的性能差别。尽管这类器件的可配置性对设计工程师很有吸引力,但使用这些器件所涉及的复杂设计规则和接口协议,要求设计工程师经过全面的培训,并需要进行参考设计评估、设计仿真和验证工作。另一方面,FPGA应用中非常复杂的模拟设计,例如用于内核、I/O、存储器、时钟和其它电压轨的DC/DC稳压器,也要求新的解决方案。本文讨论的高性能DC/DC转换器有助于系统设计工程师克服这些挑战。 FPGA系统的供电要求 1.

[应用]

基于FPGA的人工神经网络实现方法的研究

引言 人工神经网络(ArtificialNeuralNetwork,ANN)是一种类似生物神经网络的信息处理结构,它的提出是为了解决一些非线性,非平稳,复杂的实际问题。目前实现ANN还主要依靠软件程序.但是依靠程序很难达到实时性的要求。 神经网络在FPGA上实现是独立于冯·诺依曼架构,利用FPGA的并行性,在一些实时性要求很强的领域应用。通用计算机虽然编程容易,但是很多时间浪费在分析指令,读出写入数据等。于是人们想利用ASIC(专用计算芯片)完成神经网络的计算任务,但是由于资源有限,这种芯片只限于实现特定的算法结构和小规模网络,而且专用芯片的制作成本很高,只适合大批量生产。 可编程逻辑器件FPGA的出现给I

[嵌入式]

Altera为三洋后视倒车摄像添图像功能

Altera公司宣布,三洋电子有限公司在其CCA-BC200汽车后视倒车摄像系统中采用了Cyclone II FPGA和Nios II嵌入式处理器。Cyclone II FPGA的Nios II嵌入式处理器为三洋公司提供了高性能图像处理解决方案,降低了广角和偏角失真。和数字信号处理器(DSP)方案相比,单芯片FPGA是更紧凑、更可靠的解决方案,而前者通常需要两个以上的器件。 CCA-BC200是业界的首款配件市场后视倒车摄像系统。该系统可以连接至所有汽车的视频监视系统,对图像进行数字校正,实现更清晰自然的图像。三洋公司在消费类电子产品展(CES)上展示了这一后视倒车摄像系统。 三洋电子有限公司汽车高级技术中心经理Hi

[嵌入式]

基于DSP和PCI总线的通信数据采集系统

摘要: 介绍一种基于DSP和PCI总线的移动通信数据采集系统。提出了一种双映射方式,成功地解决了DSP的主机通信接口(host port interface,简称HPI口)和PCI9052之间的通信连接。

关键词: 数字信号处理器 数据采集 PCI总线

随着移动通信突飞猛进的发展,移动通信的数据业务量急剧上升,监控大容量的移动数据业务成了电信运营商刻不容缓的需求。而移动通信数据的传输一般都是基于E1链路。因此从E1链路上采集通信数据成了移动数据业务监控最基础的一部分。

数字信号处理器能够高速地处理数据并具有强大的数字吞吐能力,在数据采集领域获得了广播的应用。而PCI总线也因为极高

[应用]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号