在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂算法处理上的优势,DSP+FPGA的实时信号处理系统的应用越来越广泛。ADI公司的TigerSHARC系列DSP芯片浮点处理性能优越,故基于这类。DSP的DSP+FPGA处理系统正广泛应用于复杂的信号处理领域。同时在这类实时处理系统中,FPGA与DSP芯片之间数据的实时通信至关重要。

TigerSHARC系列DSP芯片与外部进行数据通信主要有两种方式:总线方式和链路口方式。链路口方式更适合于FPGA与DSP之间的实时通信。随着实时信号处理运算量的日益增加,多DSP并行处理的方式被普遍采用,它们共享总线以互相映射存储空间,如果再与FPGA通过总线连接,势必导致FPGA与DSP的总线竞争。同时采用总线方式与FPGA通信,DSP的地址、数据线引脚很多,占用FPGA的I/O引脚资源太多。而采用链路口通信不但能有效缓解DSP总线上的压力,而且传输速度快,与FPGA之间的连线相对也少得多,故链路口方式更适合于FPGA与DSP之间进行实时数据通信。

参考文献[3]给出TS201与TS101的性能比较,但没有针对两者的链路口进行详细介绍,本文对两者的链路口进行了细致的分析和比较。文献[4]所设计的采集系统中,DSP与FGA的通信仅限于FPGA发、TS101收的单工通信;文献[5]给出了FPGA内部没计TS101链路口的框图,但只给出了简单的介绍,无法给设计者以参考。本文采用Altera公司Cyclone系列芯片EP1C12实现了与TS101/TS201两种芯片的链路口的双工通信,并给出了具体的设计实现方法。其中TS101的设计已经成功应用于某信号处理机中。

1 TS101和TS201的链路口分析与比较

TS101和TS210都是高性能的浮点处理芯片,目前两者都广泛应用于复杂的信号处理领域。TS201是继TS101之后推出的新型芯片,核时钟最高可达600MHz,其各类性能也相对优于TS101,而且TS201的链路口采用了低压差分信号LVDS技术,功耗更低、抗噪声性能更好。表1列出了两种芯片链路口性能的详细比较,其中TS101核时钟工作在250MHz,TS201核时钟工作在500MHz。

限于篇幅,TS101、TS201的链路口结构请参阅参考文献[1][2]。由于TS101收发端共用一个通道,所以只能实现半双工通信。而TS201将收发端做成两个独立通道,可实现全双工通信,理论上数据的传输速率可以提高一倍。虽然TS201的链路口收发通道独立,但实际上二者的收发机制大体相同,都是靠收发缓存和移位寄存器收发数据。然而FPGA内部的链路口设计不必拘泥于此,只要符合链路口通信协议并达成通信即可。

2 FPGA与DSP的链路口通信

2.1 链路口通信协议分析

TS101的链路口共有11根引脚,通过8根数据线(LxDAT[7..0],这里x可以是0、1、2或3,代表TS101或TS201的0号~3号链路口中的一个,以下同)进行数据传输,并采用3根控制线(LxCLKOUT、LxCLKIN、LxDIR)来控制数据传输时钟、通信的握于和数据传输方向。其中LxDIR为通知链路口当前工作状态是接收或发送的输出引脚,可悬空不用。TS201的链路口共24根引脚,接收和发送各12根引脚,通过LVDS形式的数据线(LxDAT_P/N[3..0])和时钟线(LxCLK_P/N)进行数据传输,并采用LxACK和LxBCMP#(‘#’代表信号低有效)来通知接收准备好和数据块传输结束。

采用FPGA与DSP通过链路口通信的关键是令双方通信的握手信号达成协议,促使数据传输的进行。实际上,如果考虑TS201的LVDS信号形式已经被转换完毕,则TS101和TS201链路口传输的数据形式是一样的,都是时钟双沿触发的DDR数据,并且每次传输的数据个数都是4个长字(即128bit)的整数倍。鉴于以上两种芯片链路口数据的共同点,所以采用FPGA与两类芯片通信时,接收和发送的数据缓存部分的设计应该是很相近的,只是通信握手信号部分的设计应当分别加以考虑。下面分别给予介绍。

2.2 基于FPGA的TS101链路口设计

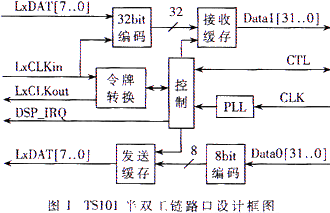

图1给出了FPCA与TS101进行半双工链路口通信的设计(对LxCLKOUT、LxCLKIN均以FPCA的角度来叙述),该接口由接收、控制和发送三部分组成。本设计FPGA时钟为40MHz,TS101核时钟上作在250MHz,链路口时钟设定为DSP核时钟的8分频,FPGA与DSP的实际数据传输率为62.5MBps。

(1) 接收部分:由编码和缓存两部分组成。由于链路口的数错是DDR形式的,不方便数据的缓存,本文采用QuartusII Megafunctions中的altddio模块将上升沿数据和下降沿数据分开。注意这个模块的下降沿数据输出会滞后上升沿数据1个时钟周期,输出时应该用链路口时钟信号(LxCLKIN)通过D触发器来将数据对齐。该模块的inclock一定要用链路口时钟信号以保证数据的正确读取,如图2所示。又由于DSP内部数据是32位的长字,所以写入接收缓存前应该用一组D触发器将数据进行32bit对齐,这里注意DSP链路口先传输32位数据中的低8位。

(2) 控制部分:由令牌转换模块和控制模块组成,是整个设计的核心部分,完成对各部分的控制和与FPGA内部进行通信(通过CTL一组信号)。TS101的链路口通信握手是靠两根时钟信号验证令牌指令完成,即当发送端驱动原本为高的LxCLKOUT信号为低电平,以此作为令牌请求向接收端发出。如果接收端准备好接收,则接收端驱动LxCLKIN为高;如果令牌发出6个时钟周期后,LxCLKIN信号仍然为高,则肩动数据传输(以上时钟信号都以发送端视角分析)。本设计中,令牌转换模块负责验证令牌和发送令牌。这里要注意,由于用来验证令牌低电平个数的时钟信号(PLL_32ns)是由FPGA时钟信号(CLK)通过锁相环倍频得到,与DSP链路口时钟异步,故验证令牌时,当计数器计到5个低电平时即可认为已达成通信握手,否则可能会丢失数据。达成握手后通知控制模块向接收或发送缓存输出控制信号,其中接收控制信号包括写缓存时钟和写使能。发送控制信号包括读缓存时钟、读使能和DSP中断信号(DSP_IRQ),其中写缓存时钟通过对链路口时钟分频得到,读缓存时钟由锁相环倍频FPGA工作时钟得到。

(3) 发送部分:与接收部分类似,也南编码和缓存两部分组成,相应的设计基本相同,这里不作过多介绍。由于DSP链路口每次传输数据个数的最小单位是4个32位字,即8个链路时钟周期,所以发送时钟廊该每8个时钟周期一组,以凑够128bit,避免传输错误,其中多余无效的数据DSP可以自行舍去。发送部分采用DSP外部中断方式而不是链路口中断方式通知DSP接收数据。

TS101的链路口通信协议要求链路口接收端在传输启动一个周期后,将其LxCLKOUT拉低,若可以继续接收,在下一个周期再将其拉高,以此作为连接测试。实际运行中发现,当FPGA接收数据时,可将LxCLKOUT信号一直驱动为高,不必做特殊的连接测试也能正确接收数据。另外,发送链路口数据时,由于发送缓存中已经对应仔好了要发送的8bit数据,故可以使用对FPGA时钟信号(CLK)倍频得到的PLL_16ns信号来读发送缓存,读出的数据即链路口发送数据,再对PLL_16ns信号的下降沿分频得到链路口的发送时钟信号。

限于篇幅,本文只给出FPCA接收TS101数据的时序图,如图3所示。LxCLKIN、LxDAT[7..0]是DSP的链路口输出时钟和数据,LxCLKOUT是FPGA的回馈准备好信号。仿真中链路口数据采用1F~3E(十六进制)的32个8bit数据,即从2221201F到3E3D3C3B的8个32bit数据;PLL_32ns信号是FPGA内部锁相环产生的与DSP链路口时钟异步的32ns时钟信号,用来校验令牌指令;W_FIFO_EN信号足写缓存使能信号,当令牌验证后使能接收缓存;DSP_DAT信号是DSP通过链路门传输的32bit数据,通过对链路口数据的编码得到;W_BUF_CLK信号由链路口时钟分频处理得到,将上升沿对应的32bit DSP数据写入接收缓存,完成接收过程。

2.3 基于FPGA的TS201链路口设计

图4给出了FPGA与TS201进行链路口通信的设计框图。由于TS201的握手信号较多,所以相对TS101的链路口设计容易些。本设计FPGA时钟50MHz,TS101核时钟500MHz,链路口时钟为DSP核时钟的4分频,采用4bit方式,单向实际数据传输速率为125MBps。

TS201的链路口数据和时钟采LVDS信号,具有速率高、功耗低、噪声小的优点。Cyclone系列芯片不仅支持LVDS信号,还集成了LVDS转换模块,这给设计提供了很大方便。应该注意的是,在硬件设计时LVDS信号两极的PCB走线要匹配,并且注意匹配电阻网络的接入。具体请参考文献[6]-9 Implementing LVDS in Cyclone De-vices。

TS201的链路口有1bit和4bit两种传输方式,本文以4bit为例进行设计。图4给出的信号都是经LVDS转换后的信号。由于TS201的收发做成了两个单独的通道,FPGA的设计也应该相应地设计为两个通道,真正做到全双工通信,收发互不影响。接收与发送部分与TS101的设计基本相同,发送部分也采用外部中断方式通知DSP接收链路口数据。TS201的通信握手信号有ACK和BCMP#信号。其中ACK信号用来通知接收准备好,在实时信号处理中,一般不允许数据传输的等待,故将这个信号置为准备好。BCMP#信号用于通知数据块传输的结束,当能确定DMA传输数据个数时,可以将此引脚悬空。

TS201链路口的收发机制非常相似,本文仅给出发送数据时序图,如图5所示。L1_IRQ是FPGA发给DSP的外部中断,用来通知DSP收数据;L1_ACKI是DSP的接收准备好信号;R_BUF_EN是读发送缓存使能信号;链路口时钟L1_CLKOUT是以读缓存时钟R_CLK下降沿的二次分频,对应从缓存中读出的4bit链路口数据L1_DA-To。注意这里读缓存及时钟分频时会有纳秒级的延迟。

3 DSP的相应设置

TS101和TS201的链路口都配置了控制寄存器(LCTLX)和状态奇存器(LSTATx)两组寄存器。LCTLx用来控制链路口的传输,LSTATx用来通知链路口的工作状态。TS101链路口时钟频率可以是核时钟的8、4、3或2分频,通过设置LCTLx中的SPD位米完成,本文设计将SPD位置000,即为核时钟8分频。由于TS201的接收发送通道独立,所以其控制寄存器分为接收控制寄存器(LRCTLx)和发送控制寄存器(LTCTLx)。TS101链路口发送时钟频率可以与核时钟相同或为其4、2、1.5分频,通过设置LTCTLx中SPD位来完成。本文设计将SPD位置100,即为核时钟4分频,并将LRCTLx/LTCTLx中(接TDSIZE位置1,设置成4bit传输方式。如果BCMP#信号悬空,注意一定要将LRCTLx巾RBCMPE位置0。

有两种方法启动DSP的链路口DMA传输:利用链路中断和利用DSP的四个外部中断(IRQ0~IRQ3)。两种中断方式都需要在中断服务程序中对DMA的TCB寄存器进行配置来启动链路口的接收DMA通道。鉴于外部中断的优先级高于链路口中断,可以避免数据丢失,本文设计的通信方式均以外部中断方式通知DSP接收数据。在DMA的TCB寄存器配置过程中,为了保证程序不被其他中断打断,可以在中断服务程序开始时就把所有其他中断屏蔽掉,存中断服务程序返回之前再把屏蔽掉的中断位还原。

本文对TigerSHARC系列的两种典型DSP芯片的链路口进行了分析和比较,并给出了FPGA与这两种DSP芯片进行链路口通倍的具体方法。在FPGA内部实现了DSP链路口的设计,同时给出了DSP进行链路口通信的具体设置方法。由于实时处理中数据的重发会严重影响处理的实时性,故本文的链路口通信设计没有对所传输的数据进行校验。本文给出的基于FPGA路口设计具有很强的通用性,可以应用于基于TS101/TS201的多种应用系统中,提高系统内部的通信能力;也可用于板间DSP的数据传输,提高系统外部的通信能力。

上一篇:FPGA与DSP的高速通信接口设计与实现

下一篇:FPGA与DSP的高速通信接口设计与实现

推荐阅读最新更新时间:2024-05-02 20:35

- 下载有礼:2017年泰克亚太专家大讲堂第二期: 100G/200G/400G通讯标准发展趋势及解决方案

- 【投票跟帖有礼】原厂的翻新仪器怼市场上的二手仪器,你顶谁?

- 有奖直播:全方位详解TI MSP Academy 教程

- 西门子精彩视频限时免费|利用电子产品生命周期管理 (PLM) 更快地交付更多产品

- TI 技术大咖带你领略独一无二的MCU世界 推荐、抢楼全有礼!

- 免费测评——拓普微智能显示模块

- 安全的革新,全新的验证方式 下载富士通 《频谱验证解决方案 》白皮书 好礼送!

- 征集|无线充电套件已经准备好,你打算用它做什么?

- PI有奖问答第二期 看视频 读资料 答题赢好礼

- Mouser 新用户大礼包再次来袭:晒单5折返E金币!

通信基础以及汽车总线技术概述

通信基础以及汽车总线技术概述 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号