受诸如视频和静态图像使用的增多以及软件无线电等可重复配置系统需求的增长,数字信号处理(DSP)的应用继续膨胀。其中许多应用把重要的DSP处理要求和对成本的敏感性、对高性能的需求以及低成本的DSP解决方案结合在一起。

通用的DSP芯片和FPGA是实现DSP功能的两种普遍的方法。每种方法都各有优点,其最适宜的方法因应用要求的不同而各异。本文论述了通用DSP的功能,阐述了通用DSP和FPGA之间的差异,比较了现有的用FPGA实现DSP的解决方案,最后介绍了LatticeECP2M DSP的结构以及实现DSP的设计方法。

通用的DSP解决方案与FPGA实现方法的对比

带有加法、减法或累加运算的乘法器是大多数DSP应用的核心。通用DSP芯片把这些功能的有效实现方法和一个通用微处理器结合在一起。乘法器的数目一般为数个,微处理器将数据串行地实现乘法或其它功能,中间结果存放在存储器或累加器中。性能的提高主要通过提升用于乘法的时钟速度来实现。典型的时钟速度从数十MHz到1GHz。其性能,用每秒百万次乘法累加(MMAC)来衡量,通常为10到4000。更高性能要求的功能不得不分拆在多个DSP引擎中实现。这些芯片的价格从低端性能的几美元到高端性能的数百美元。这种方法的优点是能够直接实现用诸如C这样的高级编程语言编写算法。

面向DSP的FPGA能在一个芯片上并行地实现许多功能。通用的布线、逻辑和存储器资源用来实现各个功能之间的互连、实现额外的功能、定序或在必要的情况下存储数据。一些基本的器件仅提供乘法器,需要用户用逻辑构造所有其它的功能。更多的高级器件提供加法、减法和累加功能,作为一整套DSP构造模块的一部分。FPGA通常拥有数十个乘法单元,可以在数百MHz的时钟速度下工作。例如,LatticeECP2-70 FPGA拥有88个18x18的乘法器,运行速度可达325MHz,性能达到每秒28600MMAC。

设计者经常要实现结构化的DSP功能,这在FPGA内要占用大量的计算资源。通常在FPGA内实现的结构化功能为:有限脉冲响应滤波器(FIR)、无限脉冲响应滤波器(IIR)、快速傅立叶变换(FFT)和混频器。每种功能都需要将乘法单元与加法、减法和累加结合在一起。图1和图2分别是典型的FIR滤波器和快速傅立叶变换(FFT)的实现方式。

目前在低成本FPGA中实现DSP功能有几种方法。第一种方法是使用器件内的查找表(LUT)。这个方法提供相对低的性能而且占用许多FPGA资源。另外一种方法是在FPGA中用硬核实现乘法器。这减少了实现DSP所需的FPGA资源。然而正如前面所述,在FPGA中实现的大多数DSP功能需要在 乘法器之后进行加、减和累加。这些功能要占用大量的FPGA资源,最后的数据宽度可达36位。因此经常会在设计中形成瓶颈。为了面对这个挑战,最新的FPGA利用有效的硬逻辑在乘法器之后进行可编程加、减和累加。用这种方法实现DSP功能后,大大减少了通用资源的使用,并能获得很高的性能。

LatticeECP2/M器件结构

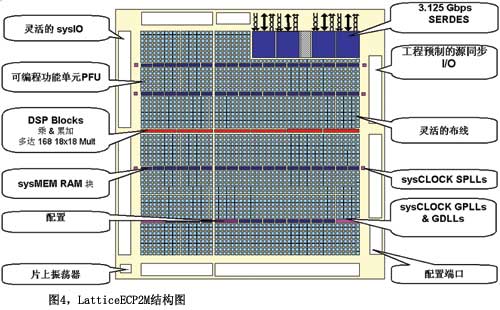

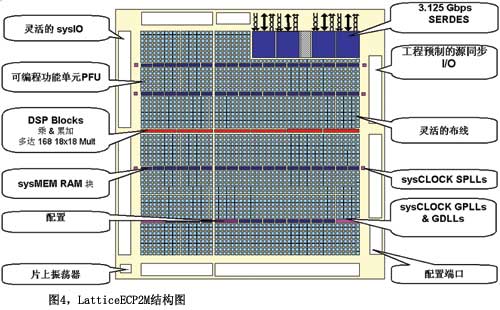

LatticeECP2和LatticeECP2M系列重新定义了低成本FPGA,在更低的成本下拥有更多最佳的FPGA特性。器件含有sysDSP块和工程预制的源同步I/O。在LatticeECP2M中有高达5.3M位的RAM块、在LatticeECP2中有高达1.1M位的RAM块。在LatticeECP2M中有3.125Gbps嵌入式SERDES,支持PCIexpress、Ethernet (1GbE 和 SGMII)以及多个其它标准。集成了以前只有高成本、高性能FPGA才有的特点和性能,这些系列的产品极大地扩展了利用低成本FPGA的应用范围。

LatticeECP2/M器件由一个低成本的FPGA结构加上3个~42个sysDSP块构成(图3为sysDSP块)。图4是ECP器件的整体结构图。图中红色部分是sysDSP块,专门用来实现DSP的功能。LatticeECP2/M系列中的sysDSP块支持三种数据宽度下(9、18和36)的四种功能单元。用户为一个DSP块选择一种功能单元,然后选择数据宽度和操作数的类型(带符号/无符号)。sysDSP块中的操作数可以是带符号或者无符号的,但在一个功能单元中不可以混合使用。类似的,操作数的宽度在一个块中必须相同。每个sysDSP块中的资源可以经过配置支持下面四种单元:

● MULT(乘法)

● MAC(乘法、累加)

● MULTADD(乘法、加/减)

● MULTADDSUM(乘法、加/减,累加)

每个块中可用的单元数目取决于数据宽度。该宽度有三种数值可供选择:x9,x18和x36。数个这样的单元可以连接起来,从而以并行方式实现DSP功能。

DSP设计方法

Lattice提供便捷的方法让设计者处理sysDSP块的这些性能,下面分别叙述这些方法:

●ispLEVER工具中的Module/IP Manager是一个图形接口,可以迅速地产生实现DSP单元的模块。这些模块可以在HDL设计中被适当地采用。

●将特定的功能通过编代码嵌入设计的HDL中,允许综合工具推理出DSP块的用法。

●采用一个Lattice Block套件在MathWork的 Simulink中实现设计。然后,ispLEVER软件中的ispLeverDSP可以适当地将这些模块转换成HDL。

●直接在源代码中用实例说明DSP组件。

任何设计方法选择取决于DSP运算规则的设计方法以及物理实现时所要求的控制程度。图5展示了在MathWork的Simulink工具中使用Lattice Block套件的情形。

结语

DSP技术的应用将进一步发展。对DSP应用中典型功能的分析表明:乘法器、加法、减法和累加单元的组合是必需的。LatticeECP2/M器件把DSP块和低成本的FPGA结构组合在一起。通过在sysDSP块内实现加法、减法、和累加功能,有很高的性能和LUT的利用率。

引用地址:

经过优化的低成本FPGA中的高性能DSP功能

推荐阅读最新更新时间:2024-05-02 20:38

具有TTL逻辑电平输出的压控振荡器

具有TTL逻辑电平输出的压控振荡器

[模拟电子]

Based逻辑分析仪的应用特点、优势及使用方法

工程师在测量数字讯号时使用逻辑分析仪能够快速的找出问题所在,而孕龙逻辑分析仪更提供了多项专利技术使工程师开发产品时可提升工作效率。孕龙科技逻辑分析仪除了强大的数字讯号分析功能外,人性化的操作接口也能够减轻操作上的负担,完整的在线使用说明可帮助使用者快速熟悉操作环境。 当工程师使用PC完成待测电路的仿真后,便可以直接透过孕龙逻辑分析仪进行待测电路的波形测量,而且孕龙科技逻辑分析仪支持的特殊总线约有四十种,如车用电子中的Can bus、Lin bus、Flex ray,数字音讯中的I2S、S/PDIF、PCM、ST,内存接口中的SPI、I2C、1-Wire,IC接口中的SSI、JTAG、Micro wire,PC系统中的USB1.

[测试测量]

浅谈家庭影院中视频线与音箱线的布线要点

在家庭影院布线(一)中说到只有视频线,音箱线装修时需要考虑,音频线(因为音源设备与功放可以放在同一位置,所以音频线很短)不需要考虑。下面讨论一下视频线与音箱线的布线。 一、视频线布线 如果你仅用电视或者等离子,液晶电视作为显示设备,视频线也不是太需要考虑。但家用投影机具有大画面,临场感强等其他显示设备说不具有的优势,未来肯定有大发展,我们装修不能仅仅为眼前考虑,装修一次至少也要保十年用途吧,十年之内估计也就两三年内家用投影机肯定进入很多家庭。 视频线一端连接DVD播放机或者HTPC, 另一端连接投影机。 DVD机的位置一般是固定的,一般在视听室前部正中间,投影机位置有三处: 1 将投影机吊在视听室后部天花板上, 使用专有的投影

[嵌入式]

石墨烯存储单元将是可弯曲手机最好选择

随着每一次推出新旗舰,我们看到智能手机厂商带来更大的显示屏,更先进的生物识别安全功能,增强的相机功能或AR/VR功能。但是,智能手机市场的下一个大事肯定是可弯曲的智能手机。外界相信三星已经开始研发这样的智能手机,而像LG甚至OPPO这样的公司正在探索灵活的显示屏,这样可以使设备体积缩小一半。三星将有可能在2019年推出折叠式智能手机,因为有些技术问题仍然需要解决。下面就随手机便携小编一起来了解一下相关内容吧。 据报道,三星Galaxy X将折叠一半,并具有灵活的OLED显示屏,但埃克塞特大学的科学家们已经创造出了一种新的材料,为智能手机制造商提供了更多的灵活性,包括在设计方面。为了实现真正灵活的智能手机,内部组件也将具有

[手机便携]

拆一个DSLogic逻辑分析仪基础版

前些天发了一个拆某电SSD维权的文章,眼看获赞就要上千了,也有很多人关注我。所以今个拆一个DSLogic逻辑分析仪,虽然这货和之前的SSD没有半毛钱的关系,主要是要让某电知道,这特么才叫良心! 最近在搞CC2530,看到别人用逻辑分析仪是真的爽,简直搞电子必备!于是也想整一个。然后就看到了这个开源的DSLogic。在国外官网Plus版卖这个数: 在国内才卖499RMB,这才叫良心,某电你懂么? 我买不起Plus版,只搞了个基础版。不废话了,上图: 送的线不错,镀银的,硬硬的很实在,就是夹子不怎么好,没有我在某宝上买的一块钱一只的那种: 16通道接口: Type-c接口,USB2.0速率: CN

[测试测量]

可编程逻辑器件在高准确度A/D转换器中的应用

1 引 言 可编程逻辑器件(PLD)是当今国际上流行的新一代数字系统逻辑器件。它主要是一种“与-或”两级式结构器件,除了具有高速度、高集成度性能之外,其最大的特点就是用户可定义其逻辑功能。因此PLD能够适应各种需求,大大简化系统设计,缩小系统规模,提高系统可靠性,受到广大工程技术人员的青睐。 可编程逻辑器件种类繁多,性能各异,主要有以下几种基本类型:可编程只读存储器(PROM),现场可编程逻辑阵列(FPLA),编程阵列逻辑(PAL),通用阵列逻辑(GAL)。通用阵列逻辑GAL(Generic ArrayLogic)是新一代的可编程逻辑器件,是采用先进的E2CMOS工艺制造的大规模集成电路,是新产品设计的理想器件

[应用]

商刊:iPod或将全线放弃硬盘转用闪存

北京时间10月10日《商业周刊》文章指出,随着闪存芯片价格的迅速降低,苹果公司很可能会将其所有音乐播放器中的硬盘换成闪存。 当苹果公司的第一款iPod应用播放器在六年前面世时,它便由于种种原因而成为稀世之作,但是最主要的原因是它采用了一个硬盘。虽然MP3播放器市场仍处于初生阶段,但是大部分用户仍然更信赖将歌曲保存在闪存芯片上而不是硬盘上。 当然,苹果公司随后就改变了音乐播放器业务以及音乐市场本身。IPod模式大获成功之后得到不断地复制,逐渐发展成如今的五个系列,它们是shuffle、nano、经典型、触屏型和iPhone。 但是现在有迹象表明基于硬盘的iPod或许会逐渐退出市场的舞台了。至少从市场调查公司iSuppli最近发

[焦点新闻]

牛津半导体推出USB/Firewire双SATA存储控制器

牛津半导体公司(Oxford Semiconductor)近日发布了具有加密功能的可配置USB/Firewire双SATA存储控制器OXUF924DSE。该产品能够帮助外部存储制造商向用户提供稳定性极高的数据保密存储。该款控制器通过整合硬件实现来加密,因此能够使数据吞吐速度保持在80Mbytes/秒这样较高的水平上。 OXUF924DSE控制器可连通双SATA磁盘和USB2.0接口以及Firewire400和Firewire800端口,而且可向高级加密标准(Advanced Encryption Standard)提供实时的128位加密。由于能够支持安全令牌(secure token)、软件密码和生物识别(指纹技术)传感器等加密

[新品]

汽车构造I(9)-119页

汽车构造I(9)-119页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号