通用的DSP芯片和FPGA是实现DSP功能的两种普遍的方法。每种方法都各有优点,其最适宜的方法因应用要求的不同而各异。本文论述了通用DSP的功能,阐述了通用DSP和FPGA之间的差异,比较了现有的用FPGA实现DSP的解决方案,最后介绍了LatticeECP2M DSP的结构以及实现DSP的设计方法。

通用的DSP解决方案与FPGA实现方法的对比

带有加法、减法或累加运算的乘法器是大多数DSP应用的核心。通用DSP芯片把这些功能的有效实现方法和一个通用微处理器结合在一起。乘法器的数目一般为数个,微处理器将数据串行地实现乘法或其它功能,中间结果存放在存储器或累加器中。性能的提高主要通过提升用于乘法的时钟速度来实现。典型的时钟速度从数十MHz到1GHz。其性能,用每秒百万次乘法累加(MMAC)来衡量,通常为10到4000。更高性能要求的功能不得不分拆在多个DSP引擎中实现。这些芯片的价格从低端性能的几美元到高端性能的数百美元。这种方法的优点是能够直接实现用诸如C这样的高级编程语言编写算法。

面向DSP的FPGA能在一个芯片上并行地实现许多功能。通用的布线、逻辑和存储器资源用来实现各个功能之间的互连、实现额外的功能、定序或在必要的情况下存储数据。一些基本的器件仅提供乘法器,需要用户用逻辑构造所有其它的功能。更多的高级器件提供加法、减法和累加功能,作为一整套DSP构造模块的一部分。FPGA通常拥有数十个乘法单元,可以在数百MHz的时钟速度下工作。例如,LatticeECP2-70 FPGA拥有88个18x18的乘法器,运行速度可达325MHz,性能达到每秒28600MMAC。

设计者经常要实现结构化的DSP功能,这在FPGA内要占用大量的计算资源。通常在FPGA内实现的结构化功能为:有限脉冲响应滤波器(FIR)、无限脉冲响应滤波器(IIR)、快速傅立叶变换(FFT)和混频器。每种功能都需要将乘法单元与加法、减法和累加结合在一起。图1和图2分别是典型的FIR滤波器和快速傅立叶变换(FFT)的实现方式。

目前在低成本FPGA中实现DSP功能有几种方法。第一种方法是使用器件内的查找表(LUT)。这个方法提供相对低的性能而且占用许多FPGA资源。另外一种方法是在FPGA中用硬核实现乘法器。这减少了实现DSP所需的FPGA资源。然而正如前面所述,在FPGA中实现的大多数DSP功能需要在 乘法器之后进行加、减和累加。这些功能要占用大量的FPGA资源,最后的数据宽度可达36位。因此经常会在设计中形成瓶颈。为了面对这个挑战,最新的FPGA利用有效的硬逻辑在乘法器之后进行可编程加、减和累加。用这种方法实现DSP功能后,大大减少了通用资源的使用,并能获得很高的性能。

LatticeECP2/M器件结构

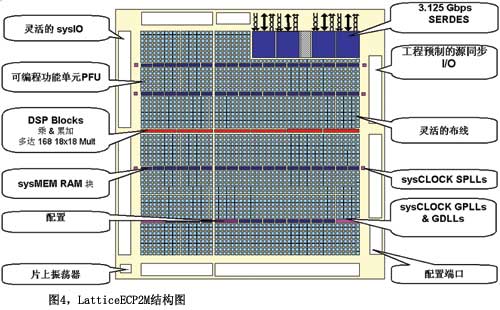

LatticeECP2和LatticeECP2M系列重新定义了低成本FPGA,在更低的成本下拥有更多最佳的FPGA特性。器件含有sysDSP块和工程预制的源同步I/O。在LatticeECP2M中有高达5.3M位的RAM块、在LatticeECP2中有高达1.1M位的RAM块。在LatticeECP2M中有3.125Gbps嵌入式SERDES,支持PCIexpress、Ethernet (1GbE 和 SGMII)以及多个其它标准。集成了以前只有高成本、高性能FPGA才有的特点和性能,这些系列的产品极大地扩展了利用低成本FPGA的应用范围。

LatticeECP2/M器件由一个低成本的FPGA结构加上3个~42个sysDSP块构成(图3为sysDSP块)。图4是ECP器件的整体结构图。图中红色部分是sysDSP块,专门用来实现DSP的功能。LatticeECP2/M系列中的sysDSP块支持三种数据宽度下(9、18和36)的四种功能单元。用户为一个DSP块选择一种功能单元,然后选择数据宽度和操作数的类型(带符号/无符号)。sysDSP块中的操作数可以是带符号或者无符号的,但在一个功能单元中不可以混合使用。类似的,操作数的宽度在一个块中必须相同。每个sysDSP块中的资源可以经过配置支持下面四种单元:

● MULT(乘法)

● MAC(乘法、累加)

● MULTADD(乘法、加/减)

● MULTADDSUM(乘法、加/减,累加)

每个块中可用的单元数目取决于数据宽度。该宽度有三种数值可供选择:x9,x18和x36。数个这样的单元可以连接起来,从而以并行方式实现DSP功能。

DSP设计方法

Lattice提供便捷的方法让设计者处理sysDSP块的这些性能,下面分别叙述这些方法:

●ispLEVER工具中的Module/IP Manager是一个图形接口,可以迅速地产生实现DSP单元的模块。这些模块可以在HDL设计中被适当地采用。

●将特定的功能通过编代码嵌入设计的HDL中,允许综合工具推理出DSP块的用法。

●采用一个Lattice Block套件在MathWork的 Simulink中实现设计。然后,ispLEVER软件中的ispLeverDSP可以适当地将这些模块转换成HDL。

●直接在源代码中用实例说明DSP组件。

任何设计方法选择取决于DSP运算规则的设计方法以及物理实现时所要求的控制程度。图5展示了在MathWork的Simulink工具中使用Lattice Block套件的情形。

结语

DSP技术的应用将进一步发展。对DSP应用中典型功能的分析表明:乘法器、加法、减法和累加单元的组合是必需的。LatticeECP2/M器件把DSP块和低成本的FPGA结构组合在一起。通过在sysDSP块内实现加法、减法、和累加功能,有很高的性能和LUT的利用率。

上一篇:经过优化的低成本FPGA中的高性能DSP功能

下一篇:装入CPLD/FPGA的步进电机运动控制器与驱动器

推荐阅读最新更新时间:2024-05-02 20:38

- Vishay 推出新款精密薄膜MELF电阻,可减少系统元器件数量,节省空间,简化设计并降低成本

- 芯原推出新一代高性能Vitality架构GPU IP系列 支持DirectX 12和先进的计算能力

- NXP 2.5亿美元收购Aviva,但车载SerDes领域依然处于战国时期

- 应对 AI 时代的云工作负载,开发者正加速向 Arm 架构迁移

- 沉浸式体验漫威宇宙,英特尔锐炫显卡为《漫威争锋》提供Day 0支持

- 艾迈斯欧司朗与法雷奥携手革新车辆内饰,打造动态舱内环境

- 《嵌入式-STM32开发指南》第二部分 基础篇 - 第7章DMA(HAL库)

- 【“源”察秋毫系列】DC-DC电源效率测试,确保高效能与可靠性的关键步骤

- NVIDIA 推出高性价比的生成式 AI 超级计算机

- Mapbox与Arm合作推出虚拟主机 加速软件定义汽车导航

- 答题赢好礼|世健探索:水质检测为人类的安全保驾护航

- 直击富士通在线展会,答题赢好礼

- 听技术大咖侃谈Type-C 测量那些事儿—— 即刻获取能量,轻松闯关赢礼品!

- 是德科技——从容应对医疗电子设备设计和测试的挑战! 答题有好礼

- 直播已结束|如何通过【TI MSPM0 固件示例】及【常用电机驱动器方案和拓扑】,在10分钟内旋转电机

- Wi-Fi智能战队征集令,Open1081免费试用进行中...

- 索取海报:泰克矢量网络分析仪基础知识

- 最后一周:免费获取Pasternack《RF产品选型指南》2018 印刷版!

- 免费试用Atmel MCU开发板,抢“鲜”体验优越性能,更有大奖等你拿!

- 瓜分2000元新年开工红包!贸泽电子邀你元宵猜灯谜

汽车构造I(9)-119页

汽车构造I(9)-119页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号