1 引 言

有限长冲激响应(FIR)滤波器在数字信号处理中是一种基本的处理单元。无限长单位冲激响应(IIR)数字滤波器的优点是可以利用模拟滤波器设计的结果,但其缺点是不具有线性相位性。图像处理以及数据传输都要求信道具有线性相位特性,FIR滤波器可以做成严格的线性相位,避免被处理信号产生相位失真,还可以具有任意的幅度特性。此外,FIR滤波器的单位冲激响应是有限长的,因而滤波器一定是稳定的。

在数字滤波器的研究中,已经提出多种FIR滤波器的设计和实现方法,如并行结构、流水线结构、分布式结构等[1-3]。FIR滤波器计算量大,且要求实时实现。如何提高速度以满足信号处理的高效性和实时性一直是人们研究的重点和热点。脉动阵列是一种新型的流水线结构,所有处理单元是相同且全流水的,并且有模块化和规则化的特征,这对于硬件设计是很重要的。脉动阵列结构可以很好地满足高速实时信号处理的需要,提高数据的通过率及电路的执行速度。该结构结合了并行结构和流水线的优势,使FIR滤波器达到了更高的处理速度。

数字滤波器现在大多在DSP芯片上实现[4]。随着集成电路技术的发展,现在已有多种专用DSP芯片用于实现滤波、FFT等运算。另外,FPGA内部的规整的逻辑块阵列,很适合实现脉动阵列这种高度并行的运算。Altera公司新推出的Stratix系列FPGA内部有丰富的逻辑阵列资源及高性能嵌入式DSP块,能够高效地实现数字信号处理功能[5]。

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR滤波器在FPGA上获得了很好的性能,比串行结构的运算速度更快,呵以更好地满足数字信号处理中高效、实时的要求。

2 FIR滤波器及脉动阵列原理

2.1 FIR滤波器原理

数字滤波器用于改变输入信号X(n)的频谱特性以满足某种特定的设计要求。一个因果的数字滤波器可以用它的单位冲激响应h(n)、传输函数H(z)或者差分方程来表达。其中单位冲激响应和传输函数描述了系统的时域和频域性质,差分方程则反映了实现该滤波器所需的运算。

一个线性时不变因果滤波器可以用式(1)的差分方程描述:![]()

如果1≤k≤N时,ak=0,则:

这就是一个M阶的FIR滤波器,是非递归运算。

2.2 脉动阵列

脉动阵列结构是1978年由Carneige-Mellon大学的H.T.Kung等人发展起来的一种专用处理器设计模型,是一种新的流水线结构,表示一种有节奏地汁算并通过系统传输数据的处理单元网络。这些处理单元规则地泵入泵出数据以维持规则的数据流[6]。由于其数据运算与传送方式类似于心脏或脉搏有节奏地跳动,因此被称为心动阵列或脉动阵列。利用脉动阵列可设计出一系列适合数字信号处理应用的模块化、规则且有效的运算结构。脉动阵列结构的基本特性如下:

(1)脉动性

数据在一个全局时钟的精确控制下,有节奏地经过计算和传递过程,最后通过网络。

(2)模块性和规则性

阵列由模块化的处理单元组成,各处理单元之间的互连方式均匀一致,并且计算网络可任意扩大。

(3)空间局部性和时间局部性

表现在数据从一个计算节点传递到下一个计算节点至少需要一个单元时间。

(4)有效的流水线结构

脉动阵列免除了形成数据流所需的控制开销。阵列内处理单元间的局部连接方式使阵列中负载均匀、连线极短,最大限度地减小了系统内部的通信延时,提高了处理单元的利用率,使整个阵列的系统性能得到充分发挥。

脉动结构是将线性映射技术用于规则依赖图上进行设计的。依赖图的边表示优先约束。脉动阵列设计中的基本矢量有:

(1)投影矢量:![]()

(2)处理器矢量:PT=(p1 p2)

(3)调度矢量:ST=(S1 S2)

(4)硬件利用率:HUE=1/│STd │

3 FlR滤波器的脉动结构设计

3.1 FIR滤波器的脉动阵列结构

用调度不等式选择可行的调度矢量ST,并根据脉动结构的可行性限制条件选择投影矢量d和处理器空间矢量PT,然后用线性映射技术设计脉动列。

选择投影矢量、处理器矢量和调度矢量如下:![]()

于是,节点IT=(i,j)被处理为:

节点IT=(i,j)的执行时间为:

硬件利用率:

以五阶FIR滤波器为例:

FIR滤波器的脉动结构设计框图如图1所示。

其中,d0,d1,d2和d3作为延时单元,m0,m1,…,m4为固定乘数的乘法器,乘数分别为ω0,ω1,…,ω4。乘法器m0和加法器a0构成处理器P0;乘法器m1和加法器a1构成处理器P1;类似的,m4和a4构成处理器P4。5个处理器同时工作,x(n)输入后同时到达5个处理器,分别和权重ωi相乘后,经不同的延时相加得到结果y(n)。

该设计框图很好地体现了2.2节提到的脉动阵列的4个基本特性。数据在网络中有节奏的输入、计算、传递并输出。该结构由5个相同的模块化处理器构成,容易扩展,可实现任意阶的FIR滤波器。数据的输入、和权重的相乘、中间结果的寄存、数据的输出各需要一个单元时问,但这几种操作可同时进行,不会互相干扰。该脉动阵列结构以高度的流水线方式运行。

需要注意的是,在乘法器输出的时候需要对输出的数据进行一位扩展,以避免加法器的溢出问题。

3.2 时序分析

该结构的空问时间表示如图2所示。横轴为时间轴,纵轴为处理器轴。图中的每一行对应一个处理器。可以看到在时间轴的某一点上,输入数据x(n)在同一时间剑达所有处理器,即输入"广播";在处理器轴的某一点上,权重ωi在各处理器中处于相同的空间坐标,因此权重"保持";而输出数据y(n)在不同的空间和时间得到,所以输出"移动"。该FIR滤波器为输入广播、权重保持、输出移动型的脉动阵列结构。

借助于脉动阵列技术,输入和输出之间的处理可以同时进行,因此,总的执行时间变得最小。对该结构进行时序分析,如图3所示。在第一个时钟周期x(0)送到各处理器,和权重分别相乘后在第二个时钟周期得到y(0)=ω0x(0),在此同时数据x(1)已经输入;第三个时钟周期输入x(2),在处理器P0得到ω0x(1),此时处理器P1的结果ω1x(0)经一级延时后和P0的结果相加得到y(1)=ω0(1)+ω1x(O)。同理,第四个周期得到y(2)=ω0x(2)+ω1x(1)+ω2x(0),第五个周期得到y(3)=ω0x(3)+ω1x(2)+ω2x(1)+ω3x(O)…。

4 FPGA验证

以一个输入输出均为8 b的五阶FIR滤波器为例,对该脉动阵列结构的FIR滤波器在FPGA上进行验证。目标器件选用Stratix系列器件,编译软件为QuartusⅡ4.2。

Stratix系列器件是Altera公司推出的新型FPGA,其内部有丰富的嵌入式存储器、优化的数字信号处理(DSP)块和高性能I/O能力。Stratix器件是设计复杂的高性能系统的理想选择。StratiX器件使用DSP块实现大计算量应用所需的大数据吞吐量。DSP块由硬件乘法器、加法器、减法器、累加器和流水线寄存器组成[6]。从图1中可以看出,每个处理器单元由一个乘法器和一个加法器构成,这种结构很适合用FPGA内部的DSP块实现。

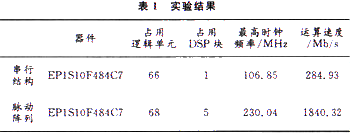

实验结果如表1所示。为了便于比较,使用相同的器件,还给出了串行结构FIR滤波器的实验结果。在串行结构中,每次计算1个x(n),需要3个时钟周期。脉动阵列结构每次计算5个x(n),需要5个时钟周期。每个x(n)为8 b数据。运算速度可以由下面的公式得出:

运算速度=(每次处理数据长度/运算耗用的时钟周期数)×系统时钟频率

从表中可以看出,在占用逻辑单元的数量上二者基本相当,虽然串行结构只占用了一个DSP块,脉动阵列结构占用了5个,但串行结构的最高运算速度只能达到284.93 Mb/s,脉动阵列可以达到1 840.32 Mb/s。显然脉动阵列结构更具优势,可以更好地满足数字信号处理中高效、实时的要求。本文基于脉动阵列技术,设计了高效的FIR滤波器,具有模块化和流水线的结构,并充分利用了FPGA资源,达到了较高的工作频率。

5 结 语

FIR滤波器是数字信号处理中的一种基本运算,有着广泛的应用。基于脉动阵列结构,本文设计了高效的FIR滤波器。模块化和高度流水线的结构使得其在FPGA上获得了较好的性能,完全可以满足系统高效、实时处理的要求,提高了系统运算速度并充分合理地利用了FPGA资源。另外,由于脉动阵列自身的特点,各级结构相同,方便扩展,可以实现任意阶的FIR滤波器。

上一篇:32位单精度浮点乘法器的FPGA实现

下一篇:WTB网络HDLC在FPGA中的实现

推荐阅读最新更新时间:2024-05-02 20:38

电力系统谐波(第二版)

电力系统谐波(第二版) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号