从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低嵌入式芯片的功耗已迫在眉睫。

1 低功耗技术分析

表1给出低功耗技术分析表。由表1可见,随着沟道宽度的减少,单位面积上的动态功耗和静态功耗都在不断增加。

这样芯片功耗则可描述为:

式中:CeffVdd2fclock是动态功耗部分。其中a为当前频率下的翻转率;Ceff为节点负载电容;Vdd为工作电压;fclock为工作频率。IleakVd是静态功耗部分,其中Ileak为漏电流。由式(1)可知,降低芯片功耗所需要降低的参数。

1.1 降低动态功耗的手段

1.1.1 降低α

降低α有两种方法:一是通过工具优化逻辑结构来降低α;二是通过编码方式来实现低的α,例如采用翻转码。实际上假设每一次翻转都是有效和最优的,则afclock可视为一常数,但真实情况并非如此,每次时钟驱动下的设计往往存在冗余,同时对于某种额定的上层任务本身,也可能不适合软硬件划分。对于fclock,若不使用该模块时,可直接gated该模块。这种gated有三种手段:

(1)在时钟产生端进行gated,由软件配置。该手段要求在前端设计这样的功能,包括正向时钟gated和反相时钟gated,其结构是对称的。实际上设计时,器件lib会提供标准的gated单元,这使得前端设计变得较为容易。

(2)在模块中进行硬件判断,以gated clock时钟。例如,在AHB总线上有一块memory,作为AHB从动装置。由于软件频繁访问该模块,因此若采用软件频繁gated,则导致操作不连续;若将模块设计在内部,则因AHB的HSEL信号变高,下一拍时钟在模块内部被打开,这样即可节省时钟翻转的功耗。尤其对于memory来说,时钟翻转和不翻转的功耗差别较大。

(3)利用综合工具在近端加gated,而无需在前端设计。

理论上,单纯的频率下降,并不能带来功耗的变化,因为工作量一定,频率的下降只能带来运行时间的增加,但是芯片功耗中,时钟树的功耗几乎占去30%,所以在合适降低频率时,会减少时钟树上的功耗。

1.1.2 降低Ceff

Ceff的降低因工艺选择的不同而存在较大的差别。因此,选择合适的工艺更有利于降低Vdd这样可使功耗得到平方关系的下降。然而,基于成本、可靠性及商务等考虑,只能选择某一种工艺,如130 nm工艺,可通过DVFS来改变电压。它的核心是:(1)某种工艺下的library可以在一定电压范围内工作正常。

(2)由于模块或系统工作在不同任务下所需的工作频率不同,因此可以计算DVFS的收益。假设一个系统可以进行MP3或MP4的解码任务,这样在MP3解码时,所需频率只有100 MHz;在MP4解码时,所需频率是200 MHz。通过STA分析,在1.1 V电压下工作时,系统可运行频率为100 MHz;在1.3 V电压下工作时,系统可运行频率为200 MHz,这样便可采用DVFS技术调节。假设翻转率、电容都没有发生变化,则在两种不同工作模式下,所需功耗下降64%。当然,前面的数值都是假设的,实际情况并非这么理想。

1.2 降低静态功耗的手段

降低静态功耗可采用Multi-Vdd,Multi-Vth两种方法,在此不做详述。[page]

2 DVFS系统

如果DVFS是基于CPU自身OS调度的需求,则在自身频率需要变化时才进行电压变化,此时可认为是一个开环的DVFS技术。比如说,Windows Mobile中的OEMidle进程就提供了一个根据CPU占用率来调节CPU频率和电压的方式。但是,在采用开环方式调节时,需要足够的余量,同时需要软件,尤其是操作系统予以支持,这对软件来说也不是透明的。

对于一个闭环系统,则需要一个性能monitotor,以监控性能,并根据性能变化,直接调节电压和频率。图1给出一个简单的自适应DVFS系统。

在该系统中,CPU是一个电压可变的power do-main,称为CPU-subsys。然而,对于其他模块,则是另一个power domain,称为peri_subsys,其中包括外部memory接口(EMI)、媒体协处理器(MCP)、LCD控制器(LCDC),以及与电压控制相关的PerformaneeMonitor(PM)模块,用于对芯片性能进行正向监控;.Power Controller(PC)模块用于在接受到PM的性能描述后计算得到控制参数,并传递给Power Supply(PS)模块,用于提供可变的电压Vdd_arm,同时armsubsys与peri subsys之间有Level shifter相隔。

对于PM模块,ARM可以通过总线进行配置,PM通过监测可变电压区的电流实现性能监控。对于处理MIPS需求比较高的操作,CPU空转时间变少,电流需求变小;对于处理MIPS要求比较低的操作,CPU执行密集操作,电流需求变大。

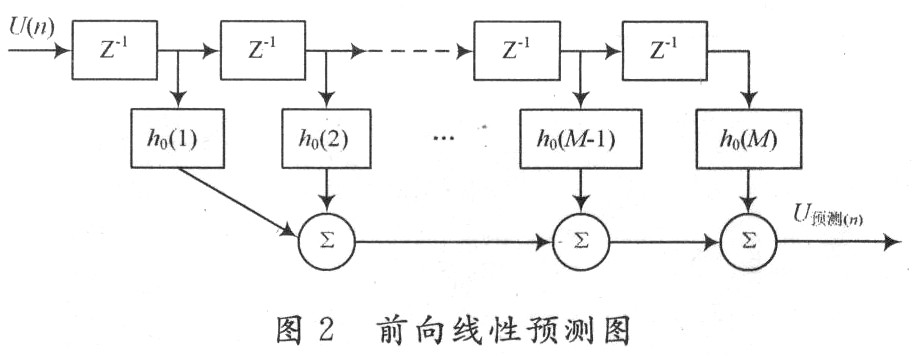

该设计核心在于如何使PM模块能根据某种算法来自适应地预测电流的需求,而且预测的响应时间、额外功耗都比较小,即达到适时、恰好的电压要求。对于自适应算法,可选取图2所示的简单前向线性预测。

3 仿真实验与结果

图3给出系统模型。构造这样一个系统,使得测试将按事先在开发板上的运行给定benchmark程序。测试得到的功耗参数,则按CPU负载折算成为归一的nop和mac两种类型指令程序,这两种指令在测试向量中间或分布。CPU行为模型执行相关程序,该模型只能取指令,执行2级流水。对于nop操作,在执行阶段进行nop;对于mac:操作,在执行阶段对固定数据进行mac,这样即可简化设计。CPU BM采用Verilog进行编写。CPU有一条AHB总线,对memory进行访问控制。MEM模块采用ahb接口,存放编译好的二进制指令,并固定频率。PM Model对CPU BM的翻转率进行monitotor在监控各阶段的翻转率后,作为输入流入自适应滤波器,计算得到所需的调节电压,给PS Model;同时输出翻转率,给PC Model。

PC Model将翻转率、时钟、电压作为输入,用于计算系统功耗。PS Model按照PM发出的电压调节指令进行电压频率调节。由于是rtl Model,所以电压调节是不可见的,只是按照实际情况,若电压从低到高,则先调节电压,再调节频率;反之亦反。

对于自适应选取的电压,可按图4予以实现。表2给出按照130 nm工艺实现电压时,CPU与总线频率的关系。在调节电压时,时钟被停顿若干时钟周期。假设电源网络的RC参数不变,则认为电压切换与切换电压差成正比,如图4所示。

对于前向预测的步长,按照实时操作系统的节拍,从1~50 ms进行调节。通过实践,可得图5所示不同步长下的不同功耗数值,同时每次切换的额外开销也计算在内。

由图5可见,对功耗、效率与调节步长都有一定的关系,合理选取调节步长后,可得效率与功耗的均衡。采用步长为25 ms时,功耗不到DVFS的25%,而效率损失只有1/3。由此可见,在CPU资源总负荷利用率为30%时,该步长相对较为合理。

4 结 语

提供了一种自适应动态电压频率调节方式,构造了与之对应的系统模型。在计算机上对该模型进行了模拟实验,得到一组均衡的前向预测参数。实验结果验证了自适应动态电压频率调节方式的有效性,给出了评估动态电压频率调节仿真的有效途径。

上一篇:基于FPGA的可重构计算技术及其应用

下一篇:基于DSP和FPGA技术的低信噪比雷达信号检测

推荐阅读最新更新时间:2024-05-02 20:50

- UWB在汽车电子通信中的应用

- 恩智浦2.4亿美元收购Aviva Links,布局车载Serdes

- 商用车自动驾驶,迎来大规模量产「临界点」?

- 宁德时代巧克力换电生态大会将举行,什么是“巧克力换电”?1.5分钟换电能实现吗?

- 新型生物材料与高端医疗器械广东研究院、远诺技术转移中心加入面向初创企业的 MathWorks

- S5PV210 Linux字符驱动之PWM蜂鸣器驱动

- 尼得科机床新增可实现高效加工的高速主轴产品线

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Bourns推出全新高效能、超紧凑型气体放电管 (GDT) 浪涌保护解决方案

电动汽车SOC估算方法

电动汽车SOC估算方法 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号