O 引言

PROFIlBUS-DP现场总线以其高速、低成本等优点而广泛应用于制造业自动化、流程工业自动化和楼宇自动化等行业,它的物理层数据传输依赖RS-485接口。RS-485接口是一种工业领域内广泛使用的串行通信接口,可采用“差分”方式在屏蔽双绞线中传输信号,因而具有较好的抗共模干扰能力,通信距离可达千米。PROFIBUSDP总线信号也可使用屏蔽双绞线传输,数据速率为9.6 kbps时的理论传输距离为1200米,波特率为12:Mbps时的理论传输距离为100米。但是,由于工业现场情况错综复杂,各种干扰相互叠加,且RS-485标准规定单段网络最多可支持32个节点(标准负载),因此,有必要使用一种中继设备来将信号更准确、更完整地传输到远端设备。而光纤和其他传输介质相比具有宽频、低损耗、屏蔽电磁辐射、重量轻等优点,因此,用光电收发器实现两线制DP(RS-485)差分信号数据与光信号之间的转换,能够有效的提高信号传输距离和传输质量,从而提高系统的可靠性与稳定性。

1 光电收发模块的配置原理

本光电收发模块的使用配置如图1所示。从物理层来说,原来的一个网段被光纤分成两段,此时。收发器应视为相应段的总线末端,因此,在收发器中默认内置了有终端匹配电阻,以使负载端输入阻抗与传输线的特征阻抗相匹配,从而达到消除负载端信号反射的目的。每一个光电收发器在电气性能上都占一个节点,因此,每段总线上最多可以带30个标准RS-485负载设备。

[page]

[page]

2 总体设计方案

图2所示是光电收发器的硬件结构框图。该设计方案整体上由DP总线数据收发部分、光纤数据收发部分和数据传输方向控制部分组成。 FPGA作为主控制器负责控制数据传输的方向、检测波特率和数据交换功能。其中电源部分采用隔离的DC/DC来减少外部电路的影响。电端DP总线的RS-485收发器可选用SN75HVD06D,该芯片可支持10 Mbps数据速率;而光端的数据接收器和发送器则可选择AVAGO公司的光发送器HFBR-14x4Z和光接收器HFBR-24x2Z,它们在50mA电流驱动下,其62.5/125μm的多模光纤传输距离可达2 km。FPGA芯片选用ALTERA公司的Cvclone系列芯片EPlC3T144C8N,该芯片有2910个LE单兀、1个PLL和144个IO引脚,且性价比较高。

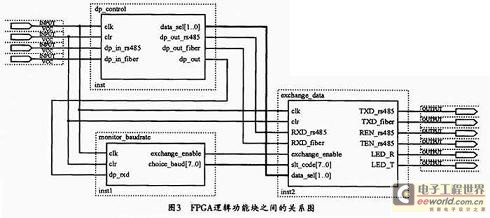

3 FPGA逻辑设计

FPGA包括数据传输方向检测功能块、波特率检测功能块、数据交换功能块等三个逻辑功能块。它们的电端和光端都默认为接收状态。数据传输方向检测功能块用于判断哪个端口先来数据,然后把该端口数据输出到波特率检测功能块以检测其数据波特率,数据交换功能块可根据确定好的数据传输方向和波特率来切换RS-485收发器的收发状态,并最终实现数据的光电转换传输。该三个逻辑功能块之间的关系如图3所示。

[page]

[page]

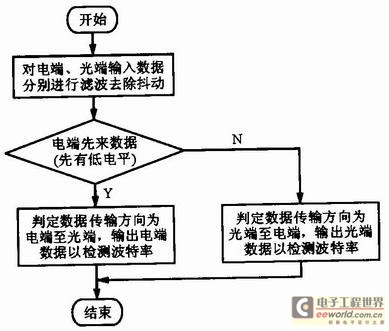

3.1 数据传输方向检测逻辑

PROHBUS-DP总线协议的传输依赖RS-485接口,故在总线空闲状态下,依靠RS-485接口前端的上拉和下拉电阻即可保证总线上的电平为“1”,RS-485收发器一般默认为接收状态。由于RS-485数据传输为半双工方式,同一时刻。线上的数据传输方向是单向的,且传输数据字节的起始位为低电平,这样,就可以根据电端接收数据和光端接收数据的低电平到来的先后顺序来判断数据的传输方向是从电端到光端,还是从光端到电端。为了避免由于线路上的干扰或者数据收发元器件的特性造成的毛刺,可对接收到的电端数据和光端数据先进行滤波去抖动处理。图4所示为数据传输方向检测流程图。

3.2 波特率检测逻辑

首先应对由数据传输方向检测功能块选择输出的数据进行滤波。不同的波特率分别用相应的时钟对滤波后的数据进行采样,若采到连续16个“1”,则说明总线目前处于空闲状态,下一个到来的低电平既是数据字节的起始位,之后即可开始接收数据,在一个字节(8 bits)的数据接收完毕后,即可判断接收到的数据是否为关键字(关键字为PROFIBUS-DP总线协议数据帧的开始定界符SDx)。如果某一波特率连续找到3次关键字,则将其它波特率连续找到关键字的次数清零。并将原来已经确定的波特率位清零。而当该波特率连续找到6次关键字时,则代表找到了新的波特率,此时可将刚找到的波特率确定为当前系统通讯速率,并将相应标志位置1。[page]

3.3 数据交换逻辑

数据传输方向和波特率确定之后,就可以进行电端和光端的数据交换了。当数据传输方向为电端到光端时,电端RS-485收发器处于接收状态,数据由电端经光发送器发送到光端线线路上;当数据传输方向为光端到电端时,在起始位数据“0”发送完毕之后,即可将电端RS-485收发器改为发送状态,在经过10个当前通讯波特率的bit时间后,再将RS-485收发器改为接收状态,并等待接收新的数据。图5所示为数据交换流程图。

4 结束语

该设计的创新点在于其采用FPGA硬件实现光电信号之间的转换,可以自适应波特率变化,并自动检测波特率变化。能支持PROFIBUS-DP协议规定的所有波特率,且转发数据无错包。与一般的RS-485中继设备相比,不但在传输距离和总线的负载能力上有很大提高。而且在抗干扰和通讯的稳定性方面也有突出优势,可用于各种的PROFIBUS-DP总线工业现场。

上一篇:Achronix将采用英特尔22nm工艺打造尖端FPGA产品

下一篇:20×18位符号定点乘法器的FPGA实现

推荐阅读最新更新时间:2024-05-02 21:11

- 2016年是德印象测试微视频网络竞选(大中国区)

- 齐聚一堂 恩智浦教大家玩转新一代物联网应用 观看视频答题有好礼!

- “西北模电王”新概念模拟电路2——《负反馈和运算放大器基础》

- TI 邀您填问卷赢好礼|私人定制专属你的 2019 工业应用方案

- 证明自己,VICOR技术问题测试问卷,等您来挑战!好礼等您拿!

- 【已结束】PI 直播【适合工业市场辅助电源的碳化硅和氮化镓 IC】(9:30入场)

- TI Sensor Menu 助力感应全世界——下载有礼!

- Mentor线上研讨会 | 教你在设计工具中进行DFM分析,轻松兼顾效率、成本和质量

- 【EE团】TI M4开发板超低价尝鲜体验,分享心得赢百元返现!

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号