(1)留言提示:按下采集键时,可采集来访者的图像和语音留言,并把图片以彩信的方式发送。

(2)时钟及手机号设定。

(3)用户管理。

(4)备忘留言。

(5)真人语音报时。

(6)自动待机及屏保。

(7)Windows兼容的存储文件格式。

1 系统设计概述

系统分为语音采集存储播放、图像采集存储、图像压缩、彩信传输、触摸屏驱动及显示等几大部分。整体系统在架构上又可以分为软件及硬件设计两大部分。系统功能框图如图1所示。

设计基于Terasic公司的DE2—70平台,采用Altera公司的Cyclone II系列的FPGA器件和Terasic公司提供的130万像素的CMOS摄像头、800 400分辨率的触摸屏以及PTW73型GPRS MODEM。图像采集采用纯硬件实现,以SDRAM作为缓存。NIOSII处理器从SDRAM中读取采集到的图像并进行JPEG压缩后由串口通过彩信猫发送出去。语音的采集存储播放由软件实现,使用Altera公司大学计划的IP核完成对音频芯片WM8731的配置。触摸屏利用用IP核进行图片和字符的显示控制。系统设计中的语音和图片等信息都存放于SD卡中。对以上功能采用了如下的一些处理技术或特点:

(1)设计基于Avalon总线架构,充分利用现有的Altera公司提供的IP核资源,包括音频芯片的配置、VGA控制显示、存储器的控制等,并设计添加了针对系统时钟、采集端口、触摸屏端口的IP核。

(2)对语音信息的采集和播放进行速度上的优化。由于CPU对SD卡的读写速度较SDRAM慢,故在采集和播放音频信息时,在SDRAM中单独开辟一个缓存区用以存放音频信息。

(3)由于采集到的bmp图像容量较大,设计中采用静态图像压缩标准JPEG对图像进行压缩,以便于图片进行彩信传输。

(4)彩信传输基于GPRS传输协议和AT指令集,通过RS232串口与主机进行连接。

(5)系统中的实时时钟采用硬件方式实现,为CPU提供更多的时间做其他处理,提高了处理性能。

(6)系统与用户的交互主要通过触摸屏实现。

(7)设计中对一些耗时的部分算法进行了自定义指令加速,在一定程度上缩短了系统的处理时间。

2 系统设计架构及流程

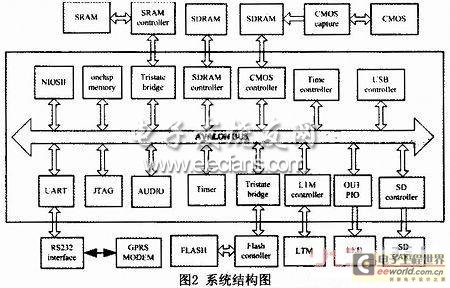

系统基于Avalon总线,采用软硬件协同设计的方式。图像采集、对触摸屏的配置和系统时钟等采用硬件方式实现,其他模块利用SOPC进行定制,完成整个系统的搭建。系统架构图如图2所示。

设计基于NIOSⅡ处理器,软件采集发送功能设计流程如图3所示。总体设计上,软件可以分为采集发送部分和系统主菜单,并且设计上充分考虑了用户的需求,增加了诸如语音报时、电子时钟、定时播放等功能。[page]

3 系统设计实现

系统的功能模块主要包括以下四个部分:图像采集与压缩;音频采集和播放;彩信传输;触摸屏驱动及显示。

3.1 图像采集与压缩

图像采集采用硬件方式实现,基于130万像素的CMOS摄像头,采集系统结构框图如图4所示。采用I2C总线对摄像头进行配置,SDRAM作为图像缓存器。由于CMOS摄像头输出数据格式为Bayer pattern,故需要把其转换为RGB三颜色以便于图像的显示、存储与压缩。存于SDRAM中的图像通过一个读取端口与avalon总线连接。采集芯片以25MHz的主时钟工作,输出640 480像素大小的图像数据。双端口SDRAM控制器工作于100MHz的时钟频率。

当完成图像的采集后,NIOSⅡ处理器通过avalon总线从SDRAM中读取图像像素值并加入bmp格式头文件以bmp图片方式存储于SD卡中。每隔一个像素点读取一个像素值,把bmp以及压缩后的jpg图片大小存为320 240。在把图像从RGB转换为bmp图片的过程中,采用了自定义指令的方式缩短了转换的时间。为了便于图像以彩信的方式传输到用户手机上,采甩JPEG标准对图像进行压缩,JPEG压缩采用软件方式实现。

3.2 音频采集播放

音频部分使用了Altera自带的IP核完成对音频芯片的配置。首先从音频芯片FIFO中读取音频信息存入SDRAM中,加入wav头文件把采集到的音频信息以wav的格式存入SD卡中,这样做的好处是方便在PC机上对音频进行操作和移植。

3.3 彩信传输

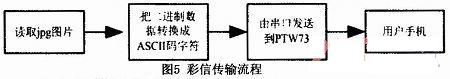

彩信传输通过串口RS232与PTW735奎接。PTW73支持语音及彩信功能的传输,并且内嵌TCP/IP协议,支持完整的AT指令集。彩信传输流程如图5所示。

3.4 触摸屏驱动及显示

触摸屏采用友晶公司提供的TRDB-LTM款800 400像素点24位真彩色的液晶屏。触摸屏的主要功能是完成用户与系统的交互,包括各种按键的控制、图像的显示及实时时钟的显示。触摸屏的配置基于纯硬件的方式,对触摸屏的驱动采用Altera自带的IP核。由于触摸屏的扫描

方向为右上角至左下角,因此在显示图片或字符串的时候需要进行倒像。

4 系统验证

设计采用SOPC Builder进行用户系统的定制,定制好各个模块后在QuartusⅡ9.0下进行了综合,利用NIOSⅡ9.0IDE设计工具在DE2-70开发平台上进行了系统的测试。系统经过调试后达到了预期的目的,各项功能及其子系统能够正常地工作。基于50MHz的系统频率,综合结果该设计消耗了9915个逻辑资源。对系统功能模块或各个子模块分别进行了验证,结果如下:电子时钟模块采用硬件方式实现,其Modelsim SE 6.2b仿真结果如图6所示,完整地实现了包括年、月、日、时、分、秒的电子时钟功能。

图像采集及压缩部分的验证结果如图7所示。其中图7(a)为系统采集并转换生成的bmp格式图片,图7(b)为系统压缩后生成的相应jpg格式图片。

5 总结

设计基于DE2-70平台,利用Quartus II 9.0、NIOS II9.0 IDE、Modelsim SE 6.2b等设计工具,采用软硬件协同设计、自定义指令加速等设计技术,实现了声音图像采集播放等功能,并且支持用户的管理功能。设计针对家庭用户不仅实现了用户留言功能,并且具有近乎实时的留言提醒和电子钥匙等功能,具有实用价值。

上一篇:FPGA实现复接与分接系统

下一篇:基于CoolRunner CPLD的MP3应用开发板的设计

推荐阅读最新更新时间:2024-05-02 21:32

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号