辐射的影响

按照是否能造成原子或者分子的电子脱离,辐射主要分为电离性和非电离性两大类,如图1所示。高能粒子或者电磁波包括X射线和γ射线都能够产生电离的作用。半导体器件受电离性的辐射影响较大,日常应用中以粒子引起的电离性辐射最常见,而其中,以α粒子和中子的影响力较大。

对于太空和地面的应用而言,辐射效应可以分为两大类,单事件效应(SEE)和总离子剂量/总剂量(TID)。在对地面的应用中,单事件效应比较普遍,SEE是高能带电粒子在器件的灵敏区内产生大量带电粒子的现象,SEE的种类很多,尤其以单事件闭锁(SEL)和单事件/粒子翻转(SEU)最难处理。当辐射在器件内造成一定程度的离子化的时候,导通大电流,发生单事件闭锁现象,即使在最轻微的情况下,这种闭锁现象仍会引起芯片循环上电,严重情况下芯片会永久损坏。但是,值得高兴的是,已经可以使用芯片设计和工艺技术来减少单事件闭锁发生的几率。

一般电子应用中遇到的辐射问题来自于天然辐射,包括由太阳和宇宙的影响造成的因素造成。星系宇宙射线(GCR)是指来自于太空的α粒子、重离子和质子,而太阳主要发射电子、质子和重离子。中子的体积非常小,能够轻易穿过大气层,甚至能穿透整个地球,而且由于其不带电荷,能逃过地球的辐射带陷阱,因此到达地面和半导体产生作用的高能粒子以中子为主。

不同的环境对产生辐射的影响是不同得,辐射通量随着高度的上升成指数增加,在海拔330km时,是太空电子应用的所在地,海拔50km是军用飞机所能达到的高度,这里中子和其他粒子的强度都比较高,随着高度继续降低,辐射的通量随着降低,是商业飞机的应用高度。

地球上的中子来源分为天然来源和人造来源。天然来源是来自宇宙射线与大气中的氧和氮的相互作用,中子是太阳耀斑的副产品。人造来源包括核武器、核反应堆、医疗设备等。

辐射对FPGA器件影响

单粒子翻转 (SEU),是指当一个重离子撞击一个电路节点,沉积足够的电荷使该节点的状态改变。SEU 不仅限于太空应用,也会发生在地面的应用,如医疗、航空电子、汽车、网络和基础设施。

软错误 (soft error)指存储器单元或寄存器中可以校正的翻转,数据被改变,但存储器单元没有损坏,一般影响单一比特位,偶尔影响超过一个比特位。

固件错误 (firm error)指SRAM FPGA 中配置存储器的翻转,它被称为“固件”,是因为错误会一直存在,直到SRAM FPGA重新上电或启动才能清除。固件错误多数导致功能故障,后果比软错误严重得多,它能够引起FPGA失效以及整个系统的故障。

FPGA 器件中的辐射影响分为两大类:数据影响(软错误)和配置影响(固件错误)。医疗等地面应用中的两个重要辐射源则包括中子和α粒子。

数据影响(软错误)数据影响(软错误)包括触发器、存储器单元、组合逻辑单元中的单比特位翻转。如果能够校正错误,则问题不严重,非关键性数据可请求重新发送,对于关键性数据可使用 EDAC/FEC、奇偶校验冗余手段来达到保护的目的。

配置影响(固件错误)是指FPGA 配置元件的单比特位翻转,它可以引起 FPGA 故障,也可以影响数百万比特位的数据,甚至可以引发整个系统的故障。

图2 中子对集成电路的影响

中子对集成电路的影响如图2所示,包括:

•中子可能撞击硅原子,放出重离子

•重离子在 CMOS IC 中引起瞬时电流脉冲

•会改变存储器单元和触发器中的数据

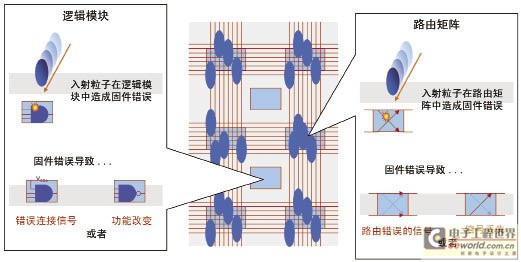

辐射如何引发 SRAM FPGA 失效,引起SRAM FPGA 中的配置翻转呢?如图3所示。

图3 辐射引发SRAM FPGA失效

非易失性FPGA

Microsemi非易失性 FPGA 具有配置翻转免疫能力。分为Flash FPGA和反熔丝FPGA,如图4所示。

图4 Flash FPGA和反熔丝FPGA

Flash FPGA,高能粒子(大气中子、太空中的重离子 )不能产生足够的电荷来让浮栅错误地改变状态。

反熔丝FPGA,反熔丝 FPGA 具有一个永久编程的金属链接,不会因高能粒子和其他辐射而发生改变。

中子导致的数据故障(软错误),Flash FPGA 和 SRAM FPGA 的数据翻转率相似,这是基于第三方机构 iROC Technologies 所做的分析。

翻转率是以每一亿小时,每百万个触发器计算,每个故障等于一个D型触发器数据的翻转,可以用EDAC/FEC、奇偶校验、CRC等方法轻易校正。

中子导致的配置故障(固件错误),每个故障等于FPGA器件的失效,而越先进的工艺通常故障率越高。

深亚微米技术增加了固件错误发生的概率,半导体的工艺越现金使得由辐射引起的故障率越高,随着CMOS技术工艺尺寸继续缩小,这对固件错误带来实质性影响。如果器件发生翻转所需的临界电荷为QCRIT,QCRIT~VCC×CNODE。更低的电源电压(VCC)增加了固件错误的易感性,使得单粒子翻转更为普遍;更小的栅极面积 (CNODE)使得电容更小,相关的临界电荷也会减少,因此也增加了固件错误的易感性。在CMOS技术中,工艺尺寸的缩小,使得栅极面积减小,并使电源电压降低,这两个因素都会让单粒子翻转变得更容易。

Microsemi下一代的Flash FPGA仍将具有固件错误免疫能力,由于Flash工艺的特点,下一代的Flash FPGA能保持足够大的浮栅电荷QCRIT可以免受大气中子的影响。QCRIT与工艺节点的影响如图5所示。

高能中子在SRAM FPGA中会产生配置翻转和数据翻转两种效应。

配置翻转导致 FPGA 丧失功能,后果十分严重,缓减方式1:三芯片( Triple-Chip )冗余,是把同样的电路复制到三个一样的芯片中,通过表决的方式,当其中一个芯片辐射失效,其余的两个芯片加起来可以仍然可以把正确的结果算出来。但是这种方式消耗过多的电路板空间及功率,而且需要外部元件进行控制和表决。缓减方式2:配置重读和重载,这种方式不断重新配置SRAM FPGA把已有的错误纠正,但是FPGA有机会在重载时再次被中子击中,在高可用系统中是不可接受的。

数据翻转导致单一比特位数据错误,后果取决于数据特性。缓减方式简单,通过FEC、EDAC、数据清除,使用容错性设计技术。

整体而言,缓减方式对SRAM FPGA没有太多作用,因为配置翻转占主导地位,而配置元件占SRAM FPGA的大部分面积。

反熔丝和Flash FPGA不存在配置翻转, Micorsemi FPGA 器件的配置经第三方独立实验室的验证能够耐受中子、质子、γ射线、X 射线以及重离子的影响。反熔丝、Flash 及 SRAM FPGA 出现数据翻转的比率相似,导致单一比特位数据错误,后果取决于数据特性。缓减方式简单,FEC、EDAC、数据清除,使用容错性设计技术,Micorsemi则已经验证了消除数据错误的缓减技术。

随着医疗设备变得越来越现金,在医疗设备中的电子元件含量不断增加,使得SEU变得越来越重要,使用辐射源的应用很重视SEU免疫力。其中包括

•肿瘤科(使用 X 射线/质子源)

•牙科设备,整形设备

• CT扫描,透视,乳房X射线摄影设备

以上这些应用的需求需要可靠的剂量、快速和精确的治疗、III类/ IV型设备需要有最小的停机时间,关键部分的功能不能中断,不能承受功能性错误等。

在网络和基础设施中的 SEU,在大型的网络中往往用到大量的FPGA,特别是一些跨地域的网络,通常会用到成千上万的FPGA,其中一个FPGA若发生问题,也可能会造成整个网络的通信影响,特别是一些高海拔的地区,SEU的效应更为明显。根据统计,在一些大型跨地域的网络中,因为SEU的引起的通信中断每几个小时可能发生一次,思科公司内部也针对SEU提出专门的调试方案和工作条款。

SEU 的免疫力在航空电子中是非常重要的,例如:飞行计算机,驾驶舱显示器;引擎控制和监控,制动;座舱增压和空调;电源控制和分配,飞行表面驱动等。而这些功能如果因为SEU而丧失则是不能接受的。

在在汽车电子中的SEU方面,和医疗应用中非常类似,在汽车设计中,半导体器件的使用越来越普遍,甚至在关键器件中也能看到FPGA的踪影,在汽车行业中,新版本的 AEC-Q100 规范提出 SER(软错误率)的测试需求,使得它成为基于 SRAM 技术的强制性规定。

图5 QCRIT与工艺节点的影响问答选编

总结

辐射对于 FPGA 的影响不局限于太空应用,SRAM FPGA 器件易于发生中子引发的配置错误 (固件错误),即便在海平面上亦然。

反熔丝和 Flash FPGA 在所有高度上都具有配置故障的免疫能力(获第三方独立研究机构确认的数据证明)。对于高可用性/高可靠系统的关键任务,应该考虑使用反熔丝或Flash FPGA。

问:X射线对FBGA有没有干扰影响?

答:有的,它可以产生电离性中子而导致SEU。

问:请问FPGA产品出厂之前,通常进行辐照效应试验吗?

答:抗辐射系列的是会的。

问:FPGA的抗辐射能力和那些因素?

答:与基本架构及工艺有关。

问:磁环、磁珠对于辐射的滤波到底有多大帮助呢?如果是3MHz~10MHz的辐射干扰,应该怎样选型磁环磁珠来对输入的信号进行滤波?

答:这种方法只能对电磁波干扰有作用,对高能粒子无能为力。

问:请问是不是其他的通用MCU容易受到强辐射的影响?Flash的工艺和OTP的工艺受到强辐射的影响会一样吗?

答:OTP、Flash都具有抗辐射能力。

问:非易失性FPGA和反熔丝FPGA器件哪种器件更具有抗辐射能力?

答:反熔丝从原理上更好,但是在测试中两个都未发现抗辐射失败现象。

问:如何测试FPGA器件的抗辐射能力?

答:方法有很多,简单的方法可用FPGA上的存储器组成一个长列的移位寄存器来比较预期结果。

问:在辐射影响方面是配置翻转占主导还是数据翻转占主 导?

答:配置翻转主导,因为配置单元占晶片面积较大,受影响的机率也较高。

问:高温或者低温对FPGA的容错能力有影响吗?

答:在测试中,高温低温未发现异常。但注意器件的工作环境要求。

问:对于已经在使用中的非耐辐射型的FPGA,如何减少辐射的影响?有何建议?

答:使用电路冗余,相当于多备份,灵活切换。但这很复杂,因为关系到检测、判决、切换等。功能受到影响是不可避免的,而且就实际来说,能否实施还很难说。

问:FPGA的可编程I/O受到辐射粒子的影响会产生什么问题?

答:后果可能非常严重,可能造成IO冲突而导致物理损坏。

问:一般情况下,大功率电机运行中产生的电源干扰,数据采集卡或者示波器采集的信号往往发生很大的失真和高频谐波干扰,这种干扰对FPGA的影响如何?

答:这种情况属于EMI/EMC的干扰,与辐射的情况不一样,但有时候会产生有相同的影响。

问:航空FPGA的设计,除了反熔丝技术、三模冗余技术,还有更好的办法吗?Microsemi在工艺上又有什么先进之处?

答: Flash FPGA也可以使用,大部分Microsemi的抗辐射FPGA除工艺本身以外在片上已包含三模冗余。

上一篇:基于SD卡的FPGA配置

下一篇:直序扩频的研究与FPGA实现

推荐阅读最新更新时间:2024-05-02 21:47

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号