引言

降低电子产品的功耗是很现实的问题;在这种越来越强的能源意识以及迫切需要降低功耗的环境下,很多产品开发人员和生产商都制定了发展战略来赢得竞争优势。降低功耗为设计人员和最终用户带来了以下优势:

- 支持开发人员更好的满足对功耗和散热要求较高的市场需求

- 在相同的散热和功耗预算内,开发人员有更大的自由度来提高性能。

- 降低运营和材料成本,实现更紧凑的产品。

- 降低苛刻的散热要求

- 敢于承担社会责任

元器件供应商必须为开发人员和生产商提供最佳选择来降低能耗,满足迫切的功耗需求,不然,在竞争中将会处于明显的不利地位。Altera最新一代28-nm器件帮助产品开发人员和生产商直接满足迫切的功耗需求。

迫切的低功耗需求

美国能源部预测全球发电量到2015年将超过20万亿千瓦时(kWh),2035年达到35万亿千瓦时,如全球发电量未来增长所示。在数据中心以及通信网络的推动下,电子设备用电量增长非常迅速。例如,美国的服务器和其他互联网基础设施的功耗从2000年的200亿kWh增长到2005年的400亿kWh,已经翻倍。Koomey, Jonathan, G博士,美国和全球服务器总功耗预测,斯坦福大学,2007年2月1在同一时期,全球同样设施的功耗从2000年的600亿kWh增长到2005年的1200亿kWh,也已经翻倍。

展望未来,美国数据中心的功耗2011年将达到1000亿kWh,按照这一趋势,2020年将会翻倍。这种快速增长将对经济发展产生很大影响。2015年,服务器运转的能源成本将超过服务器硬件成本智能能源欧洲,高效服务器:——这会显著影响全球通信和数据中心基础设施的经济成本。

在快速增长的用电量中,数据中心只占了其中的一小部分。其他用电较多的领域包括传送数据的通信网络,用作数据流终端的PC和监视器等。所有这些都是信息和通信技术(ICT)部门的组成。很多工业组织以CO2等价排放量来衡量ICT部门的能耗,反映了工业领域排放了多少温室气体。ICT部门每年产生大约相当于500兆吨的CO2,30%来源于有线和无线通信,按照这种发展趋势,2020年将超过14亿吨,如全球ICT CO2排放量分布所示。SMART 2020,在信息时代实现低碳经济:

对能源需求的快速增长促使政府和工业部门进一步提高能效。例如,美国政府是美国最大的能耗单位,每年成本高达200亿美元,它现在通过多种方式来降低功耗,包括只购买能耗小于1瓦或者待机功耗很低的产品。美国联邦能源管理项目,执行号13221,2001年8月2号:

同样的,欧盟制定了法规,要求产品的待机功耗只有1W到2 W,2013年降低到0.5W或者1W。加州也制定了法规,要求2013年电视的功耗降低49%。加州能源委员会,加州通过新的节能电视法案,2009年11月18号:

私人企业和工业组织也在积极采取措施降低功耗。例如,Verizon公司要求所有新设备的功耗必须比老设备低20%。Verizon Wireless,Verizon率先建立网络、数据中心和消费类设备的节能标准,20据工业组织GreenTouchTM,全球通信网络目前产生相当于3亿吨的CO2,Judge, Peter,阿尔卡特朗讯宣布提高网络运行效率1000-Fol,Eweek Europe,20据GSMA移动通信集团,包括便携式设备在内的全球移动通信基础设施产生了相当于245兆吨的CO2。移动通信(GSM)联盟全球系统,Green Manifesto,2009年11月1号:

所有这些组织都建议通过设置一些目标来减少温室气体的排放。例如,GreenTouch建议将互联网和其他通信网络的能效提高1,000倍,采取合适的手段到2015年实现这一目标。GreenTouch计划,Fast Facts:

类似的,GSMA虽然预测2020年移动链接将增长70%,达到80亿,但仍然建议移动领域努力保持目前的全球温室气体排放水平。与2009年相比,到2020年,其目标是每一链接的全球温室气体排放量降低40%。同样的GSMA文档预测“2020年全球排放能效可以提高15%。这是迅速减少排放,而且成本最低的选择。”移动通信(GSM)联盟全球系统,Green Manifesto,2009年11月1号:

理想的低功耗元器件

制定了这些低功耗目标后,产品开发人员必须进一步提高产品性能,同时降低能耗。而且,降低功耗还有助于帮助最终用户提高经济收益。例如,对于服务供应商依靠电子产品作为其商业模型的情况,降低功耗可以减少与电子设备供电和散热相关的运营开支。而且,降低总功耗能够降低实际供电需求。所有这些因素都有利于减小设备规模,降低投入和运营成本。如通过供应链来降低功耗需求所示,这些最终用户需求转换为设备供应商的需求,最终是元器件供应商的需求。

FPGA和可编程逻辑器件(PLD)非常适合产品开发人员通过以下方式,以低成本来控制功耗:

- 将大量的板上逻辑、存储器和处理器元件迅速集成到很少的器件中,甚至是一个器件中。

- 减少支持元件和供电电源数量,减小电路板面积,降低实现复杂电子系统所需要的功耗。

- 支持采用不同的实现方法和算法来精确的调整功耗。

灵活的可编程逻辑具有低功耗优势,在综合考虑全定制硅片的成本和产品及时面市时,它是非常有吸引力的选择。

在28 nm定制功耗

在28-nm节点,设计人员利用Altera器件可以针对特定的目标市场和应用来定制功耗。Altera的方法在28-nm系列产品中利用了多种半导体工艺,针对产品和某些系列体系结构进行了优化,增强了IP。结果,与前一代同类产品相比,Altera的28 nm FPGA功耗降低了40%。

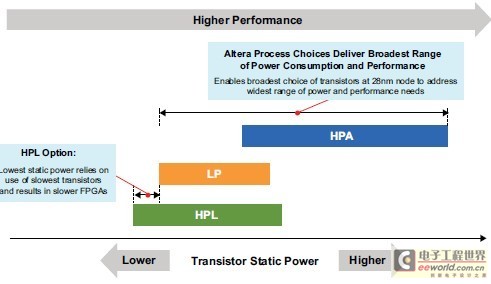

TSMC的28-nm工艺选择 显示了台积电(TSMC)的三种28-nm工艺技术,该公司是可编程逻辑供应商的28-nm节点半导体代工线。在这些工艺中,大量晶体管具有较大的静态功耗范围。左侧的晶体管静态功耗较低,而右侧的较大。这也体现了静态功耗与这些晶体管性能之间的关系。总体上,晶体管性能越好,静态功耗也就越高。Altera在28 nm产品上同时使用了28LP和28HP工艺来提高性能范围,以及多种功耗选择。第三种工艺选择是28HPL,某些晶体管的静态功耗较低,位于标以“HPL Option”的部分中,但是大量使用这类晶体管会导致FPGA运行较慢,对于很多设计人员而言是无法接受的。相应的,FPGA的28HPL工艺需要使用高速低泄漏晶体管,无法体现静态功耗的优势。

在28-nm节点,Altera器件是所有FPGA中总功耗最低的。这些器件之所以具有优异的功耗特性,是因为在产品开发的所有阶段都非常注重降低功耗。从28HP和28LP半导体工艺就开始重视降低功耗。

关于Altera注重降低高性能28HP Stratix V器件系列功耗的详细信息,请参考“降低28-nm FPGA功耗,提高带宽”白皮书。

与Stratix V系列不同,Altera的其他28-nm FPGA产品——Cyclone V和Arria V系列,设计用于不需要绝对最高性能和带宽的应用。结果,它们基于28LP工艺,设计用于提供最低总功耗,如TSMC所述:

“与TSMC的40LP技术相比,基于SiON的28LP工艺采用了该系列中最低总功耗和高性价比技术,其逻辑密度将翻倍,速度提高50%,功耗降低30-50%。”

其他在28-nm节点寻求绝对最低功耗的主要半导体供应商也选择了28LP工艺,正如Qualcomm所宣称的那样:“Qualcomm与TSMC合作,推出了我们的Snapdragon™ S4类处理器,包括Snapdragon S4 MSM8960™,它是高度集成的双核SoC,设计满足了前沿智能电话和平板电脑的低功耗需求。Snapdragon S4类处理器采用了TSMC非常复杂的28LP工艺,使Qualcomm能够突破性的实现了高性能和超低功耗的移动设备。”TSMC新闻发布,“TSMC 28nm技术达到量产”,2011年10月24号:

在低功耗基础上,Altera还采取了其他措施来降低28LP器件的静态功耗,包括大量使用“低泄漏”晶体管等,从而降低了静态电流。此外,Cyclone V和Arria V系列还提供一些可以禁用的器件特性,包括收发器、I/O块、PCI Express模块、存储器模块以及分段式PLL等。这些特性相结合,与前一代FPGA相比,器件静态功耗降低了70%。例如,Arria V系列的器件功耗在500K LE时不到750mW,比目前的中端和高端40-nm FPGA静态功耗低得多。而竞争28-nm FPGA的静态功耗是Arria V FPGA的2.6倍。 Arria V静态功耗对比显示了Arria V GX器件的典型静态功耗,以蓝色实线表示,而以蓝色点线表示最差情况下的功耗。类似的,红色实线表示竞争中端28-nm FPGA的典型静态功耗,点线表示最差情况下的功耗。借助这些特性,在同类FPGA中,Arria V器件的静态功耗是最低的。

|

图5.Arria V静态功耗对比 |

低动态功耗体系结构

除了低静态功耗,Altera Cyclone V和Arria V器件的动态功耗也较低,从而实现了最低总功耗。Altera从28LP工艺开始采用了降低动态功耗的方法,主要面向低功耗应用,包括,便携式消费类、无线链接和蜂窝基带等。TSMC阐述了提供高级工艺来实现最低总功耗而不仅仅是静态或者动态功耗的原因:

“我们之所以决定为28LPT工艺开发可靠的SiON技术,是因为无线和便携式消费类应用需求在不断变化,我们一直面对产品要符合市场需求的压力。消费者几年前需要低泄漏手持式设备,要求电池能够使用较长的时间。今天的消费者越来越依靠无线设备来浏览互联网,观看视频,听音乐,使用移动电视、GPS导航,以及传统的电话和文本服务等。主动应用功耗现在是电池使用时间的主要因素。SiON逻辑门技术由于具有较小的栅极电容,因此,动态功耗比HKMG (高K金属门)低,对于功耗受限的应用,提供的解决方案具有较低的总功耗,成本和风险也很低。”

28LP工艺具有较低的栅极电容,有源栅极电容比28HPL低30%。在Cyclone V和Arria V器件中,Altera还采用了其他方法来降低器件电容,包括用于存储器控制器的硬核IP、PCI Express,还提供收发器协议支持,减小了管芯面积及其相关电容。最后,与Stratix V器件相比,Altera还针对Cyclone V和Arria V器件的基本体系结构模块进行了优化。这些优化措施减小了硅片面积以及相关的电容,使得28LP器件系列满足了目标应用的性能要求。例如,Arria V器件逻辑阵列模块(LAB,10个自适应逻辑模块)的管芯面积比Stratix V LAB小40%。Cyclone V和Arria V器件的硬核存储器控制器也同样减小了管芯面积以及外部存储器接口的相关电容。所有减小器件电容的这些措施都降低了动态功耗,符合下面熟悉的功耗公式,其中,C表示开关电路的电容:

动态功耗 = 1/2CV 2 × f

Altera还降低了器件收发器的动态功耗。Altera丰富的收发器设计专业知识在业界是首屈一指的,其独特的优势反映在收发器较低的动态功耗上。例如,在6 Gbps,Arria V收发器功耗不到100mW,比28-nm竞争FPGA的功耗低得多,如85C结温,6 Gbps时每通道的收发器总功耗所示。对于采用了36个收发器Arria V器件的设计,功耗降低了5W多。

Altera在28-nm节点实现了较低的收发器功耗,这是因为我们经过了多年的磨炼,增强了专用体系结构。在可编程逻辑业界,只有我们能够持续不断的发展高级收发器技术,因此,功耗一直在逐步降低。竞争解决方案每一代产品的收发器功耗都在增加,如所示,画出了收发器物理介质附加层(PMA)功耗与多代FPGA之间的关系曲线。

|

图7.收发器功耗的历史发展趋势 |

通过这些静态和动态功耗优化措施,Altera基于28LP的FPGA总功耗比前几代器件降低了40%,全面降低了功耗,如Cyclone V降低了功耗所示。

|

图8.Cyclone V降低了功耗 |

显示了Arria V器件相似的结果。

|

图9.Arria V降低了功耗 |

通过软件创新降低功耗

在工艺和体系结构创新基础上,Altera在Quartus II的软件功耗优化方面进行了大量的投入。功耗驱动的编译使用功耗驱动综合和功耗驱动布局布线功能,主要用于降低设计的总功耗。对于设计人员而言,这种功耗驱动的方法是透明的,通过简单编译设置来实现。设计工程师将时序约束简单地设置为设计输入过程的一部分,对设计进行综合,满足性能要求。Quartus II为每一功能模块自动选择所需的性能,并通过功耗预知布局布线和时钟技术来降低功耗,如包括自动功耗优化的Quartus II设计流程所示。

Quartus II软件在不同的编译阶段采取各种措施来降低设计的总功耗。在综合阶段,Quartus II软件提取时钟使能信号,进行时钟选通,减少对RAM模块的访问,重新构建逻辑以避免高触发网。在适配阶段,Quartus II软件找到高触发网,以降低动态功耗,优化逻辑布局,减小时钟功耗,实现高功效DSP和RAM模块配置。最后,在汇编级,Quartus II软件对未使用的电路进行编程,尽可能减小触发,或者进行关断。最终的设计以最低的功耗满足了设计人员的时序要求。

如Quartus II软件的功耗优化设置所示,设计人员可以选择不同级别的功耗优化选项,以满足设计约束要求。选择Extra Effort设置,最大限度的降低功耗,代价是较长的编译时间。不同的设计,选择不同的努力等级会有不同的结果。这一特性降低了功耗,不需要设计人员的干预,同时减小了对设计性能的影响。此外,在详细的电路模型和高级统计方法的指导下进行功耗优化,估算哪些信号是被经常触发的。通过这些信息,Altera确定高功效实现方法,不需要设计人员的额外输入(例如,对设计进行耗时的仿真以确定开关速率)。

|

表1.Quartus II软件的功耗优化设置 | |

|

设置 |

说明 |

|

Off |

没有进行网表、布线或者性能优化来降低功耗。 |

|

Normal |

采用低计算努力等级算法,通过网表优化来减小功耗,前提条件是不会降低设计性能。 |

|

Extra Effort |

采用高计算努力等级算法,通过网表优化来减小功耗。可能会影响最佳性能。 |

基准测试

Altera为业界提供最先进、功耗最低的FPGA。通过基准测试来估算各类典型应用的总功耗,进一步表明了Arria V器件相对于竞争28-nm器件的低功耗优势。Arria V FPGA和竞争28-nm FPGA的总功耗对此显示了这些基准测试的结果,这些都记录在Altera wiki网站上,以便进一步进行研究学习。

结论

Altera低功耗28-nm器件的优点包括,降低产品成本,降低或者放宽功耗预算,较低的散热要求,能够满足更多的市场需求,在同样的散热和功耗预算内进一步提高性能等。采用最全面的方法降低28-nm产品的功耗,Altera帮助设计人员满足了迫切的低功耗需求。

上一篇:2012 暑期大学教师培训研讨会Xilinx Workshop 天津

下一篇:Xilinx CTO清华大学演讲描绘All Programmable蓝图

推荐阅读最新更新时间:2024-05-02 22:08

英特尔167亿美元收购Altera的五大理由

6月2日消息,据国外媒体报道,英特尔于周一宣布以167亿美元收购FPGA生产商Altera。此交易为该公司有史以来涉及金额最大的一次收购案例。英特尔为何愿意出巨资收购一家目前看似与自身业务并不相关的企业,外媒PCWorld给出了以下五大原因:

一、整合CPU技术与FPGA技术

收购FPGA巨头,意味着英特尔如今已在考虑CPU之外的新技术应用。FPGA是可以作为类似GPU一样的加速技术被整合到处理器产品中的。

二、进一步丰富服务器产品线

服务器芯片是英特尔的摇钱树,尤其是在PC市场不断萎缩以及迟迟打不开移动市场的大环境下,这种价值更是得以凸显。然而目前,英特尔正在为企业客户提供着整合了第三方FPGA产品的芯片

[手机便携]

Altera为FPGA提供首款集成100G EFEC解决方案

Altera公司今天宣布,开始提供业界第一款集成增强前向纠错(EFEC) IP内核,该内核针对高性能Stratix IV和Stratix V系列FPGA进行了优化。EFEC7和EFEC20是Altera Newfoundland技术中心 (以前的Avalon Microelectronics) 开发的多维IP内核,专门面向城域和长距离光传送网(OTN)等100G应用而设计。 当今的服务供应商将其10G城域和长距离OTN网络升级到100G速率,以支持视频数据越来越高的带宽需求,并且开始规划未来的400G应用。此外,这些骨干网络在光纤上的传输距离要延长25-50%,同时实现低功耗、低成本和低延时。Altera的EFEC IP

[嵌入式]

28nm供不应求 台积电拟调高资本支出

由于28奈米制程产品需求强劲,台积电(2330)正加速扩产,市场传出台积电今年资本支出60亿美元(约1772亿元台币)将上调,对此,台积电企业讯息处长孙又文证实,目前28奈米的市场需求的确大于产能,内部评估调升资本支出,但上调幅度尚未决定。 台积电虽在元月的法说会上才宣布今年的资本支出60亿美元,较去年的72.86亿美元(约2151.7亿元台币)减少17.65%,当时董事长张忠谋认为,台积电于前2年在扩大资本支出上已相当积极,但因各种制程可相互转换,因此并未造成12寸产能供过于求,同时也将针对65奈米制程适度将产能转换至28奈米,因此60亿美元的支出应该足够。 客户正在排队抢产能

距上次法说会仅经2个

[手机便携]

Altera Arria GX FPGA支持松下P2驱动器

在准时高效的广播行业,每一分钟都至关重要。提供支撑技术以加速视频传送过程,Altera公司今天宣布,松下公司在其新的AJ-PCD35、5槽P2 (无带格式)存储器卡驱动器中选用了Altera的Arria® GX FPGA、PCI Express (PCIe) MegaCore® IP和Nios® II处理器解决方案。 松下公司新的存储驱动器使用了PCIe接口,提供从P2卡到非线性编辑系统的视频读写功能,同时可以从多个存储器卡传送数据,与传统驱动器相比,大大提高了传送速率。松下AJ-PCD35可以直接读写5个卡的内容,不但帮助专业广播人员提高了节目内容的数量和质量,而且满足了时限要求。4月20号到23号在拉斯维加斯会议

[手机便携]

看好光网络前景 FPGA厂商加紧收购

FPGA供应商赛灵思(Xilinx)日前表示,公司已收购了一家贝尔法斯特(北爱尔兰)通信初创公司Omiino,此前,AppliedMicro及Altera此前分别收购了光传送网IP供应商Tpack A/S及Avalon。 Omiino成立于2007年,由前Amphion半导体、伟创力及北电员工创建,2008年公司获得210万美元种子基金,利用FPGA来开发通信网络设备。 Omiino利用来自于Altera或Xilinx的FPGA进行二次开发,销售给部分特定的电信领域。Omiino为10G、20G、40G及以太网光网络产品提供成帧器/映射器,Omiino员工共有16人、 “我们一直非常努力地开发这一令人兴奋的技

[嵌入式]

1080亿元现金 Intel正式完成收购Altera

Intel今天官方宣布,已经正式完成了对FPGA厂商Altera的收购流程,167亿美元(约合人民币1080亿元)的交易额也已全部以现金方式支付(有钱任性)。这笔交易是今年6月1日正式宣布的,此前已经先后得到欧盟和中国的批准。 Altera今后将以 可编程方案事业部 (Programmable Solutions Group)的名义在Intel麾下运作,不过按照Intel此前说的,Altera仍将继续保持独立运营,其品牌和产品计划完全不变,客户们也不必担心。 早先对安全厂商McAfee的收购,Intel采取的也是同样的处理方式,过渡很顺利。 Intel表示,收购Altera将使其在高速增长的数据中心、IoT物联网市场

[模拟电子]

Altera与骏龙环球签署6个东南亚国家分销协议

Altera公司近日宣布,与骏龙环球有限公司签署了6个东南亚国家的分销协议。骏龙环球有限公司现在是Altera在新加坡、马来西亚、泰国、菲律宾、印度尼西亚和越南的授权代理商。这一扩展协议完善了Altera在亚太地区现有的分销网络。 Altera公司亚太区副总裁兼董事总经理Erhaan Shaikh表示:“我们看到东南亚地区有强劲的增长,设计工作也越来越多,相信与骏龙公司签署扩展协议会进一步增强对客户的服务和技术支持。骏龙公司优秀的销售和现场应用团队与Altera在中国合作了多年,我相信他们能够帮助Altera进一步拓展在东南亚地区的市场份额。” 骏龙公司总裁Johnny Chan说:“我们非常荣幸能够有机会

[嵌入式]

中端FPGA工艺下探 莱迪思新平台导入了28nm FD-SOI技术

高端FPGA市场有赛灵思和英特尔两条巨龙盘踞,莱迪斯几乎未曾踏入这山头半步,那么是如何成为世界第三大FPGA厂商的呢? 今年,赛灵思和英特尔展开了对“世界最大FPGA”宝座的角逐,分别发布了16nm和14nm的两款FPGA芯片。做最大的FPGA,秀最纯粹的肌肉,这样高的技术壁垒让多少城外想进来的人撞得头破血流。因此,莱迪斯做了一个聪明的决定,只专注在中低端FPGA领域,努力从中端市场获得成长。 打破两个局限性 在过去,莱迪斯的战略有一定的局限性,第一个局限性体现在应用领域方面,莱迪斯几乎只做消费类。第二个局限性则是由于产品研发模式僵硬,导致的技术很难复用。 近年来,5G、机器视觉、自动驾驶等新技术的兴起引起了莱迪斯的重视,莱迪

[手机便携]

高级CC++编译技术(Advanced C and C++ Compiling) (Milan Stevanovic (译)卢誉声)

高级CC++编译技术(Advanced C and C++ Compiling) (Milan Stevanovic (译)卢誉声) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号