随着各种高速长时间物理实验要求的不断提高,系统对高速的数据采集模块的需求也越来越高,在许多特殊应用的场合中,系统也需要对大量突发的数据进行采集处理,用FPGA实现的高刷新率高分辨率图像采集系统,用于船载雷达图像记录。该系统由AD、FPGA、SDRAM组成,AD芯片把雷达提供的以VGA接口方式给出的图像信号转换成数字信号,FPGA控制时序通过整页突发的模式写入SDRAM中,并提供了后续处理的接口。

中国船级社规定从2004年开始,在国内和国际航行的船舶中都必须安装船载航行数据记录仪,其中船载雷达图像记录仪是很重要的一部分,船载雷达图像按VGA图像标准输出,其分辨率在640×480-1280×1024之间,刷新率在60-85Hz之间。目前常见的图像采集系统多是针对复合视频信号的采集,或者是针对CCD图像信号的采集。这些图像采集系统并不能满足雷达图像采集的要求,即使少数针对高分辨率高刷新率图像的采集系统也是以计算机板卡的形式出现,运行时需要一台计算机。

目前一些速度高达1GSPS的基于VME总线的数据采集系统,通过4路,每路采集速度高达250MHz的系统实现1GSPS速度的数据采集。但由于该类系统中没有大容量的数据缓存,因此并不能实现高速长时间的数据采集。另外一些系统采用一种基于FPGA,使用多SDRAM作为数据缓存的采集系统。该类系统解决了长时间高速采集的问题,可以对频率为100MHz,16bit位宽的数据进行采集。但是由于它采用了多个FIFO来降低SDRAM的工作频率,使得该类系统应用在需要严格的数据同步的高速图像采集系统中会出现一些数据难以同步的问题,还有一种PC板卡形式的高分辨率图像采集卡,该系统直接对图像进行压缩后存储,并通过PCI接口提供给PC,这种形式既不适合船舶上狭小的空间,也不能满足船舶失事时对数据的保护要求。

本文提出一种高分辨率高刷新率图像采集系统。该系统使用于嵌入式系统中,不仅体积小,还解决了数据保护的问题,可用于船载雷达图像记录系统。该系统可支持对多达4路8bit位宽最高采样率达120MHz的数据通道,或者一路VGA图像信号,可对采集数据进行长时间采集存储。具体的连续采集时间根据系统所采用的SDRAM容量大小有所变化。该系统还为数据的后续处理提供了ASRAM接口,使得用于缓存数据的SDRAM也可作为后续处理CPU的系统内存。这样既可以提高数据的处理速度,方便后续针对雷达图像的压缩或者识别处理,也节省了资源。

采集系统设计

系统分析及芯片选择

首先确定系统要求。目前标准规定的VGA分辨率从640×480-1280×1024之间可调,刷新率为60-80Hz可调。系统应能接受最高情况为分辨率1280×1024,刷新率60Hz。在这种情况下,图像像素点频率为:1280×1024×60=75MHz。

VGA是用于给显示器等模拟设备提供图像信号的模拟接口。它有RGB3个模拟信号分量以及行场同步信号,其中行场同步信号是符合TTL电平的脉冲信号。由于模拟的VGA信号中包含有场同步时间和行同步时间及消隐时间,因此当图像为1280×1024@60Hz的情况下,AD转换后像素点频率要比实际算出来的75MHz还高。这么高的采样率对于AD提出了很高的要求。因此采用Analog Device公司的芯片。AD芯片具有3路采样精度为8bit的通道,最高采样率为140MSPS,具有300M的模拟带宽,并且专门对计算机及工作站图像接口进行了优化,最高可满足对分辨率为1280×1024,刷新率为75Hz的视频进行采样。

由于AD的采样率比较高,相应的输出数据率很也高。在系统要求的最高情况下,象素点频率为108MHz,相应的数据率为324Mbit/s(RGB3个分量,每个分量8bit)。同时,由于采集的是图像数据,因此系统对行同步要求比较高,因为如果在某一行的图像数据中丢失了某一个或多个点的数据,整个图像就会产生倾斜,如图1所示。图a为正确采集后得图像,没有发生倾斜;图b为行采集数据小于显示的水平分辨率;图c为行采集数据大于显示的水平分辨率。因此需要对每行的数据进行突发存储,保证数据不丢失。突发的长度为图像的水平分辨率。

从上面的分析可知,AD后数据的及时存储要求很高,在极端条件下系统必须以110MHz左右的频率进行突发长度为1280×3Byte的存储。传统的通过DSP把数据存储到SDRAM的方法不能满足这么高的速度和这么长的突发长度。因此我们采用FPGA直接控制SDRAM存储的方式进行。考虑到图像数据的频率和大小,我们采用工作在133MHz的SDRAM。

由于原始的图像数据量很大,需要占用比较大的存储空间,因此对采集到的图像数据还要进行后续处理。所以FPGA除了接收AD转换后的数据和控制SDRAM之外,还需要为图像的后续处理提供接口。

综上所述FPGA需要实现如下功能:同步接收AD采集的数据;读写SDRAM;提供后续图像处理接口;提供控制接口。

设计中采用Altera公司Cyclone系列的FPGA EP1C6。EP1C6具有2个锁相环,包含5980个逻辑单元,相当于12万门的规模,同时还包含了最高频率200MHz,92160bit的内部RAM。该芯片的频率和引脚IO等资源都能很好的满足本系统的要求。

总体设计

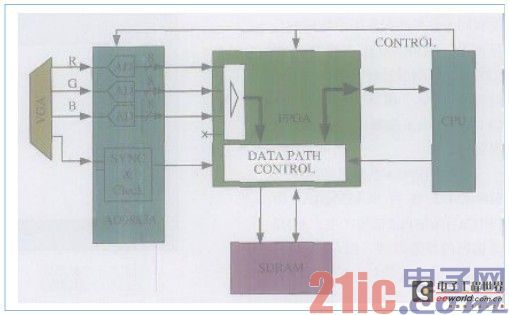

采集系统总体框图如图2所示。

[page]

[page]

采集系统由AD、FPGA、SDRAM和主CPU组成。整个系统由CPU控制。进行采集时,首先CPU根据行场同步信号判断图像的分辨率和刷新率,并对AD和FPGA进行相应的设置。其次,CPU使能FPGA进行采集。待采集一帧结束后,CPU即可对图像数据进行处理。

AD模块能够采集多种VGA图像格式,但却不能自动检测图像格式,必须通过它提供的IIC接口进行设置,我们在主CPU中实现对图像格式的自动检测,并对AD模块进行设置,另外,不同格式的VGA图像中场同步信号的有效脉冲电平没有统一,AD模块可以对输入的场同步信号极性进行自动检测并表示在内部寄存器中,通过读取该寄存器可以判断输入VGA信号场同步的极性。AD模块输出的场同步信号可以实现对输入场同步信号的反相。FPGA内部的同步逻辑只支持一种有效电平的场同步信号,因此在采集前需要通过读取AD内部的寄存器判断当前输入同步信号的极性,以确定是否需要设置AD芯片对场同步信号进行反相处理。

为了方便主CPU对FPGA的控制,FPGA提供了IIC接口。主CPU可以通过与AD模块一样的IIC接口控制FPGA。设置采集图像的大小,图像存储起始地址,消隐时间长短等信息,从而保证采集图像大小精确、完整,同时为了方便主CPU对图像进行后续的处理,FPGA把存储图像的SDRAM转换成ASRAM接口提供给CPU处理,从而把存储图像的空间直接映射到了CPU的寻址空间。CPU可以通过DMA快速的对图像数据进行读取和处理,提高系统效率。

FPGA内部设计

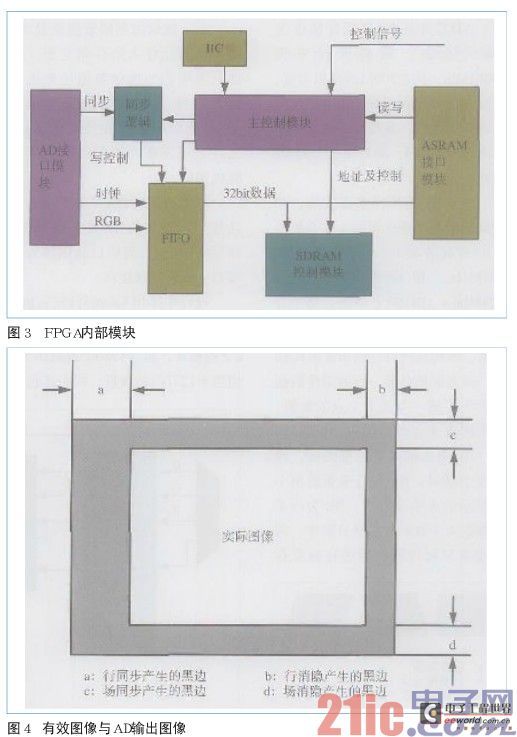

FPGA内部模块如图3所示。

FPGA内部由主控制、SDRAM控制器、AD接口、FIFO、ASRAM接口、IIC等模块组成。主控制模块负责接收CPU的控制信号和协调各个模块之间的工作,SDRAM控制模块实现对SDRAM的操作逻辑。AD接口模块接收AD模块输出的数据和同步信号并保证图像数据的行场同步,ASRAM接口模块转换CPU对ASRAM的操作为对SDRAM的操作指令,IIC逻辑模块接收CPU对FPGA采集系统的各种参数设置和控制。[page]

系统FPGA主要时钟频率有SDRAM工作频率133MHz,由EP1C6自带的PLL倍频产生;AD模块输出的像素时钟,由AD芯片内部PLL产生,IIC模块中的时钟,由CPU产生。其中AD芯片输出的时钟根据不同的输入图像格式有比较大的变动范围,从25-108MHz,而SDRAM的读写时钟固定为133MHz。因此在这两个不同频率的时钟之间必须加FIFO来同步,FIFO使用QuartusII软件中提供的免费IP核,通过使用FPGA内部高速RAM来实现。

AD模块负责与AD芯片的接口逻辑。前面已经分析了图像采集中同步的重要性,如果图像中的某一行数据不完整,那么将影响到整个图像。AD模块通过AD芯片输出的行场同步信号来实现图像数据的同步,以AD芯片输出点频作为FIFO模块的写时钟,行场同步信号的组合逻辑组成FIFO的写使能。另外,由于模拟的VGA接口存在有行、场同步时间和行、场消隐时间,为了保证图像采集的精度和完整,AD芯片要求把点频设置为比实际有效点频大20%-30%,因为在AD转换后的图像中行幅和场幅往往比实际图像大,造成图像有比较大的黑边。如图4所示。为了获得准确的图像数据,AD模块设置了计数器可以过滤图像起始的黑边。其计数值可以通过IIC接口进行设置。

SDRAM有多种不同长度的突发模式。在本设计中由于AD输出的频率最高接近110MHz,突发存储的长度比较长,为了能保证数据能够及时存储,工作频率为133MHz的SDRAM必须工作在整页突发的模式,以达到最高的数据吞吐率。

为了提高通用性,本设计中把SDRAM接口转换成ASRAM接口提供给主CPU,避免了SDRAM工作频率和CPU外部时钟不同时造成的SDRAM控制权切换的麻烦,提高对各种CPU的兼容性。ASRAM接口逻辑实现对CPU地址到SDRAM地址的映射及操作时序的转换。主控制模块产生相应的SDRAM控制指令,控制SDRAM读写。SDRAM的操作对于CPU来说是透明的。

该采集系统也可对4路8bit的AD通道进行采集,因为FPGA内部的AD逻辑模块提供了32bit的接口,VGA采集方式只用了其中24bit。采用4路8bit模式时只需把前端AD部分做一些调整。

实际应用

在中国船级社对船载航行数据记录仪的性能要求中,要求船载航行数据记录仪应能连接到欲记录其图像的雷达显示器的视频缓存输出,通过专用的雷达缓存输出接口,数据记录仪需记录一系列单个和整屏的视频帧。该要求设计的显示器的分辨率应在640×350到1280×1024之间,刷新率在60-85Hz之间。采用本设计可以完整实现该要求。

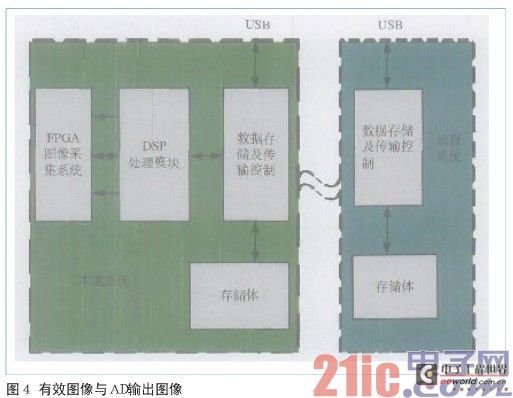

图5所示为完整的雷达图像记录系统框图。

总体上系统由本地端系统和远程系统两大部分组成。本地端负责对雷达图像的采集压缩和存储备份。远程系统保存雷达图像的副本。本地系统由采集、处理、存储传输3大部分组成。采集部分就是前文所述的以FPGA为核心的雷达图像采集系统。处理部分采用TI公司C6000系列DSP作为系统的CPU。存储传输部分主芯片则采用了Samsung公司的SOC芯片S3C2410。存储体则采用了多片大容量的NAND Flash。

远程系统与本地系统中的存储和传输部分一样。它只负责对雷达图像的存储。

本地系统和远程系统通过485或者以太网相互通信。同时,本地系统和远程系统都提供了USB接口。在计算机上可以通过USB接口读取设备中存储的图像,并对设备参数进行设置。

本文介绍的高速图像采集系统完整实现了预期的功能,能够对最高分辨率为1280×1024刷新率为60Hz的雷达图像进行采集,并通过ASRAM接口把图像数据提供给CPU进行后续处理。

该采集系统适用于嵌入式系统中,成功应用于船载雷达数据记录仪中,实现对雷达图像的采集,通过了实际测验。主要性能如下:采集图像分辨率从640×350到1280×1024可调,刷新率从60-85Hz可调,在15s采集一次的情况下可以保存24小时的雷达图像,并可以通过USB接口在计算机上重现雷达图像。

此外,本采集系统实现了对高速突发长度长的数据的采集,并提供了相对通用的控制和存取接口,使得该系统的应用不仅仅局限于雷达图像的采集。通过修改前端的AD模块,该系统还能同时对4路位宽为8bit,采样率最高位120MHz的AD通道进行数据采集,使它适用于其他需要高速采集的场合中。具有较强的通用性。

上一篇:CPLD在信号滤波和抗干扰中的应用

下一篇:可编程逻辑器件的应用参考

推荐阅读最新更新时间:2024-05-02 22:26

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号