引言

DS80C400评估板包括TINIm400参考电路板和TINIs400插座板,为评估TINI运行环境和利用DS80C400网络微控制器开发基于TINI的应用提供了一个优秀平台。TINIm400/TINIs400组合电路板的一个缺点是其通用IO (GPIO)引脚数有限。TINIs400插座板只包含几个可方便用作GPIO的引脚;插座板上的大多数IO引脚遍布在电路板上,并被用作其它功能(例如,J27为I2C引脚,J4为外部中断引脚)。

本应用笔记逐步演示了如何使用复杂可编程逻辑器件(CPLD)来配置硬件和开发软件,从而为TINIs400插座板额外提供32个GPIO引脚。

硬件设置

扩展TINI的IO性能的第一步是在TINIs400插座板上额外安装四个器件:CPLD、电源调节器,以及两个插头。Dallas Semiconductor公司售出的TINIs400插座板上没有安装这些器件,但为添加这些器件预留了焊盘和走线。板上并未安装这些器件,因为许多应用并不需要扩展IO性能,或者采用定制电路板设计。

TINIs400电路原理图1的第7页详细给出了扩展TINI IO性能所必需的器件。该电路使用了100引脚VQFP封装的Xilinx XC2C64 CoolRunner-II CPLD。

XC2C64和更大规模的XC2C128均已在TINI硬件平台上通过测试,该平台也支持相同引脚和相同封装的其他规模的器件。 与CPLD相关的插头有三个,其中两个是必需安装的,具体说明如下:

J30 JTAG编程连接器。通过JTAG接口对XC2C64 CPLD编程。J30连接器为JTAG信号TMS、TCK、TDI和TDO提供引脚。更详细的讨论见下文的CPLD编程一节。

J28扩展IO连接器。通过该连接器可访问XC2C64器件的32个引脚。对CPLD编程将为这些引脚提供读/写接口。

J29额外IO连接器。该连接器提供与XC2C64的16个额外连接,本设计中未用到这些连接器。

除J30和J28插头以外,还需要安装以下器件:

U2 MAX1792EUA18调节器

U12 Xilinx CPLD

电容C40至C57。这些电容仅在使用CPLD时才需要,从Dallas Semiconductor获得的TINIs400插座板应该已安装了这些电容。如果安装位置不正确或缺失,在进行其它TINI开发时也许不会注意到。

CPLD配置

CPLD是可编程逻辑器件。可将它看作是可编程硬件,具有非常灵活的内部逻辑,允许通过简单再编程实现很多功能。用CPLD可以实现32位触发器,以存储CPLD输出引脚的逻辑电平。用Verilog,一种硬件描述语言(HDL)来描述CPLD要实现的功能。Xilinx提供的工具可将Verilog源代码转换成二进制形式,用来配置CPLD。

在TINIs400电路板上,XC2C64与TINI微控制器DS80C400的存储器总线连接。这种连接允许TINI程序通过读、写特定地址访问CPLD。所以,当地址线选择CPLD时,必须对CPLD编程以正确响应;CPLD必须锁存写入的数据总线信号,并且当读CPLD时必须驱动端口输入。

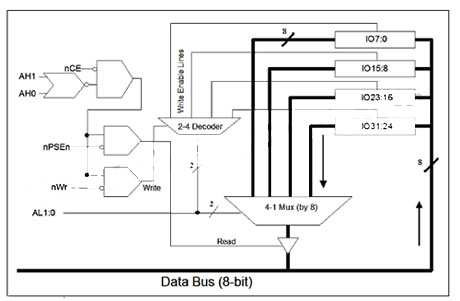

图1. CPLD功能框图 |

图1为CPLD需要实现的功能方框图。图中右上部的模块(IO7:0、IO15:8、IO23:16、IO31:24)代表存储输出电平值的触发器。这些8位寄存器组每一个均连接到数据总线。当通过适当的地址线和写选通信号(nWr)使能时,数据总线上的内容被锁存到寄存器内。检测IO引脚的输入电平并送入4:1多路复用器,此时低位地址选择8位值并传递到数据总线。如果CPU请求读(由地址线和nPSEN信号使能),则使能多路复用器的输出并驱动数据总线。

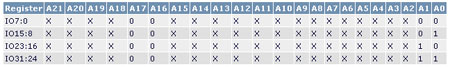

尽管10条地址线(不包括芯片使能)与CPLD连接,但本示例应用只使用其中四条。A17:A16高地址线配合芯片使能6一起使用。当地址位A17:A16为低且nCE6有效(低电平)时,选择CPLD,但CPLD在读或写信号有效之前不起作用。其它两个地址位A1:A0,用来选择四个8位寄存器当中的一个作为写操作的目标地址或读操作的源地址。这一地址方案意味着许多地址都可使能对四个8位寄存器的访问。表1概括了这种地址方案的灵活性。

表1. 能够激活CPLD寄存器的地址线取值

|

由于TINI库和工作固件将DS80C400配置为每个芯片使能端对应2MB空间,并且DS80C400的地址范围是24位(16MB),所以八个芯片使能端对应地址的高3位。为激活芯片使能6,24位地址的高3位必须为110b。

尽管表1说明多个地址均可激活寄存器,我们仅使用了以下寄存器地址:

地址C00000h IO7:0

地址C00001h IO15:8

地址C00002h IO23:16

地址C00003h IO31:24

Verilog编码

有六个Verilog文件用来实现CPLD的32位GPIO功能。本应用笔记的源代码中包含了这些文件,并附带提供Xilinx WebPACK(参见下文的讨论)工程文件。本工程的Verilog源文件包括:

Buffer8.v:8位缓冲器,用来连接TINI到四个8位寄存器的数据总线。

Mux2x8.v:2:1多路复用器,用来选择两条8位总线中的一条。

OneO4e.v:2-4译码器,输出一个取决于低地址位的有效信号。

Reg8OD.v:8位伪开漏极触发器阵列,用来存储输出值。

TSBuffer8.v:8位三态缓冲器,用来驱动数据总线输入值。

CPLD.v:模块间的顶层连接。

最应引起注意的Verilog源文件是CPLD.v。它包含输入、输出和节点的定义,并且给出在其它文件中定义的实例化模块。该源文件也是提取写脉冲和读脉冲的地方:

assign Reset = ~nRstOut; // make a hi-active Reset

assign IOBank = ~nCE6 & ~|AH; // decode the I/O bank

assign ReadT = IOBank & ~nPSEn; // qualify Read strobe

assign WriteT = IOBank & ~nWr; // qualify Write strobe

然后将信号ReadT作为三态缓冲器的使能信号,使用检测到的输入值驱动DS80C400的数据总线:

// Tri-State data bus to TINI needs this buffer

TSBuffer8 U4(ReadT, DataToTINI, D);

信号WriteT送入四个8位寄存器组作为时钟信号。

// 4 8-bit pseudo-open-drain output drivers

Reg8Out U6(Reset, ~WriteT, Enable[0], DataFromTINI, UIO[ 7: 0]);

Reg8Out U7(Reset, ~WriteT, Enable[1], DataFromTINI, UIO[15: 8]);

Reg8Out U8(Reset, ~WriteT, Enable[2], DataFromTINI, UIO[23:16]);

Reg8Out U9(Reset, ~WriteT, Enable[3], DataFromTINI, UIO[31:24]);

另一个重要的源文件(虽然不是Verilog文件)是CPLD.ucf。该文件给出了CPLD.v中声明的信号名称和XC2C64器件实际引脚之间的映射关系。地址线和几个IO引脚的定义如下:

NET "AL<1>" LOC = "P30";

NET "AL<0>" LOC = "P32";

NET "AH<1>" LOC = "P37";

NET "AH<0>" LOC = "P39";

NET "UIO<5>" LOC = "P43";

NET "UIO<6>" LOC = "P49";

NET "UIO<7>" LOC = "P50";

NET "UIO<8>" LOC = "P52";

NET "UIO<9>" LOC = "P53";

注意,这些引脚定义直接来自TINIs400电路原理图的第7页。例如,从电路图可以看出:地址线3-0 (A[3:0])连接到引脚28、29、30和32。如以上清单所示,我们定义了两条最低地址线信号(AL<1>和AL<0>),它们被映射至CPLD的引脚30和32。

CPLD编程

用于CPLD编程的工程文件包含在本应用笔记的源代码CPLD目录内。可以使用Xilinx的免费Webpack工具来构建并编程CPLD。本应用笔记中的应用实例是用6.3.03i版本开发的。只要支持CoolRunner 2 CPLD系列,Xilinx工具的最新版本应该也适合本设计。

硬件连接

我们使用Avnet Avenue JTAG编程电缆来连接计算机的并口和CPLD的JTAG引脚。许多CPLD或FPGA评估套件均提供JTAG编程电缆。本文使用的编程电缆如图2所示。

图2. Avnet Avenue JTAG编程电缆 |

图3为编程电缆和TINIs400插座板之间所需的连接。对信号做了标记,因此也可以用其他编程电缆。TINIs400插座板要求VCC为3.3V。

图3. JTAG编程器与TINIS400插座板的连接关系。J30上未标注的引脚没有连接。 |

载入工程时,点击File菜单并选择Open Project。浏览本应用笔记的源文件并选择parallel32.npl。现在已经打开工程并准备构建。接下来说明如何配置一个全新的工程。也可以跳过这一节,直接浏览后面的部分了解如何编程CPLD。

遵照以下指导说明,根据应用笔记提供的源代码创建一个新工程。

在File菜单中选择New Project。

选择想要创建新工程的目录,输入工程名称。将创建一个以工程名称命名的新目录。确保Top Level Module Type为HDL。点击Next继续。

在接下来的菜单中选择工程需要的器件和封装。器件系列选择CoolRunner 2 CPLDs。然后从给出的列表中选择器件——可以是XC2C64、XC2C128或其它同类器件。封装选择VQ100,这是TINIs400插座板认定的封装。本应用笔记中用到的其它配置选项参见图4。完成配置后,点击Next继续。

图4. 配置新工程的器件和设计流程 |

下一个窗口询问新工程中要创建的所有新文件。由于已提供了所有源文件,因此点击Next,不增加任何新文件。

接下来的窗口要求添加任何现有的源文件。点击Add Source按钮添加源代码提供的所有Verilog文件(文件列表见上文的Verilog编码一节)和CPLD.ucf文件。一旦添加后,程序会询问:File.v is which source type The suffix is ambiguous as to type (File.v是什么文件类型,后缀类型不明确)。选择Verilog Design File并点击OK (参见图5)。所有输入文件归类完毕后,点击Next继续。

图5. 确定输入源文件的文件类型 |

接下来的窗口概括了新工程的基本信息。查看一遍信息并点击Finish。

只要在上面第5步中添加了UCF文件,程序将要求把该文件关联到其影响的内容。在列表中选择CPLD并点击OK。

至此,完成了工程创建和配置。现在可以编辑、构建及综合您的设计。

器件编程

按照以下指导说明来综合CPLD工程,并对XC2C64器件编程。确保编程电缆已按上文硬件连接一节中说明的方法连接完毕。

CPLD编程:

在Project View (一般在窗口左上部)中选择Module View标签。在Module View中选择主文件CPLD.v。

在Process View窗口(一般在Project View窗口下部)中,展开Implement Design分支并双击Generate Programming File。这将运行把Verilog源代码转换成二进制文件(用于编程CPLD)需要的所有进程。运行进程时,进程左侧将出现说明执行结果的标记。绿勾标志意味着进程成功结束,没有错误或警告。黄色惊叹号意味着进程成功结束,但有警告信息。红色X号意味着进程没有成功结束,出现了错误。

一旦程序结束并且成功生成编程文件,双击Configure Device (IMPACT)。

将出现一个窗口,显示Configure Devices。选择Boundary Scan Mode选项并点击Next。

在接下来的窗口(Boundary-Scan Mode Selection)中选择Automatically connect to cable and identify Boundary Scan chain,并点击Finish。

如果器件连接正确,iMPACT将弹出一个窗口,显示“There was one device detected in the boundary-scan chain. iMPACT will now direct you to associate a programming or BSDL file with this device....”。点击OK。

应该在当前的工程目录下打开一个文件对话窗口(如果没有在该目录下打开,应查到其正确位置)。在该窗口中双击选择CPLD.jed。

右键单击Xilinx芯片图并选择Program。

确保选中Erase Before Programming and Verify,并且不要选其它项。点击OK。

此时将出现编程状态进度条,几秒钟(少于20秒)后编程结束,CPLD配置完毕。

进行自己的CPLD功能设计时,当DS80C400不和CPLD通信时,应确保CPLD代码释放地址、控制和数据信号为高阻抗状态。忽略这一点是很常见的错误,这会导致奇怪的故障现象,例如电路板会被保持在复位状态或发生随机性重启。发生此类问题时,只要擦除CPLD即可阻止该问题。

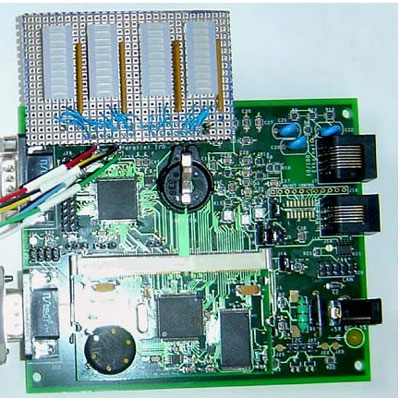

调试电路板

简单地借助32个LED,即可以演示TINI的IO扩展性能。该演示板用四组LED和四个电阻排来指示每个CPLD IO引脚的状态。LED板(安装在TINIs400上)如图6所示。

图6. 装有调试IO板的TINIs400/TINIm400 |

该简易电路板的原理图包含在本应用笔记的源代码中。注意,其中的电阻值是建议值;阻值太高会导致显示较暗,阻值太低会消耗太多TINI电源电流,并中止执行过程。

软件接口

这一简单的存储器接口实现后,软件访问扩展的IO引脚变得相当简单,将采用汇编语言来实现(作为原生函数嵌入Java应用中)。

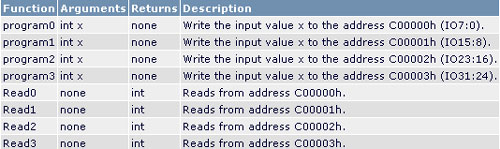

表2给出了为实现接口功能而定义的Java原生函数。

表2. TINI-CPLD接口使用的Java函数

|

注意,也可以用两个函数完成同样的工作:program(int address, int x)和read(int address)。但是,在本应用中选择每个地址分配一个函数,这样允许应用提取不同的地址作为功能寄存器。每个程序的汇编程序代码和读函数都相当简单。代码只要求以正确的地址载入数据指针,然后用一个movx指令激活存储器总线。

Native_program0:

clr a ; request first parameter

lcall NatLib_LoadPrimitive ; load parameter into r3:r0

mov dptr, #0C00000h ; point to memory mapped peripheral

mov a, r0 ; move low byte of source into accumulator

movx @dptr, a ; write to memory mapped peripheral

clr a ; indicate no error condition

ret ;

...

Native_read0:

mov dptr, #0C00000h ; point to memory mapped peripheral

movx a, @dptr ; read from memory mapped peripheral

mov r0, a ; move into low byte of result

clr a ; indicate no error condition

mov r1, a ; unsigned extend to 32-bits

mov r2, a ; unsigned extend to 32-bits

mov r3, a ; unsigned extend to 32-bits

ret ;

应用实例

应用实例在源代码的javacode文件夹中。该应用向四组LED写入递增值。该数值每500ms更新一次,因此可以很方便地知道应用是否正确运行。

由于该应用包括原生函数和Java代码,因此构建过程比纯粹的Java程序更为复杂。源代码中包含构建批处理文件,但要求针对您开发的系统做一些修改,具体说明如下:

c:\work\tini\tini1.16

ative\bin\win32\macro -Ic:\work\tini\tini1.16

ative\lib\ cpld.a51

改变目录以使其指向宏预编译处理器和本地库(native library)包含文件在您硬盘上的存储位置。这些项目是标准TINI SDK的一部分,可从ftp.dalsemi.com/pub/tini/index.html下载。

c:\work\tini\tini1.16

ative\bin\win32\a390 -f 1.16 -p 400 -l cpld.mpp

改变目录以使其指向a390汇编程序的地址。它们和宏预编译处理器存储在相同的目录中。

del *.class

从当前目录中删除先前存在的类。

javac -bootclasspath C:\work\tini\tini1.16\bin\tiniclasses.jar demo.java

不考虑TINI类文件,构建源文件demo.java。改变目录以指向TINI的API类,它是TINI SDK的一部分。

java -classpath C:\work\tini\tini1.16\bin\tini.jar;%classpath% TINIConvertor -n cpld.tlib -f . -o demo.tini -d C:\work\tini\tini1.16\bin\tini.db

组合本地库构建TINI可执行文件,实现与CPLD的接口。Java代码只需要调用该函数。

System.loadLibrary("cpld.tlib")

为了访问CPLD的扩展IO引脚,需要再次改变目录以使其指向TINI SDK附带的tini.jar工具文件和tini.db类数据库。

结束语

TINI和CPLD的结合提供了一种简单接口,可扩展IO性能,并具有高度灵活性。然而,使用可编程逻辑器件时其功能并不仅限于扩展IO。CPLD可用来实现许多逻辑功能和状态机。与TINI网络栈、Java虚拟机和操作系统结合使用,CPLD可使TINI系统具有高度可配置性和灵活性。

上一篇:基于ADSP-TS201S的图像采集处理系统

下一篇:基于ADSP-TS201S的图像采集处理系统

推荐阅读最新更新时间:2024-05-02 20:25

- 热门资源推荐

- 热门放大器推荐

-

人工智能算法(卷2)-受大自然启发的算法

人工智能算法(卷2)-受大自然启发的算法 -

电子电路——从入门到精通.pdf

电子电路——从入门到精通.pdf -

深入理解并行编程V2.0

深入理解并行编程V2.0 -

开关电源技术(电气自动化新技术丛书) 杨旭等 .pdf

开关电源技术(电气自动化新技术丛书) 杨旭等 .pdf

An error occurred.

Sorry, the page you are looking for is currently unavailable.

Please try again later.

If you are the system administrator of this resource then you should check the error log for details.

Faithfully yours, OpenResty.

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

人工智能算法(卷2)-受大自然启发的算法

人工智能算法(卷2)-受大自然启发的算法

京公网安备 11010802033920号

京公网安备 11010802033920号