在DVB-C系统当中,实际信道中的突发错误往往是由脉冲干扰、多径衰落引起的,在统计上是相关的,所以一旦出现不能纠正的错误时,这种错误将连续存在。因此在DVB-C系统里,采用了卷积交织来解决这种问题。它以一定规律扰乱源符号数据的时间顺序,使其相关性减弱,然后将其送入信道,解交织器按相反规律恢复出源符号数据。

DVB-C的卷积交织和解交织原理为:交织由I=12(I为交织深度)个分支构成。每个分支的延时逐渐递增,递增的单元数M=n/I=204/12=17(M为交织基数)。这里的数据单位为字节。0支路无延时,1支路延时17个符号周期,11支路则延时l7×11个符号周期。输入端有一开关随着时间推移依次连接各个延时支路,输出端有一开关与输入端一一对应,同步连接各延时支路。

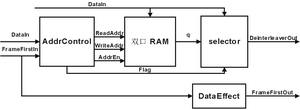

图1 解交织器的实现框图

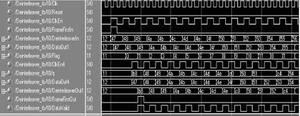

图2 解交织器的Modelsim仿真图

解交织器的实现

解交织器的FPGA实现原理

本文采用RAM分区循环移位法来实现,因为RAM里面暂存一位数据,只需要用一个逻辑门大小的资源,比基本寄存器暂存一位数据需要12个逻辑门大小的资源要优化很多。用RAM分区循环移位法来实现解交织器,就是把RAM分成11个区。每个区的大小为(单位为字节):

Ni=M*(I-i-1)(i=0,1,2, …,(I-1))

这里i为RAM所分区的区号。

因为11支路不需要延时,所以 RAM的11分区大小即N11为0。本文在RAM前面设置一个地址控制器,这是解交织器关键的一步。RAM每区有一个首地址和区内偏移地址,分别用一个寄存器来存储。在地址控制器里产生每区的首地址和区内偏移地址,从而进一步产生RAM的读写地址。

解交织器的FPGA实现

把解交织器的深度I和基数M设成参数,以增强程序的通用性。如果以后设计的解交织器的系数I和M需要改动,只要把参数值重新设置一下就可以了,不需要改动程序。由前面的计算可知,解交织器总共需要延时的比特数,也就是RAM的大小应该为8976比特。

可以用下面一段程序实现首地址的初始化:

FirstAddr[0]=0;

for(i=1;i<(I-1);i=i+1)

FirstAddr[i]=(I-i)*M+FirstAddr[i-1];

也就是说0~11支路的首地址在RAM中分别为0,187,357,510,646,765,867,952,1020,1071,1105。

RAM每区的字节数可以由参数来表示,即为(I-i-1)*M,i为分支号。

每区内偏移地址SectAddr[i]初始化为0,每写入一个数据,递增1并与由参数表示的每区的字节数进行比较,若两数相等,则SectAddr[i]重新设为零,保证区内偏移地址在每区内循环移动。

由上可知,RAM每区的读写地址为:FirstAddr[i]+SectAddr[i](i为RAM分区号)

图1所示的就是由Altera MegaWizard工具配置的双口RAM。RAM每区的读写地址相同,也就是先读出给定地址单元的数据后,再写入新的数据。这里要同时发生读写操作,所以要使用双口RAM。每隔一个时钟周期,RAM读写指针就跳到下一个RAM区,这样读写指针在RAM的11个区循环移动,实现解交织。

图2为解交织器在Mentor公司的Modelsim SE环境下的逻辑仿真图。Clk为时钟信号,Reset为异步复位信号,ClkEn为时钟使能信号,高电平有效,FrameFirstIn为帧同步信号,高电平有效。DeinterleaverIn为输入数据。设计时要注意数据同步问题,要不然会造成数据错位,导致设计的失败。DeinterleaverIn为了在selector模块输入时和RAM的输出数据q保持同步,要作相应的延时,同步延时后DataIn4,同理,对应地RAM的输入数据DataIn1,selector模块的使能信号ClkEn4等也是经过同步处理得到。Flag为selector模块的选择控制信号,当Flag信号为0~10时,选择RAM的输出数据q作为输出,而当Flag=11时,则选择DeinterleaverIn经过同步处理后的数据DataIn4作为输出,从而保证在解交织器的11支路实现无延时输出。在解交织器的最前面输出的字节有些是无效的,加一个DataEffect模块是为了等全部字节都有效时,才把FrameFirstOut信号置高,告诉后面的模块数据开始全部有效。

从资源利用方面考虑,使用RAM分区循环移位法来实现DVB-C解交织器比全部用基本寄存器或用配置FIFO的方法来实现要优化得多。

为了更好地验证,本文把设计在synopsys 公司的synplify pro软件环境下进行综合,选用Altera公司的Cyclone EP1C12Q240C8器件。因为使用了软核IP,所以再把生成的*.vqm文件导入synopsys公司的QuartusII 软件进行再综合,选择同样的器件类型和型号,结果说明采用双口RAM设计所使用的逻辑单元较少,而且使用的8976比特RAM资源占用了Cyclone器件中的3个M4K,只有全部存储资源的3%。

结语

虽然采用卷积交织会在刚开始传输数据的时候输出一些无效数据,在系统中引入一定的延时,但是它能把突发干扰造成的突发错误分散成随机错误,利于RS纠错,这样一权衡,有延时也是很值得的。本文利用EDA工具完成解交织器的设计,并且采用Verilog和原理图协同输入的设计方法,大大提高了设计效率。这里设计的解交织器具有通用性,如果要用不同深度I和基数M的解交织器,只要重设程序里的参数值就可以了,非常方便。

上一篇:德州仪器推出业界最低成本的浮点 DSP

下一篇:基于现场可编程门阵列的数控延时器的设计

推荐阅读最新更新时间:2024-05-02 20:26

- 宁德时代巧克力换电生态大会将举行,什么是“巧克力换电”?1.5分钟换电能实现吗?

- 新型生物材料与高端医疗器械广东研究院、远诺技术转移中心加入面向初创企业的 MathWorks

- S5PV210 Linux字符驱动之PWM蜂鸣器驱动

- 尼得科机床新增可实现高效加工的高速主轴产品线

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Bourns推出全新高效能、超紧凑型气体放电管 (GDT) 浪涌保护解决方案

- S5PV210之UBOOT-2011.06启动过程解析

- 六个理由告诉您为什么应该将模拟无线麦克风更换为数字无线麦克风

- S5PV210启动过程分析

- 【已结束】力源直播【安森美 25KW 充电桩模块方案】(9:30入场)

- 有奖直播|Keysight World 2020【电信基础设施、云与人工智能分论坛】

- 免费试用eZ430-RF2500开发套件!

- 有奖直播|安森美全新 ADAS 电源 IC 提升 ADAS 系统的清晰度及安全性

- 【EEWORLD第三十五届】2012年02月社区明星人物揭晓!

- 【主题月活动】术业有专攻,电容我在行!

- 5G来袭 TE Connectivity 助你抢占消费电子市场先机

- 免费尝鲜:ST 双核无线 MCU STM32WB55 开发板

- ADI•世健工业嘉年华—有奖直播:ADI赋能工业4.0—助力PLC/DCS技术创新

电力工程设计手册 09 火力发电厂电气二次设计

电力工程设计手册 09 火力发电厂电气二次设计 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号