随着嵌入式技术的飞速发展,对嵌入式系统的应用需求也呈现出不断增长的态势,因此,嵌入式技术也相应地取得了重要的进展,系统设备不断向高速化、集成化、低功耗的方向发展。现场可编程门阵列FPGA经过近20年的发展,到目前已成为实现数字系统的主流平台之一。 FPGA具有单片机和DSP无法比拟的优势,相对于单片机和DSP工作需要依靠其上运行的软件进行,FPGA全部的控制逻辑是由延时更小的硬件来完成的。

通用串行总线(USB)是现代数据传输的发展趋势,是解决计算机与外设连接瓶颈的有效手段,USB2.O版本在原先的版本基础上实现许多技术上的飞跃与进步。USB2.0协议规范有以下主要优点:1)速度快,接口的传输速度高达480Mh/s,远大于PCI接口的132 Mb/s的传输速度;2)连接简单,所有的USB外设利用通用的电缆可简单方便地连入PC机中,安装过程高度自动化;3)支持多设备连接,USB接口支持多个不同设备采用“级联”方式来连接外设。

故为了将数据采集系统设计更加符合高速化和集成化的趋势,采用了FPGA和USB2.0组合的方案来进行。

1 数据采集系统的框架与硬件设计方案

系统硬件设计部分中,在完成系统时钟源、电源等必要电路的设计基础上,重点就是完成系统内各个部件的接口电路的设计,通过这部分的设计,基本的硬件平台就建立起来了。系统部件间的硬件电路接口设计如图1所示。

A/D芯片在此选用了德州仪器公司的10位串行接口芯片TLV1572,8管脚的SOIC封装,它外部较少的管脚不仅能够很方便地实现与其他器件连接,而且它体积小,可以节省很多布线资源,如图2所示。TLV1572的最高采样速率为1.25 MS/s,其积分非线性误差INL<±1LSB,可以采用3 V或5 V的供电方式。

由于大部分USB1.1的芯片都需要微控制器参与数据从端点FIFO到应用环境的转移,微控制器在里面扮演了搬运者的角色,那么显然微控制器本身的工作频率就极大地限制了数据传输带宽的进一步提高,微控制器将成为制约整个系统速度提高的瓶颈。

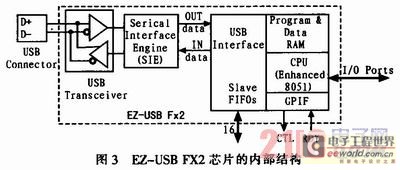

故在此选用的是Cypress Semiconductor公司的EZ-USBFX2(CY7C68013A)USB2.0芯片,它集成了USB2.0收发器,串行接口引擎SIE和可编程的外围接口。该芯片的另一大优点就是提供了一种独特架构,使USB接口和应用环境直接共享Slave FIFOs,微控制器无需参与数据传输,这样就极大地提高了系统数据传输速率,如图3所示。

由于FPGA的I/O管脚数目众多,它在和A/D芯片及USB2.0芯片相连时,能够按照优化布线资源的方式进行PCB布局设计,具体的连接方法在图1中已经给出。[page]

2 数据采集系统软件设计方案

FPGA软件设计方案中采用了自顶向下的设计方法,运用Verilog HDL语言来设计数字系统,分别完成数字系统内部各个子模块的设计。数据采集系统结构及模块间的连接示意图如图4所示。

由图4可见,系统主要由3个模块组成。它们分别是A/D接口adc.v模块、USB接口usb.v模块以及顶层top.v模块,其中在顶层top.v模块中,完成了对其他两个模块的调用,使它们拼接成为一个完整的系统。其中锁相环PLL_1和PLL_2分别给ade.v模块和usb.v模块提供时钟源。

2.1 FPGA控制A/D芯片接口的软件设计

在adc.v模块中,需要完成FPGA对TLV1572的接口逻辑代码的设计,其实质就是在TLV1572的时序分析的基础上来设计逻辑代码,使得FPGA能够按照其时序要求完成对A/D芯片的各种控制,包括提供给TLV1572的串行时钟信号信号ADC_CLK、CS片选信号ADC_CSn以及从TLV1572中读取出转换完成的串行数据S_DATA。

TLV1572的时序图如图5所示。

从时序图可见,A/D芯片的转化过程是在当CS为低电平后,由SCLK的上升沿发起的,输出的头六位二进制数字均为“0”,此时A/D芯片正处于采样阶段,数字无效,这六位无效的二进制数之后,A/D转换完成后的二进制数据在SCLK的上升沿被送到总线上,这时,作为系统主控制芯片的FPGA应当去采样总线上的数据,得到转换后的结果。

2.2 FPGA控制USB2.0芯片的软件设计

在usb.v模块中,需要完成FPGA对CY7C68013A的接口逻辑代码的设计和异步FIFO模块的设计。其中,对CY7C68013A的接口逻辑代码主要是完成对CY7C68013A芯片的端点FIFO的各种控制,包括16位的数据信号FIFO_DATA[15:0]、2位端点FIFO选择信号FIFO_ADDR[1:0]、端点FI-FO满标志位信号FIFO_Full、端点FIFO写使能信号FIFO_WR_en。因为adc.v模块和芯片外部的CY7C68013A工作在不同的时钟域内,故异步FIFO模块设计部分设计的目的除了是要完成从ade.v模块读取过来数据的缓冲,另外就是需要解决异步时钟域数据传输可能出现的亚稳态问题。

具体来说,FPGA在工作时需要不断向CY7C68013A的端点FIFO写入数据,而FPGA与CY7C68013A之间的工作模式属于同步方式,两者都由PLL _2模块提供40 MHz的时钟信号进行工作,那么它们之间的关系就是同步Slave FIFO的写操作,由FPGA向CYTC68013A中写入数据。

在Verilog HDL程序设计中,需要设计一个状态机来完成同步Slave FIFO写的时序,写时序如下;1)IDLE:当写事件发生时,进状态1;2)状态1:使FIFOADR[1:0]指向IN FIFO,进状态2;3)状态2:如果端点FIFO满,在当前状态等待,否则进状态3;4)状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK周期,进状态4;5)状态4:如需传输更多的数,进状态2,否则进入IDLE状态。

该状态转换的状态图如图6所示。

[page]

2.3 FPGA的顶层模块的设计由图4可知,top.v模块是FPGA整个系统的顶层模块,它通过顶层调用的方式把adc.v和usb.v两个模块组合成一个完整的系统,系统与外界进行通信是通过top.v这个模块对外的各个接口来实现的,具体到器件层面,就表现为由top.v文件定义的FPGA的相关的管脚来和A/D与USB2.0芯片进行数据的交换、控制信息以及时钟信号的传递。这种自顶向下的设计方法,不仅符合人的思维逻辑,也大大地简化了大规模逻辑电路的设计工作,使人们从繁琐的自底向上的底层设计中解放出来,以一种系统级的思维模式设计电路。这是自顶向下设计方法的巨大优势之一。顶层top.v模块是通过例化的方式来调用adc.v模块和usb.v模块的以及PLL模块。

2.4 USB2.0芯片的固件程序设计

在USB的体系中,无论是其本身的规范还是各种厂家所提供的芯片资料,关于主机对USB的检测都称之为枚举Enumeration(and ReNumer-ation),即枚举(与重新枚举)。固件在这发挥了无法替代的作用。应该说所有基于微控制器及其外围电路的功能设备的正常工作都离不开固件的参与,固件的作用就是辅助硬件,或者说是控制硬件来完成预期的设备功能。没有固件的参与和控制,硬件设备只是芯片的简单堆砌,无法实现预期的功能。

CY7C68013A内部集成了增强型的8051内核,它与8051指令集二进制是兼容的,那么就可以选择汇编或者高级语言C51来编写固件代码,两者各有优缺点,适用的环境也不同。本设计中采用C51来编写固件程序,关于开发C51语言的Keil μVision 2开发编译环境在此不再赘述。

Cypress公司为了简化和加速用户使用CY7C68013A芯片进行USB外设的开发过程,特别设计了一个完整的固件程序的框架。这个框架可以执行CY7C68013A芯片的初始化、USB标准设备请求的处理和USB挂起电源管理服务。用户只需要提供一个USB描述符表,添加其他端点接收和发送数据的通信代码,以及控制外围电路的程序代码。

在Keil μVision 2集成开发环境下,新建工程后,需要将工程代码复制到工程目录中并添加至工程列表中,开发固件程序需要几个重要的文件依次为:1)fw.c,框架程序的代码。2)periph.c,用户函数挂钩的相关定义,外围设备的控制文件。在上节中,主程序fw.c调用的TD_lnit()函数即在此定义出来。3)dscr.a51,USB描述符表,上节中关于描述符的定义在这个文件中给出。4)EZUSB.lib,EZ-USB函数库目标代码。5)USBJmpTb.OBJ,EZ-USB中断向量和跳转表。6)FX2.h,程序运行所需要的一些宏定义。7)fx2regs.h,CY7C68013A相关的寄存器定义及位屏蔽的宏定义。8)syncdly.h,定义了若干延时函数供程序调用。

3 Modelsim环境下仿真与结果

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言的仿真软件,该软件可以用来实现对设计的VBDL、Verilog HDL或是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

目前需要对adc.v模块进行功能仿真,以此验证该模块的功能的正确性。仿真测试的方法就是给adc.v这个模块的s_data数据输入端,即A/D芯片的串行数据的输出端,加载一组测试数据,每16个为一组测试数据,模拟在真实环境下从A/D芯片读取出来的二进制数据,然后在adc.v模块的输出端,即并行的16位宽的data_out端口观察是否与给定的测试数据相一致。假如一致,则模块的功能是正确的。假如有个别位的数据不一致,则需要检查模块的代码是否存在问题。在编辑器中编写Testbench程序如下(非关键的程序限于篇幅,就省略了):

[page]

由上面的程序可以看见,给s_data端加载的一组16位二进制数据为“0000-0011_0110_1011”。在ModelSim环境下,将待测试的文件与该测试文件放在同一个工程下,设置好相关参数后运行仿真可以得到如下仿真波形,如图7所示。

由图7可见,从data_out这个并行的数据端口读出的数据正是在Testbench仿真测试文件中给定的那一组测试数据,仿真得到的结果是正确的。

4 数据采集系统的实验

在FPGA控制A/D芯片接口的软件设计中,是通过FPGA内部的逻辑电路实现了分频,并将分频后的信号作为A/D芯片工作的采样时钟,经过测试,得知A/D芯片的采样频率为1.08 MHz,通过信号发生器,将输入的模拟信号设为10 kHz、幅度为3 V的正弦波,采样转换后的数据上传到上位机中,显示的波形如图8所示。

在同等条件下,把输入的模拟信号的频率调整为5 kHz。A/D芯片的采样频率仍然为1.08 MHz。得到的显示波形如图9所示。

由图8和图9可知,在对模拟信号采样时,当采样率不变时,输入模拟信号的频率越低,相对地就提高了采样点、减小了采样间隔,在图形中就越能体现出原始模拟信号的信息,得到的波形就更加的理想。

5 结束语

本文在研究了FPGA和USB2.0技术的基础上,提出了数据采集系统的总体设计方案,以FPGA和USB2.0为技术核心,设计了硬件电路和软件代码并在ModelSim环境下通过了仿真测试。该系统不仅能够实现一般用途的数据采集,还实现了系统的高速化、集成化和低功耗工作,为便携化数据采集系统提供了一种设计思路。

上一篇:DDR测试技术与工具

下一篇:一种高速数据采集卡的设计与实现

推荐阅读最新更新时间:2024-03-30 22:14

- 有奖直播:ADI数字主动降噪耳机方案 8月6日上午10:00-11:30 邀您聆听让技术为我们静下来

- 有奖直播【如何在几分钟之内完成高效可靠的USB PD电源设计——PI Expert™分步教程】(9:30开始入场)

- 罗姆有奖直播|可应用于LiDAR的激光二极管及周边电源推荐

- ADI有奖下载活动之14 ADI公司针对pH计和电导率仪的演示系统

- 仲夏狂欢,TI 博文学习季再度热力来袭!

- Digi-key干货视频教程来袭,意见领袖讲解疑难设计问题,带你突破成长瓶颈~

- TI原装MSP430 LaunchPad千人大团购!

- 【看电源研讨会 抽好礼】 高密度电源系统的PCB布局与散热设计系统

- 我与BeagleBone 有个约会!

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号