封装技术的进步推动了三维(3D)集成系统的发展。3D集成系统可能对基于标准封装集成技术系统的性能、电源、功能密度和外形尺寸带来显著改善。虽然这些高度集成系统的设计和测试要求仍在不断变化,但很显然先进的测试自动化将对推动3D集成系统的量产产生重要影响。本文将讨论3D集成系统相关的一些主要测试挑战,以及如何通过Synopsys的合成测试解决方案迅速应对这些挑战。

2.5D集成和3D集成

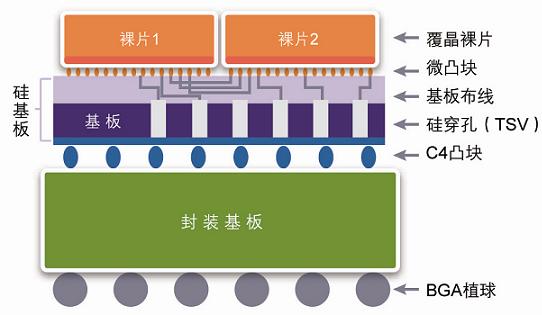

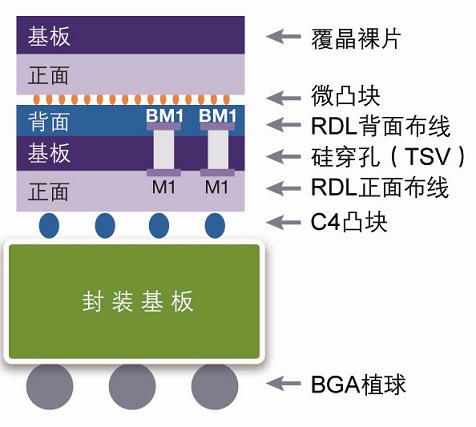

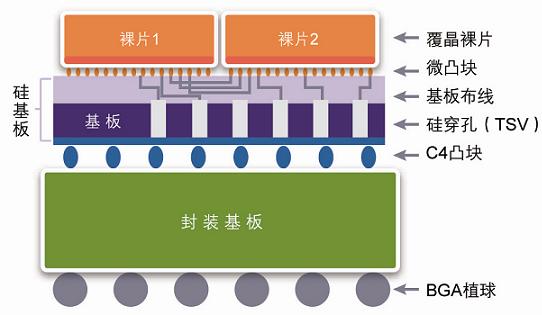

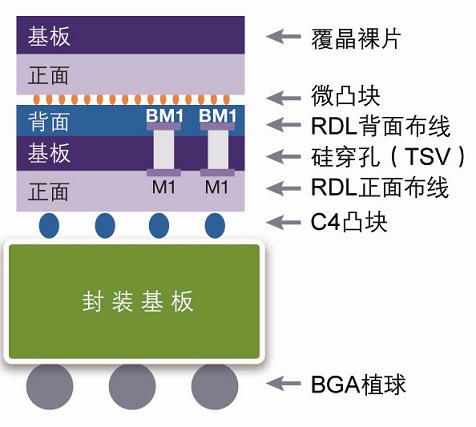

目前有两种基本的3D封装配置。2.5D集成系统在一个普通电气接口(称为硅基板)上挂接多块二维(2D)裸片,并通过穿过基板的导线把这些裸片连接在一起(如图1所示)。系统I/O通过中途延伸穿过基板的垂直硅穿孔(TSV)连接到底层封装基板。由三维堆叠IC(3D-SIC)组成的系统(如图2所示)的外形尺寸比2.5D集成系统更紧凑。在这种配置中,TSV蚀刻在基板中,由2D IC组成的晶片最小厚度不到50微米。多块裸片垂直堆叠并通过TSV进行互连。

图1:2.5D集成(两块裸片通过穿过硅基板的导线进行互连)。

图2:3D-SIC(两块堆叠裸片通过TSV进行互连)。

对堆叠配置进行测试需要2.5D封装测试所需的自动化的超集,因此在以下章节中我们将重点讨论这一话题。

对3D堆叠IC进行测试

图3显示了由三片裸片堆叠的3D-SIC众多可能测试方法中两种方法的测试场景。一种方法是在所有裸片粘接在一起之后进行堆叠测试,如场景1所示。堆叠测试从底部(第一块)裸片与第二块裸片之间,以及第二块裸片与第三块裸片之间的TSV互连测试开始,然后从底部裸片开始按顺序对每块裸片进行测试。此外,堆叠测试同时还可包括把整个堆叠作为一个集成系统进行测试。

图3:对某个三裸片堆叠进行3D-SIC测试场景举例。在场景1中,只有在所有三块裸片粘接完成之后才进行堆叠测试。在场景2中,每当有一块已知合格裸片粘接到堆叠顶部时都要进行一次堆叠测试。

由于对后续发现存在缺陷的裸片进行“拆除(un-bond)”不太可行,因此在粘接之前对单个IC在粘接过程中的互联可能造成的损失测试可能比仅依赖堆叠测试来识别已造成整个系统缺陷的缺陷裸片更加具有成本效益。在图3的场景2中,每当有一块KGD粘接到IC堆叠顶部时都要进行一次堆叠测试,以便排查对顶部两块裸片以及在粘接过程中的互联可能造成的损失。[page]

分辨合格裸片测试

尽管把KGD测试纳入3D-SIC测试流程有可能降低总的制造和测试成本,但会带来新的挑战。除底部裸片以外,没有可用于KGD测试的任何探针压焊点,因为所有的I/O都只可通过TSV(顶部有细间距的微凸块,排列在裸片的两侧)接入。业界正在努力建设摆脱这些约束的探针系统,但在新系统可投入生产之前,设计者必须考虑能够利用其现有自动化测试设备(ATE)基础设施的其它方法。一种可行的方法是插入KGD测试专用的“牺牲的(sacrificial)”探针压焊点。虽然存在由于专用探针压焊点而引起的面积损失,但还是可以通过使用DFTMAX压缩中的有限引脚测试功能尽量减少压焊点的数量。有限引脚测试最多可缩短测试应用时间和测试数据量170X,只需要使用一对测试数据引脚。

此外,由于3D-SIC中的故障影响与2D设计中的故障影响完全相同,所以在建立KGD测试模型时仍然可以使用传统的故障模型。但是,由于3D集成系统的外形尺寸比传统设计更小,性能更高,所以高质量的KGD测试可能需要使用TetraMAX ATPG中提供的更高级的测试——比如,针对微小时延缺陷的信号跳变延迟测试和针对桥接故障的桥接测试。

尽管如此,单靠扫描测试并不够。用于连接相邻裸片的TSV数量有数千个,如果没有能够满足3D-SIC细间距要求的探针技术,那么在KGD测试过程中这些TSV的故障是无法观测的。设计者可通过为所有的TSV I/O使用双向I/O包装器单元(wrapper cell)来克服该障碍。TetraMAX可按照双向引脚形式为I/O建立模型,然后生成允许在TSV I/O中应用和捕获数据的TSV“回路”测试,验证其功能。

缺陷驱动型嵌入式存储器自测试是KGD测试的另一个重要组成部分。3D集成系统的设计者可通过Synopsys的DesignWare自测试和修复(STAR)存储器系统为Synopsys和第三方存储器实现最高的缺陷覆盖率。

电源测试注意事项

3D-SIC系统复杂度越高,对动态功耗的控制要求就越高。功耗在裸片粘接到堆叠前后是不同的(因为裸片粘接后TSV为堆叠分配电源)。需要使用功率感知(power-aware)ATPG和基于电源域测试等先进的电源管理技术来限制功耗,从而最大程度地减少3D-SIC测试过程中的误报故障。功率感知ATPG、DFTMAX和TetraMAX协同工作可生成能够把Shift模式和capture模式功耗限制在功能水平(基于设计者指定的开关转换预算)范围以内的模型。

通过基于电源域测试,TetraMAX能够生成符合设计功能电源状态要求的模型,降低动态功率和泄露功率,并尽量减少IR压降问题的发生。此外,它还可通过生成用于测试电源管理电路的模型序列进一步提高缺陷覆盖率。Synopsys的高级电源管理功能已成功部署到2D设计中,以提高缺陷覆盖率和限制ATE上的误报故障。这些高级电源管理功能将在3D-SIC测试中发挥重要作用。

堆叠测试

TetraMAX生成KGD模型后,把KGD模型映射到堆叠级端口是一个简单的过程。对于TSV互连测试,TetraMAX使用动态桥接故障模型生成针对TSV I/O之间时序的全速测试模型。但堆叠测试的主要挑战是设计和实现能够向非底部裸片提供足够测试接口的3D DFT架构,以便进行单独裸片测试,裸片间测试(即TSV互连测试)和可能的多裸片同时测试。Synopsys正积极参与IEEE P1838等新兴3D测试标准的开发。虽然这些标准尚未整合使用,但早期采用者可使用Synopsys的合成测试解决方案来高效地实现基于已确立标准的3D DFT架构。

例如,DFTMAX可为使用IEEE Std 1149.1作为测试接入机制的3D-SIC系统合成、连接和验证JTAG测试接入端口(TAP)和边界扫描寄存器(BSR)逻辑,以便进行KGD或堆叠测试。

此外,DFTMAX还使用IEEE Std 1500标准进行芯核包装和“裸片包装”——当非底部裸片的测试控制接口使用基于IEEE Std 1500标准的包装器时。同样,位于底部裸片并通过JTAG TAP接收指令的DesignWare STAR存储器系统可使用IEEE Std 1500接口为堆叠中所有其它裸片的嵌入式存储器提供必要的测试接入和隔离。

在每块裸片上实现测试接口后,测试接口采用菊花链方式在堆叠内上下互连,实现对逻辑搭载逻辑(logic-on-logic)和逻辑搭载存储器(memory-on-logic)配置的堆叠测试,如图4所示。

图4:Synopsys支持对基于已确立测试接入标准的逻辑搭载逻辑(LoL)和逻辑搭载存储器(MoL)系统进行3D-SIC测试。

能够通过JTAG TAP访问3D-SIC中的嵌入式测试和调试资源的另一个功能是DesignWare SERDES IP(UPx)。Synopsys的高速接口自测试似乎兼容新兴的IEEE Std P1687标准(推荐的仪器使用标准),并且是对3D-SIC产品成功认证和部署起到关键作用的器件接入机制的一个典型类型。除了上述标准以外,Synopsys的测试解决方案使用STIL(IEEE Std 1450.x)和CTL(IEEE Std 1450.6)作为主流接口连接到电子设计和制造行业中的其它系统,并且作为对2.5D和3D封装配置同时进行测试的手段。

关键字:电阻网络 测试方法

引用地址:3D集成系统的测试自动化

2.5D集成和3D集成

目前有两种基本的3D封装配置。2.5D集成系统在一个普通电气接口(称为硅基板)上挂接多块二维(2D)裸片,并通过穿过基板的导线把这些裸片连接在一起(如图1所示)。系统I/O通过中途延伸穿过基板的垂直硅穿孔(TSV)连接到底层封装基板。由三维堆叠IC(3D-SIC)组成的系统(如图2所示)的外形尺寸比2.5D集成系统更紧凑。在这种配置中,TSV蚀刻在基板中,由2D IC组成的晶片最小厚度不到50微米。多块裸片垂直堆叠并通过TSV进行互连。

图1:2.5D集成(两块裸片通过穿过硅基板的导线进行互连)。

图2:3D-SIC(两块堆叠裸片通过TSV进行互连)。

对堆叠配置进行测试需要2.5D封装测试所需的自动化的超集,因此在以下章节中我们将重点讨论这一话题。

对3D堆叠IC进行测试

图3显示了由三片裸片堆叠的3D-SIC众多可能测试方法中两种方法的测试场景。一种方法是在所有裸片粘接在一起之后进行堆叠测试,如场景1所示。堆叠测试从底部(第一块)裸片与第二块裸片之间,以及第二块裸片与第三块裸片之间的TSV互连测试开始,然后从底部裸片开始按顺序对每块裸片进行测试。此外,堆叠测试同时还可包括把整个堆叠作为一个集成系统进行测试。

图3:对某个三裸片堆叠进行3D-SIC测试场景举例。在场景1中,只有在所有三块裸片粘接完成之后才进行堆叠测试。在场景2中,每当有一块已知合格裸片粘接到堆叠顶部时都要进行一次堆叠测试。

由于对后续发现存在缺陷的裸片进行“拆除(un-bond)”不太可行,因此在粘接之前对单个IC在粘接过程中的互联可能造成的损失测试可能比仅依赖堆叠测试来识别已造成整个系统缺陷的缺陷裸片更加具有成本效益。在图3的场景2中,每当有一块KGD粘接到IC堆叠顶部时都要进行一次堆叠测试,以便排查对顶部两块裸片以及在粘接过程中的互联可能造成的损失。[page]

分辨合格裸片测试

尽管把KGD测试纳入3D-SIC测试流程有可能降低总的制造和测试成本,但会带来新的挑战。除底部裸片以外,没有可用于KGD测试的任何探针压焊点,因为所有的I/O都只可通过TSV(顶部有细间距的微凸块,排列在裸片的两侧)接入。业界正在努力建设摆脱这些约束的探针系统,但在新系统可投入生产之前,设计者必须考虑能够利用其现有自动化测试设备(ATE)基础设施的其它方法。一种可行的方法是插入KGD测试专用的“牺牲的(sacrificial)”探针压焊点。虽然存在由于专用探针压焊点而引起的面积损失,但还是可以通过使用DFTMAX压缩中的有限引脚测试功能尽量减少压焊点的数量。有限引脚测试最多可缩短测试应用时间和测试数据量170X,只需要使用一对测试数据引脚。

此外,由于3D-SIC中的故障影响与2D设计中的故障影响完全相同,所以在建立KGD测试模型时仍然可以使用传统的故障模型。但是,由于3D集成系统的外形尺寸比传统设计更小,性能更高,所以高质量的KGD测试可能需要使用TetraMAX ATPG中提供的更高级的测试——比如,针对微小时延缺陷的信号跳变延迟测试和针对桥接故障的桥接测试。

尽管如此,单靠扫描测试并不够。用于连接相邻裸片的TSV数量有数千个,如果没有能够满足3D-SIC细间距要求的探针技术,那么在KGD测试过程中这些TSV的故障是无法观测的。设计者可通过为所有的TSV I/O使用双向I/O包装器单元(wrapper cell)来克服该障碍。TetraMAX可按照双向引脚形式为I/O建立模型,然后生成允许在TSV I/O中应用和捕获数据的TSV“回路”测试,验证其功能。

缺陷驱动型嵌入式存储器自测试是KGD测试的另一个重要组成部分。3D集成系统的设计者可通过Synopsys的DesignWare自测试和修复(STAR)存储器系统为Synopsys和第三方存储器实现最高的缺陷覆盖率。

电源测试注意事项

3D-SIC系统复杂度越高,对动态功耗的控制要求就越高。功耗在裸片粘接到堆叠前后是不同的(因为裸片粘接后TSV为堆叠分配电源)。需要使用功率感知(power-aware)ATPG和基于电源域测试等先进的电源管理技术来限制功耗,从而最大程度地减少3D-SIC测试过程中的误报故障。功率感知ATPG、DFTMAX和TetraMAX协同工作可生成能够把Shift模式和capture模式功耗限制在功能水平(基于设计者指定的开关转换预算)范围以内的模型。

通过基于电源域测试,TetraMAX能够生成符合设计功能电源状态要求的模型,降低动态功率和泄露功率,并尽量减少IR压降问题的发生。此外,它还可通过生成用于测试电源管理电路的模型序列进一步提高缺陷覆盖率。Synopsys的高级电源管理功能已成功部署到2D设计中,以提高缺陷覆盖率和限制ATE上的误报故障。这些高级电源管理功能将在3D-SIC测试中发挥重要作用。

堆叠测试

TetraMAX生成KGD模型后,把KGD模型映射到堆叠级端口是一个简单的过程。对于TSV互连测试,TetraMAX使用动态桥接故障模型生成针对TSV I/O之间时序的全速测试模型。但堆叠测试的主要挑战是设计和实现能够向非底部裸片提供足够测试接口的3D DFT架构,以便进行单独裸片测试,裸片间测试(即TSV互连测试)和可能的多裸片同时测试。Synopsys正积极参与IEEE P1838等新兴3D测试标准的开发。虽然这些标准尚未整合使用,但早期采用者可使用Synopsys的合成测试解决方案来高效地实现基于已确立标准的3D DFT架构。

例如,DFTMAX可为使用IEEE Std 1149.1作为测试接入机制的3D-SIC系统合成、连接和验证JTAG测试接入端口(TAP)和边界扫描寄存器(BSR)逻辑,以便进行KGD或堆叠测试。

此外,DFTMAX还使用IEEE Std 1500标准进行芯核包装和“裸片包装”——当非底部裸片的测试控制接口使用基于IEEE Std 1500标准的包装器时。同样,位于底部裸片并通过JTAG TAP接收指令的DesignWare STAR存储器系统可使用IEEE Std 1500接口为堆叠中所有其它裸片的嵌入式存储器提供必要的测试接入和隔离。

在每块裸片上实现测试接口后,测试接口采用菊花链方式在堆叠内上下互连,实现对逻辑搭载逻辑(logic-on-logic)和逻辑搭载存储器(memory-on-logic)配置的堆叠测试,如图4所示。

图4:Synopsys支持对基于已确立测试接入标准的逻辑搭载逻辑(LoL)和逻辑搭载存储器(MoL)系统进行3D-SIC测试。

能够通过JTAG TAP访问3D-SIC中的嵌入式测试和调试资源的另一个功能是DesignWare SERDES IP(UPx)。Synopsys的高速接口自测试似乎兼容新兴的IEEE Std P1687标准(推荐的仪器使用标准),并且是对3D-SIC产品成功认证和部署起到关键作用的器件接入机制的一个典型类型。除了上述标准以外,Synopsys的测试解决方案使用STIL(IEEE Std 1450.x)和CTL(IEEE Std 1450.6)作为主流接口连接到电子设计和制造行业中的其它系统,并且作为对2.5D和3D封装配置同时进行测试的手段。

上一篇:电阻网络器件需要各种测量技术(二)

下一篇:利用SPICE设计TEC温度环路PID控制

推荐阅读最新更新时间:2024-03-30 22:53

固定宽带接入速率测试方法行业标准报批稿公示

4月16日消息,《固定宽带接入速率测试方法》行业标准报批稿日前已完成编制,开始公示。 据悉,本标准是《宽带网络服务质量及评测方法》系列标准之一,工信部电信研究院、中国电信、中国移动、中国联通等单位参与起草。 本标准规定了宽带接入速率的定义、测试设备要求、基准测试方法、替代测试方式及测试数据的处理方法。适用于对宽带接入服务商提供给家庭固定宽带用户的接入速率进行测试,不适用于企业专线接入的情况。 本标准所指网络包括接入网、城域网、骨干网和国际互联网等部分。据悉,根据网站服务器所处位置的不同,用户访问网站时信息流在网络各部分传递的途径也有所不同,因此用户最终访问网站所体验到的宽带网络速率,也会受到从用户终端到网站服

[网络通信]

视频监控摄像机动态范围的几种测试方法

摘要: 在应用安防监控摄像机时,经常会出现明暗反差较大或逆光的场景,使得图像中明亮的区域曝光过度、较暗的区域欠曝光,而不能看清图像最亮与最暗部分。因此,各摄像机厂家竞相开发了宽动态摄像机。但如何检测其宽动态性能,是工程商等应用人员急需了解的。本文介绍摄像机动态范围的基本概念,重点介绍国外三大厂商各自对监控摄像机动态范围的具体测试方法,以供工程商等应用人员测试选用参考... 引言 由于自然光线的排列是从120000Lux到星光夜里的0.00035Lux,室内照度为100Lux,而外面风景的照度可能是10000Lux,因此当摄像机从室内看窗户外面,两者对比就是10000/100=100∶1。这个对比人眼能很容易地

[安防电子]

针对不同要求的两种高频基准整流器的测试方法分析与比较

随着LED灯的慢慢普及,传统的节能灯和荧光灯灯在慢慢退出市场。在未来几年LED灯成为主流照明产品成为必然,当然在这几年的过渡期,节能灯和荧光灯还是在某些领域占据主流。和LED灯的基本组成部分一样,节能灯也是由灯管(光源)和电子整流器和Fixture(外壳)等组成,其中最重要部分之一的电子整流器的质量好坏在很大程度上决定了节能灯的使用寿命,在这其中T5灯管采用的高频基准整流器(25KHz)的地位最为突出。如何检测高频电子整流器成为关键,为此IEC(国际电工委员会)制定了相关的测试标准主要有IEC60081(双端荧光灯测试要求)和IEC60901(单端荧光灯测试要求)。同时根据实际情况,这里还有另外一种IEC同等的测试方法。 针对

[模拟电子]

面向运算放大器应用的电阻器网络

某些理想的运算放大器配置假定反馈电阻器呈现完美的匹配。而实际上,电阻器的非理想性会对各种电路参数产生影响,例如:共模抑制比(CMRR)、谐波失真和稳定性。如图1例子所示,配置一个单端放大器以将接地参考信号电平移位至2.5V共模电压就需要一个上佳的CMRR。假设CMRR为34dB且没有输入信号,则该2.5V电平移位器将产生一个50mV的输出偏移,其甚至有可能压倒12位ADC和驱动器的LSB和偏移误差。

图1:用作电平移位器的单端运放

对于运放而言,34dB是一个不太理想的CMRR。然而,不管该运放的性能如何,一个由1%容差电阻器构成的反馈网络会将CMRR限制在34dB。高度匹配的电阻器 (比如 LT54

[电源管理]

粉末真密度测试仪使用说明和测试方法

粉末真密度测试,是指粉末质量与其真实体积之比值,(真体积不包括存在于粉体颗粒内部的封闭孔隙)。所以,测定粉体的真密度必须是无孔材料。基于“阿基米德原理(密度=质量/体积)”的“气体置换法”,以气体取代液体,对被测定样品所排出的体积进行测量.粉末的特性应不溶于水或者酒精。 粉末真密度测试仪使用说明:使用时请详细阅读产品使用说明书;确保检测环境不受外界电磁场干扰;工作台应避免震动影响;当粉末完全浸入液体中,必须完全排除其气泡,才能确定其所排除的体积。 粉末真密度测试仪器操作方法: 1、先将玻璃杯放置秤量台上,按0键归零;再将粉末样品倒入容器内,稳定符号O出现后,在屏幕上方会显示OK,按MODE记录样品的重量值(W1) 2、将比

[测试测量]

用简单的测试方法检查电池的容量

大多数手持设备使用碱性或可充电电池,因此测量电池容量是此类设计的关键特征。但是,在大多数情况下,对于预算紧张的项目而言,使用电池电量监控IC可能是一种奢望。这是一个更简单,更便宜的选择。 如今,即使是最便宜的微控制器也经常包括内部模数转换器(ADC)模块,并且由于其(相对)较低的分辨率和较高的噪声水平,一直没有使用该模块。但是,那些未使用的内部ADC通道之一足以执行测试以确定电池是否仍然可用。 用于检测电池状态的方法称为电化学动态响应(EDR)(参考文献1),并由Cadex Electronics的美国专利号7,622,929授予专利。 EDR通过施加负载脉冲并评估电池对攻击和恢复的响应时间,将负载下的电池状况与存储的

[测试测量]

传索尼五月初发A77 II 搭2400万像素传感器

索尼在今年已经发布了不少全新的影像类产品,之前刚刚发布的A7S可谓是一款让人惊艳的视频功能强大的微单机型,这似乎让人们已经开始渐渐淡忘索尼的单电系列产品了。不过索尼可没有忘记自己的产品线,根据最新消息,索尼在5月初还将举办一场发布会,A77 II很有可能会在届时发布。

索尼的A77似乎终于要迎来自己的继任者了

从已获得的最新消息来看,新相机将会采用一枚全新的2400万像素传感器,拥有性能更好的AF对焦系统,并将进一步提升相机的连拍性能。不过相对于这些提升,我们还是更加关注新一代的A77 II是否仍将使用之前的半透镜技术。同时还有几枚FE镜头的消息,至于是否属实,我们还要等待更多的消息,我们也会 及时为大家带来

[家用电子]

氧化铝水分测试方法及注意事项

氧化铝粉可增加到各种水性树脂、油性树脂内、环氧树脂、丙烯酸树脂、聚胺酯树脂、塑料、橡胶中,增加量为3%-5%,能够明显提高原料的硬度,硬度可达6-8H甚至更高。还能够用在导热、抛光、电镀、催化剂等。氧化铝粉的出产工艺越来越高,现已能够出产1微米以下的氧化铝粉。纳米氧化铝通明液体XZ-LY101体颜色无色通明。该纳米氧化铝通明涣散液中运用的是5-10纳米的氧化铝,该氧化铝是纳米氧化铝通过层层深加工挑选出来的氧化铝。 氧化铝(Al?O?)是一种高硬度的化合物,熔点为2054℃,沸点为2980℃,在高温下可电离的离子晶体,常用于制作耐火材料。宝石晶体凡人应用、 红外军事装置、卫星空间技术、高强度激光的窗口材料、半导体照明产业、光电物

[测试测量]

小广播

热门活动

换一批

更多

最新测试测量文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

11月13日历史上的今天

- 特斯拉AutoPilot如何自我进化?高管解读背后AI技术

- 车载大屏/曲面已够潮 伟世通还能这样玩

- 第二代宝马数字密钥车辆访问系统将于2019年底公布

- Cepton将激光雷达与MechaSpin处理引擎结合 可对车辆即时分类

- 德州仪器为降低噪声和系统功耗推出新一代逻辑单元

- 华为nova9系列获推鸿蒙HarmonyOS 2.0.1.162:增多机位模式

- 万亿美元市值的特斯拉在中国建数据中心意欲何为?

- Redmi Note 11 Pro现身跑分网站:搭天玑920芯片,预装安卓11

- 1亿像素!Redmi Note 11系列官方样张公布

- 搭载激光雷达和5纳米芯片的通用汽车Ultra Cruise全揭秘

厂商技术中心

数字逻辑与数字系统 (李景宏 王永军 等编著)

数字逻辑与数字系统 (李景宏 王永军 等编著) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号