1 引言

由于传统的多波形函数信号发生器需采用大量分离元件才能实现,且设计复杂,这里提出一种基于CPLD的多波形函数信号发生器。它采用CPLD作为函数信号发生器的处理器,以单片机和CPLD为核心,辅以必要的模拟和数字电路,构成的基于DDS(直接数字频率合成)技术、波形稳定、精度较高的多功能函数信号发生器。

2 系统设计

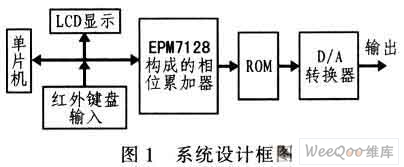

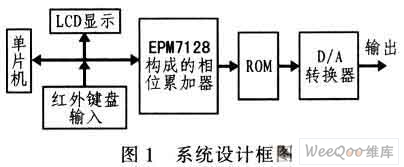

图1给出系统设计框图,该系统设计主要由CPLD电路、单片机电路、键盘输入液晶显示输出电路以及D/A转换电路和低通滤波器等电路组成。

2.1 频率合成器

该系统设计采用直接数字式频率合成DDS(Direct Digital Frequency Synthesis)技术,采用ROM存储所需的量化数据,按照不同频率求出频率控制字。以K为步进对相位累加器进行累加,每累加一次,取出累加器的高8 位数据送至ROM,ROM根据不同的地址取出不同的数据送TLC7524进行转换。再经过滤波即可得到所需要波形。由于DDS具有相对带宽很宽,频率转换时间极短,频率分辨率高等优点。此外,全数字化结构便于集成,输出相位连续,频率,相位和幅度均可实现程控。

2.2 幅度控制模块

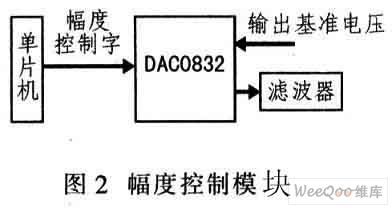

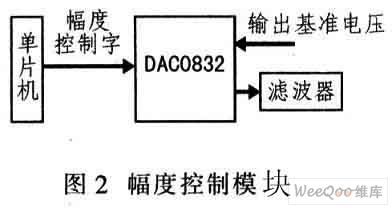

幅度控制模块由DAC0832控制,利用其内部电阻分压网络,将其作为数控电位器。将 TLC7524的输出波形作为DAC0832的基准电压源输入,其输出波形为V=(N/256)×Vin,其中N为单片机输入的幅度控制字。通过一简单的电阻分压网络调整运放输出峰一峰值为0~5 V,再送至DAC0832由单片机控制其幅度实现幅度的步进,如图2所示。

2.3 后级处理模块

采用二阶巴特沃兹低通滤波器。巴特沃兹低通滤波器的幅度函数是单调下降的,由于n阶低通巴特沃兹低通滤波器的前(2n-1)阶导数在ω=0处为零,所以巴特沃兹低通滤波器也称最大平坦幅度滤波器。由于该设计要求滤除的频率分量主要为由D/A转换器产生的高频分量,与系统所要求保留的频率相差很远,所以滤波器在通频带内的平坦程度比其衰减陡度更为重要,而且巴特沃兹低通滤波器所要的元件值合乎实际情况,不像其他滤波器要求元件值那么苛刻。

3 硬件电路系统设计

3.1 总体设计思路

整个系统以CPLD(EPM7128)、AT89S51、AT28C64(EEP-ROM)为核心。CPLD通过相位累加产生读取ROM的地址。以单片机为系统控制的核心,主要功能:给CPLD送频率控制字,即相位累加器的累加值,以此控制频率;给D/A转换器送幅度控制字D,控制波形幅度;处理红外遥控键盘;送数据给液晶LCD。EEPROM存储已固化好波形的数据。

3.2 CPLD模块

该模块通过一个4引脚的工业标准JTAG接口在系统编程(ISP),并且在编程过程中仅需5.0 V单电压供电。编程过程中,I/O引脚处于三态并被上拉,以消除板上冲突。上拉阻值为1 kΩ。因为该器件是在线编程的,为了便于调试,所以把下载口直接做在电路板上。考虑到电源为自制的稳压电源,CPLD受电源纹波干扰影响较大,所以在每个器件旁都加有去耦电容。

3.3 D/A转换及幅度控制

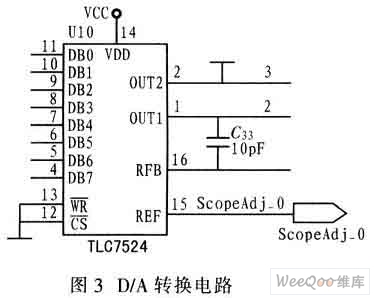

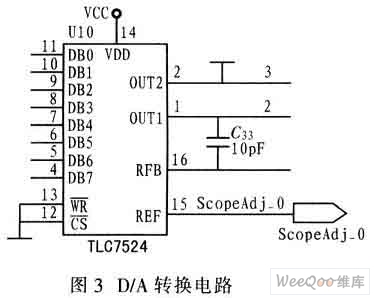

D/A转换采用TI公司的TLC7524,该器件转换速度可达10 M,幅度控制D/A转换采用MAX518,该器件是I2C总线的双D/A转换器,只需很少的端口线就可实现两路幅度的控制,大大节省单片机的端口。图3给出D/A转换电路。 [page]

3.4 后级处理模块

低通滤波器对阶梯正弦波进行傅里叶分析。其中若一周期采样点数为N,则其高次谐波能量主要集中在输出频率的(N±1)倍频上,其幅值为基频的 1/(N±1)。低通滤波可以平滑其台阶。另外还需滤除由DAC0832和TCL7524产生的1MHz和10 MHz的高频分量。因此根据设计的要求(输出最大频率为250 kHz,为了保证250 kHz频带内输出幅度平坦,又要尽可能抑制谐波和高频分量,综合考虑选用宽带运放LF351,用EWB仿真表明:截止频率为1 MHz~250 kHz以内幅度平坦。为了保证稳幅输出,选用AD817。该器件是一种低功耗、高速、宽带运算放大器,具有很强的大电流驱动能力。实际电路测量表明:当负载为100 Ω,输出峰-峰值为10 V时,其带宽大于500 kHz,幅度变化小于±1%。

4 软件设计

4.1 波形发生

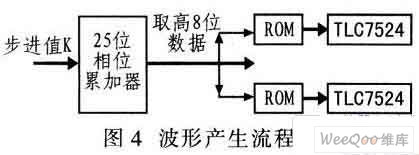

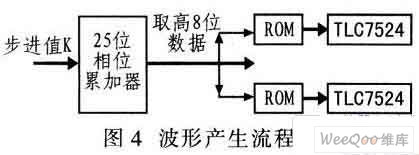

在CPLD内设置25位相位累加器,高9位为ROM地址,低16 位为产生精确的读ROM的点与点之间的时间间隔而设置的累加寄存器,即:单片机送一频率控制字,由低16位寄存器每个时钟都累加这个值,累加到低16位溢出,然后ROM的地址加1。ROM内的每个地址的数据表示当前波形的幅度,然后连续读出数据并被平滑滤波后得出平滑、稳定的波形。波形产生流程如图4所示。

4.2 幅度控制

系统的幅度控制由MAX518完成,利用其内部电阻网络实现数字电位器功能,输出电压作为TLC7524的基准电压。图5为幅度控制流程。

5 电路系统调试与参数测试

调试与测试所用仪器PC机、双踪模拟示波器YUAN-LONG、SS7200通用智能计数器、DT9205三位半数字万用表。在户1 kHz步进为20 mV下,测试电压幅度。表1为电压幅度测试,表2为输出频率测试。

6 结论

基于单片机和CPLD的DDS正交信号源,其频率幅度可精密控制,扩展输出频率达300 kHz,增加扫频输出功能。采用红外键盘控制频率和幅度,采用液晶同步显示信号的频率和幅度;输出端产生正弦波、方波、三角波、锯齿波,梯形波、短形波、频率突变的方波、尖脉冲数字信号等,且具有扫频输出的功能。测试结果表明,系统稳定可靠,人机交互界面友好,操作简单方便。

关键字:CPLD DDS 滤波器 正交信号源

引用地址:基于CPLD及DDS的正交信号源滤波器的设计

由于传统的多波形函数信号发生器需采用大量分离元件才能实现,且设计复杂,这里提出一种基于CPLD的多波形函数信号发生器。它采用CPLD作为函数信号发生器的处理器,以单片机和CPLD为核心,辅以必要的模拟和数字电路,构成的基于DDS(直接数字频率合成)技术、波形稳定、精度较高的多功能函数信号发生器。

2 系统设计

图1给出系统设计框图,该系统设计主要由CPLD电路、单片机电路、键盘输入液晶显示输出电路以及D/A转换电路和低通滤波器等电路组成。

2.1 频率合成器

该系统设计采用直接数字式频率合成DDS(Direct Digital Frequency Synthesis)技术,采用ROM存储所需的量化数据,按照不同频率求出频率控制字。以K为步进对相位累加器进行累加,每累加一次,取出累加器的高8 位数据送至ROM,ROM根据不同的地址取出不同的数据送TLC7524进行转换。再经过滤波即可得到所需要波形。由于DDS具有相对带宽很宽,频率转换时间极短,频率分辨率高等优点。此外,全数字化结构便于集成,输出相位连续,频率,相位和幅度均可实现程控。

2.2 幅度控制模块

幅度控制模块由DAC0832控制,利用其内部电阻分压网络,将其作为数控电位器。将 TLC7524的输出波形作为DAC0832的基准电压源输入,其输出波形为V=(N/256)×Vin,其中N为单片机输入的幅度控制字。通过一简单的电阻分压网络调整运放输出峰一峰值为0~5 V,再送至DAC0832由单片机控制其幅度实现幅度的步进,如图2所示。

2.3 后级处理模块

采用二阶巴特沃兹低通滤波器。巴特沃兹低通滤波器的幅度函数是单调下降的,由于n阶低通巴特沃兹低通滤波器的前(2n-1)阶导数在ω=0处为零,所以巴特沃兹低通滤波器也称最大平坦幅度滤波器。由于该设计要求滤除的频率分量主要为由D/A转换器产生的高频分量,与系统所要求保留的频率相差很远,所以滤波器在通频带内的平坦程度比其衰减陡度更为重要,而且巴特沃兹低通滤波器所要的元件值合乎实际情况,不像其他滤波器要求元件值那么苛刻。

3 硬件电路系统设计

3.1 总体设计思路

整个系统以CPLD(EPM7128)、AT89S51、AT28C64(EEP-ROM)为核心。CPLD通过相位累加产生读取ROM的地址。以单片机为系统控制的核心,主要功能:给CPLD送频率控制字,即相位累加器的累加值,以此控制频率;给D/A转换器送幅度控制字D,控制波形幅度;处理红外遥控键盘;送数据给液晶LCD。EEPROM存储已固化好波形的数据。

3.2 CPLD模块

该模块通过一个4引脚的工业标准JTAG接口在系统编程(ISP),并且在编程过程中仅需5.0 V单电压供电。编程过程中,I/O引脚处于三态并被上拉,以消除板上冲突。上拉阻值为1 kΩ。因为该器件是在线编程的,为了便于调试,所以把下载口直接做在电路板上。考虑到电源为自制的稳压电源,CPLD受电源纹波干扰影响较大,所以在每个器件旁都加有去耦电容。

3.3 D/A转换及幅度控制

D/A转换采用TI公司的TLC7524,该器件转换速度可达10 M,幅度控制D/A转换采用MAX518,该器件是I2C总线的双D/A转换器,只需很少的端口线就可实现两路幅度的控制,大大节省单片机的端口。图3给出D/A转换电路。 [page]

3.4 后级处理模块

低通滤波器对阶梯正弦波进行傅里叶分析。其中若一周期采样点数为N,则其高次谐波能量主要集中在输出频率的(N±1)倍频上,其幅值为基频的 1/(N±1)。低通滤波可以平滑其台阶。另外还需滤除由DAC0832和TCL7524产生的1MHz和10 MHz的高频分量。因此根据设计的要求(输出最大频率为250 kHz,为了保证250 kHz频带内输出幅度平坦,又要尽可能抑制谐波和高频分量,综合考虑选用宽带运放LF351,用EWB仿真表明:截止频率为1 MHz~250 kHz以内幅度平坦。为了保证稳幅输出,选用AD817。该器件是一种低功耗、高速、宽带运算放大器,具有很强的大电流驱动能力。实际电路测量表明:当负载为100 Ω,输出峰-峰值为10 V时,其带宽大于500 kHz,幅度变化小于±1%。

4 软件设计

4.1 波形发生

在CPLD内设置25位相位累加器,高9位为ROM地址,低16 位为产生精确的读ROM的点与点之间的时间间隔而设置的累加寄存器,即:单片机送一频率控制字,由低16位寄存器每个时钟都累加这个值,累加到低16位溢出,然后ROM的地址加1。ROM内的每个地址的数据表示当前波形的幅度,然后连续读出数据并被平滑滤波后得出平滑、稳定的波形。波形产生流程如图4所示。

4.2 幅度控制

系统的幅度控制由MAX518完成,利用其内部电阻网络实现数字电位器功能,输出电压作为TLC7524的基准电压。图5为幅度控制流程。

5 电路系统调试与参数测试

调试与测试所用仪器PC机、双踪模拟示波器YUAN-LONG、SS7200通用智能计数器、DT9205三位半数字万用表。在户1 kHz步进为20 mV下,测试电压幅度。表1为电压幅度测试,表2为输出频率测试。

6 结论

基于单片机和CPLD的DDS正交信号源,其频率幅度可精密控制,扩展输出频率达300 kHz,增加扫频输出功能。采用红外键盘控制频率和幅度,采用液晶同步显示信号的频率和幅度;输出端产生正弦波、方波、三角波、锯齿波,梯形波、短形波、频率突变的方波、尖脉冲数字信号等,且具有扫频输出的功能。测试结果表明,系统稳定可靠,人机交互界面友好,操作简单方便。

上一篇:可变低通滤波器在滤除噪声干扰中的应用

下一篇:基于PSO的FIR数字滤波器设计

推荐阅读最新更新时间:2024-03-30 22:54

CPLD在信号滤波和抗干扰中的应用

摘要: 滤波和抗干扰是任何智能仪器系统都必须考虑的问题。在传统的应用系统中,滤波部分往往要占用较多的软件资源和硬件资源。复杂可编程逻辑器件(CPLD)的出现,为解决这一问题开辟了新的途径,条用CPLD实现滤是一种高效可靠的方法。介绍了利用MAX+PLUS Ⅱ对CPLD编程来实现对传感器和按键信号滤波和抗干扰。该方法已在产品开发中获得了成功应用。 1 滤波和抗干扰概述 单片机应用系统的输入信号常含有种种噪声和干扰,它们来自被测信号源、传感器、外界干扰源等。为了提高测量和控制精度,必须消除信号中的噪声和干扰。噪声有两大类:一类为周期性的;另一类为不规则的。前者的典型代表为50Hz的工频干扰,一般采用硬件滤波,使用积

[模拟电子]

追投27亿元,卓胜微35亿元投建射频 SAW 滤波器晶圆产线等

集微网消息,3月31日,江苏卓胜微电子股份有限公司(以下简称“卓胜微”)发布公告称,3月29日,公司召开第二届董事会第六次会议、第二届监事会第五次会议,通过《关于拟进一步对外投资签署合作协议的议案》,同意对芯卓半导体产业化建设项目追加投资27亿元,以进一步扩充 SAW 滤波器晶圆制造和射频模组封装测试产能及厂房及配套设施建设。 公告显示,芯卓半导体产业化建设项目总投资金额为35亿元,主要进行射频 SAW 滤波器晶圆制造和射频模组封装测试产能及厂房及配套设施建设扩建。 项目建成后,将提升卓胜微在射频 SAW 滤波器领域的整体工艺技术能力和模组量产能力,实现射频 SAW 滤波器芯片和射频模组的全产业链布局,提升公司的自主研发创新能

[手机便携]

应用于晶体管图示仪的CPLD控制器设计

晶体管图示仪是电路设计中常用的电子仪器,它能够显示晶体管的输入特性、输出特性和转移特性等多种曲线和参数。它不仅可以测量晶体二极管和三极管,还可以测量场效应管、隧道二极管、单结晶体管、可控硅和光耦等器件。但传统的晶体管图示仪存在着电路复杂,体积庞大,示波管的显示屏小,功耗大,价格昂贵等缺点。随着计算机软硬件技术、单片机技术和EDA技术的不断发展及其在电工电子测量技术的应用,晶体管图示仪在结构、工作原理和功能上发生很大变化,成为数字化和智能化的虚拟仪器。本文设计的晶体管图示仪就是这样一种新型仪器,除改善了原有仪器不足之外,还扩展了仪器功能,具有图形保存,数据处理,界面显示灵活,可操作性强,性能价格比高等优点。 1 系统结构

[嵌入式]

一种便携式心电监护仪前置放大电路和抗干扰的设计(一)

监护仪是一种用以测量和监控病人生理参数、并可与已知设定值进行比较、如果出现超差可发出报警的装置或系统。便携式监护仪小型方便,结构简单,性能稳定,可以随身携带,可由电池供电,一般用于非监护室及外出抢救病人的监护。导联系统采用通用的三电极方式,右胸上电极及左腹下电极为心电采样电极,右腹下电极为右腿驱动电极。这种联接方式有效实用,有利于便携使用。便携式监护仪分析处理系统可以分为两大部分,一是携带在被检查者身上的袖珍监护仪,另一为由微机系统组成的心电图处理诊断系统。被检查者将某一时段的动态心电信号由监护仪记录下来,通过GPRS通信方式将数据传送到医院的心电图处理诊断系统中。 体表心电信号的频率主要集中在0. 05~ 100Hz,幅度为

[医疗电子]

采用ARM和CPLD结构的检测系统可重构设计方法

引言 检测系统的可重构设计是检测技术的发展方向。可重构设计是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。对于检测系统而言,可重构可以分为软件可重构和硬件可重构。采用硬件可重构技术设计的检测系统具有硬件普适性,通过更换各个硬件模块或配置不同的软件代码,即可实现不同功能的检测,从而减少硬件和软件开发上的投入、缩短产品开发周期。 本文提出了一种基于ARM嵌入式微处理器和复杂可编程逻辑器件( CPLD) 的检测系统硬件可重构设计方法。这种结构检测系统既具有ARM微控制器体积小、集成度高、运算速度快、存储器容量大、功耗低等特点; 又具有CPLD强大的高速逻辑处理能力和方便灵活的动态可重构性,将两者结合

[单片机]

多家上市公司欲抢食滤波器百亿美元“蛋糕

麦捷科技(7.97 +2.31%,诊股)(300319,SZ)公告,拟联合合肥中电科国元产业投资基金合伙企业(有限合伙)(以下简称合肥电科国元)分别向重庆胜普电子有限公司(以下简称胜普电子)增资3264.29万元和1305.71万元,增资完成后,将分别持有后者35%和14%的股份。麦捷科技表示,此次股权合作致力于推动移动通信行业核心器件滤波器的芯片国产化。 随着5G通信时代的即将到来,射频滤波器被认为将迎来百亿美元级的市场。而在目前主要由日本和美国企业所把控的滤波器市场,以麦捷科技和信维通信(31.04 -3.00%,诊股)(300136,SZ)为代表的国内上市公司也在逐渐加码,积极进入这一市场欲抢食“蛋糕”。 欲推动

[半导体设计/制造]

一个嵌入式系统的Petri网模型与CPLD实现

摘要:将Petri网与VHDL结合,运用Petri网建立硬件系统模型,然后采用VHDL语言进行设计,最终下载到CPLD,成功地实现了整个硬件系统的逻辑控制器设计。

关键词:Petri网 C/E模型 VHDL CPLD

Petri网是异步并发系统,没有人为的控制流,直观地表示了非确定性;且可以图形化的方式描述复杂的系统,并可运用数学工具进行分析。因此,其在软件系统的建模与仿真中得到广泛应用。Petri网自身具备的可运行性方便了系统形式化描述级的模拟,可以用于表达不同抽象级上的系统概念并清楚地描述整个系统的运作过程。笔者发现Petri网的应用目前仅局限于软件系统的设计,例如网络协议、物流管理等,而在硬件系统中却很少涉足。硬件系统

[半导体设计/制造]

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号