引言

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,可测性设计(DFT)的功耗问题引起了VLSI设计者越来越多的关注。因为在测试模式下电路的功耗要远远高于正常模式,必将带来如电池寿命、芯片封装、可靠性等一系列问题。随着集成电路的发展,内建自测试(BIST)因为具备了诸多优越性能(如降低测试对自动测试设备在性能和成本上的要求、可以进行At—speed测试及有助于保IP核的知识产权等),已成为解决SoC测试问题的首选可测性设计手段。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。

另外,在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而由LFSR产生的连续测试模式之间的相关性很低。因此,在自测试期间会增加电路中节点的翻转活动,导致功耗增大。

2 功耗分析和WSA模型

CMOS电路*耗的来源主要分为静态功耗和动态功耗两种。漏电流或从电源供给中持续流出的其它电流导致静态功耗。动态功耗则是因为短路电流和负载电容的充放电,从而由电路正常工作时的功能跳变所引起的,它包括功能跳变、短路电流、竞争冒险等。对于CMOS工艺来说,目前动态功耗是电路功耗的主要来源。

对于节点i上每次开关上的功耗为:

式中,Si是单周期内翻转的次数,Fi是节点i的扇出,C0是最小输出负载电容,VDD是电源电压。

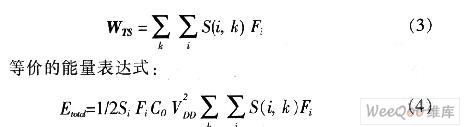

从式(1)看出,门级的功耗估计与Si和Fi的乘积和节点i的翻转次数有关。节点的扇出由电路拓扑决定,而它的翻转次数由逻辑模拟器来估计。这个乘积即称为节点i的权重翻转活动(Weighted Switching Activity,WSA)。在测试过程中WSA是节点i功耗Ei的唯一变量,所以WSA可作为该节点的功耗估计。对于一对连续的输入矢量TPk=(Vk-1,Vk),电路总的WSA为:

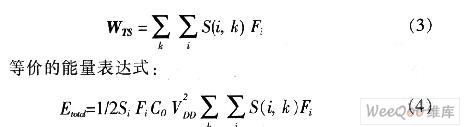

式中i是电路中所有节点的个数,S(i,k)是由TPk所激励节点i的翻转次数。

根据式(2),考虑长度为L的测试矢量TS作为电路的输入矢量,电路总的WSA为:

根据以上功率和能量消耗的表达式,再给定一个电路设计为CMOS的工艺和供给电源,可得以下结论:

(1)电路中节点i的跳变数成为唯一的影响能量、最大功耗和平均功耗的参数。

(2)测试中时钟的频率也影响着平均功耗和最大功耗。

(3)测试长度,即施加在待测电路(CUT)上的测试向量的数目一只影响总的能量的消耗。

3 LFSR优化的低功耗方法

通过对测试过程的功耗分析可知,选择BIST低功耗的方案时,一方面可以通过减少测试序列长度来实现(但该方法往往以牺牲故障覆盖率为代价),另一方面降低WSA值也可实现系统功耗的降低。

在BIST结构中,线性反馈移位寄存器(LFSR)由于结构的简单性、规则性、非常好的随机测试矢量生成特性、用来压缩测试响应时的混淆概率非常小等特点,在DFT的扫描环境中很容易集成,所以当从扫描DFT设计升级成BIST设计时,LFSR因其硬件开销很小而成为BIST中应用最广的矢量生成结构。

基于LFSR优化的BIST结构可分为test—per-一scan和test—per—clock两类结构。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展:而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。

3.1 基于扫描的test—per—scan方式

3.1.1 基本结构

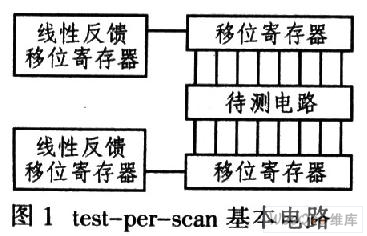

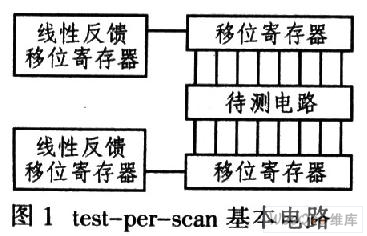

test—per一scan内建自测试的目标是尽可能的降低硬件开销。这种结构在每个输入输出端口处使用LFSR与寄存器的组合来代替LFSR。图l是test—per-scan内建自测试的基本电路结构。在内建自测试矢量下,LFSR生成测试矢量并且通过扫描移位寄存器(shift register)将测试矢量移位到待测电路(CUT)的输入端,同时响应被移入LFSR并压缩。 [page]

3.1.2 原理

全扫描或部分扫描设计中由于移位会产生比较大的功耗。基于扫描的test一per-scan低功耗设计方法需要修改标准的扫描设计,降低状态转换活动率。没计修改包括在移位期间用于屏蔽扫描路径活动的一些门控逻辑,以及对用于抑制随机模式的附加逻辑进行综合等。

3.1. 3 部分扫描算法

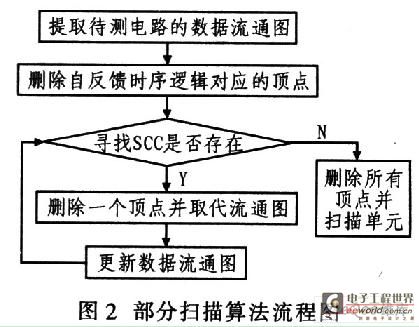

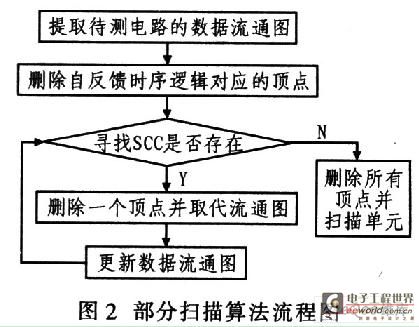

根据以上扫描设计原理,在消除测试序列中的冗余模式之后,采用图2所示的部分扫描算法对待测电路进行部分扫描设计。其步骤如下:

①首先删除所有自反馈时序逻辑对应的顶点。

②在数据流图中查找所有的强连通单元(Strongly Connected Components,简称SCC)。

③依次删除SCC所有顶点中最大的顶点。

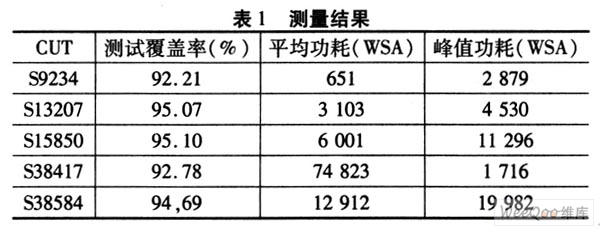

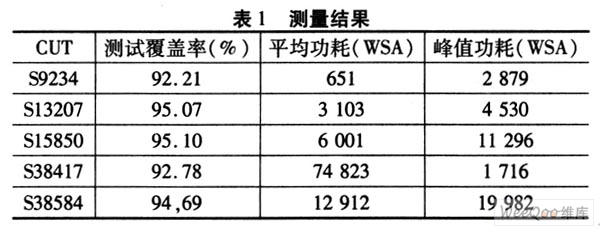

参考文献采用上述算法对ISCA89基准电路扫描BIST测试,并采用ATPG工具和仿真工具VCS故障模拟和功能模拟,表1列出测试覆盖率、平均功耗和峰值功耗数据。

由表l数据可见,部分扫描对待测电路测试覆盖率影响非常小(3.2 基于时钟的test—per-clock方式

3.2.1 基本结构

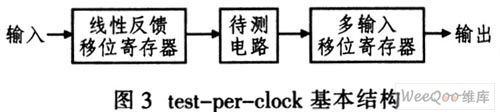

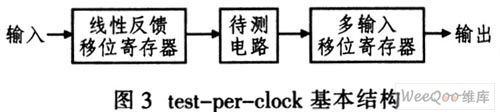

一个test-per-clock内建自测试基本结构如图3所示。每一个测试时钟L2SR生成一个测试矢量。多输人特征寄存器(Multiple-一Input Signature Register,简称MISR)压缩一个响应矢量。 [page]

3.2.2 原理

在扫描测试中,主要功耗包括逻辑功耗、扫描功耗和时钟功耗。前面给出的方法主要集中在降低逻辑功耗或扫描功耗,但没有降低时钟功耗。基于时钟的低功耗test—per—clock方式可以同时降低这3种功耗。该方法采用低功耗的test—per-一clock BIST结构。对LFSR进行修改后,用作TPG以生成低功耗的测试矢量。使用这种经过修改的时钟方案会降低被测电路、TPG和馈给TPG的时钟树的跳变密度。通过降低被测电路、TPG和时钟树的状态转换活动率来降低BIST期间的功耗。

由于来源于标准扫描结构的测试模式可直接用于低功耗扫描结构,这种方法与采用传统扫描结构所达到的故障覆盖率和IC测试时间基本一致。与传统扫描结构相比,面积开销很小,在电路性能方面也没有损失。

3.2.3 低功耗测试矢量生成

对于test—per—clock结构来说,减少测试功耗主要通过优化测试矢量来实现,而测试矢量生成技术是指产生确定性测试矢量的技术。

测试矢量生成方式在生成测试模式时,除了要达到传统的ATPG目的,还需考虑降低测试期间的功耗。基于ATPG的方法又分为2种:①集成的ATPG优化方法,该方法的测试模式在测试生成期间进行低功耗优化;②ATPG之后的优化方法,该方法的测试模式首先由传统的ATPG生成,然后再进行功耗优化。

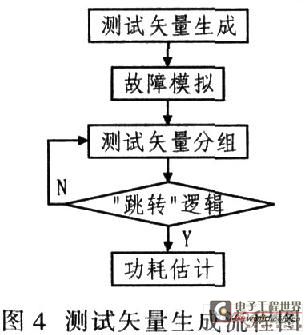

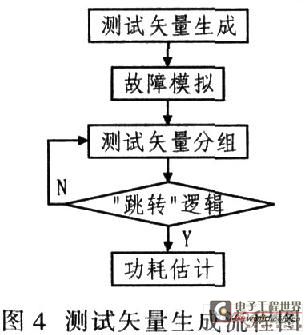

(1)与模拟退火算法相结合测试矢量生成的步骤是:首先根据模拟退火算法将测试模式分组成若干个有效测试矢量组与无效测试矢量组两部分;然后根据算法原理,生成控制LFSR运行的控制码;在这些控制码的作用下,LFSR就跳过大量的无效测试矢量,生成由有效测试矢量构成的精简的测试矢量序列。其基本流程如图4所示。

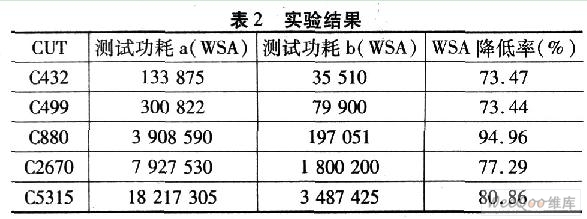

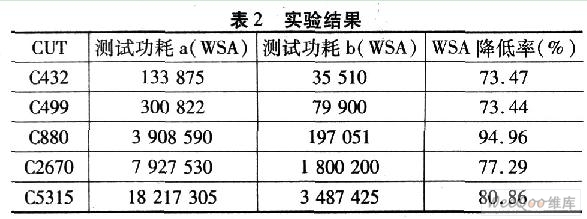

(2)与进化算法相结合依据测试矢量生成技术原理,采用基于遗传算法的测试模式生成器,用于计算冗余的测试模式。在冗余测试模式中,一个故障由几个不同的序列覆盖。然后使用一个优化算法,从前面已计算过的测试序列组合中选择一个最佳子集,使其峰值功率最小,而不影响故障覆盖率。参考文献采用ISCAS’85Bench—mark中的组合电路作为实验电路,在保持故障覆盖率不变的情况下,对待测电路的测试功耗a与使用模拟退火算法的BIST结构的测试功耗b相比较,得到的结果如表2所示。

由表2可知,满足相同故障覆盖率时,采用模拟退火算法分组测试矢量后,WSA大幅降低,总的WSA改善率在73.44%"94.96%之间。由于减少测试矢量,测试时间也大为缩短。

4 结语

采用线性反馈移位寄存器生成测试矢量的BIST结构可分为test—per—scan和test—per—clock两大类,相应的实现低功耗BIST测试方法也分别针对test一per—scan和test—per一clock结构。对tesl—per-scan结构模式,减少测试功耗主要通过优化扫描链来实现;对于test—per-clock结构模式,减少测试功耗主要通过优化测试矢量来实现。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展;而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。当然,随着测试功耗研究的深入,将会有更好的方法使功耗、故障覆盖率、系统性能等问题达到最优。

关键字:BIST LFSR 低功耗

引用地址:基于LFSR优化的BIST低功耗设计

随着便携式设备和无线通讯系统在现实生活中越来越广泛的使用,可测性设计(DFT)的功耗问题引起了VLSI设计者越来越多的关注。因为在测试模式下电路的功耗要远远高于正常模式,必将带来如电池寿命、芯片封装、可靠性等一系列问题。随着集成电路的发展,内建自测试(BIST)因为具备了诸多优越性能(如降低测试对自动测试设备在性能和成本上的要求、可以进行At—speed测试及有助于保IP核的知识产权等),已成为解决SoC测试问题的首选可测性设计手段。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。

另外,在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而由LFSR产生的连续测试模式之间的相关性很低。因此,在自测试期间会增加电路中节点的翻转活动,导致功耗增大。

2 功耗分析和WSA模型

CMOS电路*耗的来源主要分为静态功耗和动态功耗两种。漏电流或从电源供给中持续流出的其它电流导致静态功耗。动态功耗则是因为短路电流和负载电容的充放电,从而由电路正常工作时的功能跳变所引起的,它包括功能跳变、短路电流、竞争冒险等。对于CMOS工艺来说,目前动态功耗是电路功耗的主要来源。

对于节点i上每次开关上的功耗为:

式中,Si是单周期内翻转的次数,Fi是节点i的扇出,C0是最小输出负载电容,VDD是电源电压。

从式(1)看出,门级的功耗估计与Si和Fi的乘积和节点i的翻转次数有关。节点的扇出由电路拓扑决定,而它的翻转次数由逻辑模拟器来估计。这个乘积即称为节点i的权重翻转活动(Weighted Switching Activity,WSA)。在测试过程中WSA是节点i功耗Ei的唯一变量,所以WSA可作为该节点的功耗估计。对于一对连续的输入矢量TPk=(Vk-1,Vk),电路总的WSA为:

式中i是电路中所有节点的个数,S(i,k)是由TPk所激励节点i的翻转次数。

根据式(2),考虑长度为L的测试矢量TS作为电路的输入矢量,电路总的WSA为:

根据以上功率和能量消耗的表达式,再给定一个电路设计为CMOS的工艺和供给电源,可得以下结论:

(1)电路中节点i的跳变数成为唯一的影响能量、最大功耗和平均功耗的参数。

(2)测试中时钟的频率也影响着平均功耗和最大功耗。

(3)测试长度,即施加在待测电路(CUT)上的测试向量的数目一只影响总的能量的消耗。

3 LFSR优化的低功耗方法

通过对测试过程的功耗分析可知,选择BIST低功耗的方案时,一方面可以通过减少测试序列长度来实现(但该方法往往以牺牲故障覆盖率为代价),另一方面降低WSA值也可实现系统功耗的降低。

在BIST结构中,线性反馈移位寄存器(LFSR)由于结构的简单性、规则性、非常好的随机测试矢量生成特性、用来压缩测试响应时的混淆概率非常小等特点,在DFT的扫描环境中很容易集成,所以当从扫描DFT设计升级成BIST设计时,LFSR因其硬件开销很小而成为BIST中应用最广的矢量生成结构。

基于LFSR优化的BIST结构可分为test—per-一scan和test—per—clock两类结构。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展:而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。

3.1 基于扫描的test—per—scan方式

3.1.1 基本结构

test—per一scan内建自测试的目标是尽可能的降低硬件开销。这种结构在每个输入输出端口处使用LFSR与寄存器的组合来代替LFSR。图l是test—per-scan内建自测试的基本电路结构。在内建自测试矢量下,LFSR生成测试矢量并且通过扫描移位寄存器(shift register)将测试矢量移位到待测电路(CUT)的输入端,同时响应被移入LFSR并压缩。 [page]

3.1.2 原理

全扫描或部分扫描设计中由于移位会产生比较大的功耗。基于扫描的test一per-scan低功耗设计方法需要修改标准的扫描设计,降低状态转换活动率。没计修改包括在移位期间用于屏蔽扫描路径活动的一些门控逻辑,以及对用于抑制随机模式的附加逻辑进行综合等。

3.1. 3 部分扫描算法

根据以上扫描设计原理,在消除测试序列中的冗余模式之后,采用图2所示的部分扫描算法对待测电路进行部分扫描设计。其步骤如下:

①首先删除所有自反馈时序逻辑对应的顶点。

②在数据流图中查找所有的强连通单元(Strongly Connected Components,简称SCC)。

③依次删除SCC所有顶点中最大的顶点。

参考文献采用上述算法对ISCA89基准电路扫描BIST测试,并采用ATPG工具和仿真工具VCS故障模拟和功能模拟,表1列出测试覆盖率、平均功耗和峰值功耗数据。

由表l数据可见,部分扫描对待测电路测试覆盖率影响非常小(3.2 基于时钟的test—per-clock方式

3.2.1 基本结构

一个test-per-clock内建自测试基本结构如图3所示。每一个测试时钟L2SR生成一个测试矢量。多输人特征寄存器(Multiple-一Input Signature Register,简称MISR)压缩一个响应矢量。 [page]

3.2.2 原理

在扫描测试中,主要功耗包括逻辑功耗、扫描功耗和时钟功耗。前面给出的方法主要集中在降低逻辑功耗或扫描功耗,但没有降低时钟功耗。基于时钟的低功耗test—per—clock方式可以同时降低这3种功耗。该方法采用低功耗的test—per-一clock BIST结构。对LFSR进行修改后,用作TPG以生成低功耗的测试矢量。使用这种经过修改的时钟方案会降低被测电路、TPG和馈给TPG的时钟树的跳变密度。通过降低被测电路、TPG和时钟树的状态转换活动率来降低BIST期间的功耗。

由于来源于标准扫描结构的测试模式可直接用于低功耗扫描结构,这种方法与采用传统扫描结构所达到的故障覆盖率和IC测试时间基本一致。与传统扫描结构相比,面积开销很小,在电路性能方面也没有损失。

3.2.3 低功耗测试矢量生成

对于test—per—clock结构来说,减少测试功耗主要通过优化测试矢量来实现,而测试矢量生成技术是指产生确定性测试矢量的技术。

测试矢量生成方式在生成测试模式时,除了要达到传统的ATPG目的,还需考虑降低测试期间的功耗。基于ATPG的方法又分为2种:①集成的ATPG优化方法,该方法的测试模式在测试生成期间进行低功耗优化;②ATPG之后的优化方法,该方法的测试模式首先由传统的ATPG生成,然后再进行功耗优化。

(1)与模拟退火算法相结合测试矢量生成的步骤是:首先根据模拟退火算法将测试模式分组成若干个有效测试矢量组与无效测试矢量组两部分;然后根据算法原理,生成控制LFSR运行的控制码;在这些控制码的作用下,LFSR就跳过大量的无效测试矢量,生成由有效测试矢量构成的精简的测试矢量序列。其基本流程如图4所示。

(2)与进化算法相结合依据测试矢量生成技术原理,采用基于遗传算法的测试模式生成器,用于计算冗余的测试模式。在冗余测试模式中,一个故障由几个不同的序列覆盖。然后使用一个优化算法,从前面已计算过的测试序列组合中选择一个最佳子集,使其峰值功率最小,而不影响故障覆盖率。参考文献采用ISCAS’85Bench—mark中的组合电路作为实验电路,在保持故障覆盖率不变的情况下,对待测电路的测试功耗a与使用模拟退火算法的BIST结构的测试功耗b相比较,得到的结果如表2所示。

由表2可知,满足相同故障覆盖率时,采用模拟退火算法分组测试矢量后,WSA大幅降低,总的WSA改善率在73.44%"94.96%之间。由于减少测试矢量,测试时间也大为缩短。

4 结语

采用线性反馈移位寄存器生成测试矢量的BIST结构可分为test—per—scan和test—per—clock两大类,相应的实现低功耗BIST测试方法也分别针对test一per—scan和test—per一clock结构。对tesl—per-scan结构模式,减少测试功耗主要通过优化扫描链来实现;对于test—per-clock结构模式,减少测试功耗主要通过优化测试矢量来实现。test—per—scan技术引起的面积开销较小,测试结构简单,易于扩展;而test—per—clock在一个周期内可实现矢量的生成和响应压缩,能够完成快速的测试。当然,随着测试功耗研究的深入,将会有更好的方法使功耗、故障覆盖率、系统性能等问题达到最优。

上一篇:是德科技信号生成软件将加快5G开发与测试速度

下一篇:USB 3.0物理层的一致性测试简介 -- 接收端测试简介(下)

推荐阅读最新更新时间:2024-03-30 22:54

Nordic nRF52840为低功耗蓝牙智能手表提供全天候运动追踪

Nordic Semiconductor宣布总部位于深圳的智能可穿戴设备企业深圳市爱都科技有限公司选择使用Nordic的nRF52840低功耗蓝牙 (Bluetooth® Low Energy /Bluetooth LE)先进多协议芯片级系统 (SoC) 为其集成GPS芯片的“ID205G”智能手表提供核心处理能力和无线连接。 这款可穿戴设备配置1.3英寸TFT-LCD彩色触摸屏,内置心率传感器、加速度计和陀螺仪,专为需要时尚智能手表外形和详细健康及健身数据监测的用户而设计。nRF52840 SoC的64MHz、32位Arm®Cortex®M4处理器带有浮点单元(FPU),提供充足的计算能力来运行复杂的传感器算法,使得这款智能

[物联网]

动态电压与频率调节在降低功耗中的作用

1 DVFS的工作流程 现在,为了延长便携式设备(如手机、MP3、多媒体播放器、笔记本电脑等)的电池寿命,芯片厂商们正在绞尽脑汁开发新的节电技术。简单地说,这些节电技术可以分为两类——动态技术和静态技术。静态技术包括不同的低功耗模式,芯片内部不同组件的时钟或电源的按需开关等。动态技术则是根据芯片所运行的应用程序对计算能力的不同需要,动态调节芯片的运行频率和电压(对于同一芯片,频率越高,需要的电压也越高),从而达到节能的目的。该技术的理论依据是如下的公式: 从上面的公式可以看出,降低频率可以降低功率,但是单纯地降低频率并不能节省能量。因为对于一个给定的任务,F*t是一个常量,只有在降低频率的同时降低电压,才能真正地降低能量的消

[应用]

蓝牙低功耗市场战火热 众大厂争推SoC方案

蓝牙低功耗(Bluetooth Low Energy)芯片市场战况日益激烈。看好智能配件(Appcessory)市场成长商机,包括博通(Broadcom)、ROHM集团旗下的LAPIS 半导体、意法半导体(ST)、赛普拉斯(Cypress),以及戴乐格(Dialog)半导体等业者,皆竞相于今年推出蓝牙低功耗系统单芯片(SoC)解决方案,让市场竞争战火急遽升温。 Nordic产品管理总监Thomas Embla Bonnerud强调,nRF51系列蓝牙低功耗SoC 具备创新的硬体与软体架构,为该公司拓展智能配件市场的重要利器。 Nordic产品管理总监Thomas Embla Bonnerud表示,愈来愈多半导体厂已

[模拟电子]

艾迈斯推出高精确度、超低功耗、小尺寸新型温度传感器

2016年6月22日,全球领先的高性能模拟IC和传感器供应商艾迈斯半导体(ams AG)推出一款业界领先的数字温度传感器,采用小型封装且具备低功耗和高精度。 在每秒采样4次时,采用1.6mmx 1mm封装的AS6200典型电流为6 A,其数字化测量输出可精确到 0.4 C。 工厂对集成在单芯片中的AS6200就温度传感系统所需的功能进行了校准,因此用户能够轻松地将该传感器设计进空间受限或电池供电的产品中。 该设备由硅带隙传感器、模拟数字转换器、数字信号处理器和一个串行I2C接口组成。芯片上的DSP可以进行所有线性化校准,并产生一个12位(0.0625 C分辨率)的二进制输出。 AS6200_Blockdiagra

[传感器]

安森美扩展蓝牙低功耗微控制器(MCU)系列到汽车无线应用

安森美扩展蓝牙低功耗微控制器(MCU)系列到汽车无线应用 NCV-RSL15结合行业最低功耗以及最新安全加密技术,用于车辆接入、胎压监测等 2023 年 3 月15 日—领先于智能电源和智能感知技术的安森美 推出采用蓝牙低功耗联接的超低功耗车规级无线微控制器。随着传感器数量和车载通信的增加,汽车制造商越来越倾向于使用无线连接技术,以减少布线成本和重量,NCV-RSL15是其理想选择 。另一方面,传感器部署数量上升可能会导致网络攻击次数随之增加,加剧安全问题。使用这款新型微控制器可解决这类安全隐患。 虽然胎压监测系统(TMS)和其他感知应用中的传感器和一般功能清单不断增长,但功耗预算却没有增加。同时,现在有些应用要求

[汽车电子]

msp430f149的低功耗模式

430的低功耗确实很强啊,虽然和VR单片机比起来速度慢了好多。在CPU进行工作时,如果没有什么事情干,就得进入低功耗模式啦,LMPX(0~4)这几种模式的具体事项就是如下的,得记住了。 一,运行模式 MSP430具有一种活动模式和五种软件可选的低功耗运行模式。一个中断事件可以将芯片从五种低功耗模式中的任何一种唤醒,为请求服务并在从中断程序返回时恢复低功耗模式。下面6种运算模式由软件配置。 ● 活动模式AM: -所有时钟活动 ● 低功耗模式0(LPM0) -CPU关闭 ACLK和SMCLK保持活动,MCLK关闭 ● 低功耗模式1(LPM1) -CPU关闭 ACLK和SMCLK保持活动,MCLK关闭 如果DCO在活动模式中没有

[单片机]

基于STM32L低功耗穿载式手环方案

针对 物联网 (IOT)方案, 意法半导体 (ST Microelectronic)推出了具备高性能、低功耗、低成本特性的STM32系列产品,采ARM Cortex-M架构。低耗电产品可以26~33DMIPS驱动,一般产品则具38~63DMIPS的性能。高性能产品则提供150~225DMIPS效能,并内建LCD控制器,可以低功率控制显示器。每颗价格仅32美分,让低阶型装置也能实现优越的性能。而智能型手环加速测量运动量和移动距离。温度和高度等也可利用传感器测量。微控制器(MCU)芯片可处理数字讯号,并转换成有意义的数据。 【系统功能】 -信号测量 :使用ST 位移侦测组件(LIS3DH/LIS2DH12)来侦测感应用户

[单片机]

TI 推出采用SC70-3封装的5uA低功耗系列电压基准产品

该器件提供高精度与出色低温度漂移 2007 年 10 月 9 日,北京讯 日前,德州仪器 (TI) 宣布推出一系列 5uA 低功耗系列电压基准产品,该系列产品具备高精度(最大 +/-0.15 %)、低温度失调(最大 30ppm/C)、SC70-3 封装(比 SOT23 小 40%)等多种出色特性。微小型封装与低流耗的完美结合使 REF33xx 产品系列理想适用于电池供电的便携式消费类应用,而且高精度与低温度失调特性更使其成为多种应用的理想选择,其中包括医疗设备、手持式仪表、测试设备以及数据采集系统。(更多详情,敬请访问: http://focus.ti.com.cn/cn/docs/prod/folders/print/ref

[新品]

小广播

热门活动

换一批

更多

最新测试测量文章

更多精选电路图

更多热门文章

更多每日新闻

- 新突破!超高速内存,为英特尔至强6性能核处理器加速

- 将vRAN站点整合至单服务器,助力运营商降低总体拥有成本

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

更多往期活动

11月18日历史上的今天

厂商技术中心

ESP32-C6 系列芯片手册

ESP32-C6 系列芯片手册 控制之美(卷1)——控制理论从传递函数到状态空间

控制之美(卷1)——控制理论从传递函数到状态空间

京公网安备 11010802033920号

京公网安备 11010802033920号