在直流无刷电机(BLDC)控制系统中,对电机转速的测量是一项重要且关键的问题。目前存在多种测速手段:利用编码器测速、利用霍尔(HALL)信号测速、利用电机反向电动势测速等等。其中,利用编码器测速方法的优点可以达到高分辨率的要求,但需增加成本和体积;利用电机反向电动势测速的优点是无需提供额外硬件接口,缺点是测速软件算法复杂。本文介绍了一种利用HALL信号、基于TMS570处理器NHET功能的BLDC测速软件设计方案,此方案可实现速度测量精度和软硬件复杂程度之间的平衡,同时在软件设计过程中采用提高可靠性的算法确保速度测量的可靠和准确。

1 TMS570处理器及NHET功能简介

TMS570系列处理器是TI公司推出的一种面向高性能交通运输领域的安全MCU,该系列MCU基于ARMCortex—R4F内核架构,具有较高的性能并满足IEC61508SIL-3的安全要求,主要应用于汽车工业,如刹车防抱死系统(ABS)、电助力转向(EPS)、HEV/EV逆变器系统。

TMS570系列处理器集成了第4代高端定时器(NHET),NHET使用高分辨率硬件通道并提供针对实时环境下的精确周期、脉冲测量功能、输出比较功能、PWM功能。NHET采用独立的指令结构和“时序决议循环”机制使时间分辨率达到ns级别,完全满足各种高精度时间测量应用需要,其内部集成可编程的抑制滤波器,确保测量数据的可靠性要求。

2 BLDC测速硬件接口设计

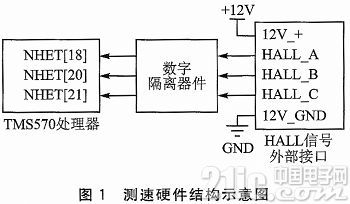

测速硬件结构示意图如图1所示。BLDC硬件测速接口设计较为简单,将HALL信号进行数字隔离后,直接接入TMS570的NHET引脚即可,将3个HALL信号同时引入NHET进行测速是一种硬件冗余设计,其目的是提高BLDC速度测量的可靠性,防止由于单通道HALL输入信号失效导致整个测速功能无法完成的情况发生。

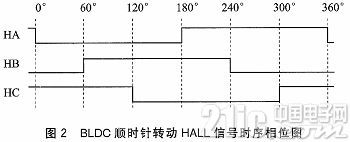

HALL信号输入采用DC 12 V电平,经数字隔离后输出DC 3.3 V电平,直接作为MCU输入。当BLDC转动时,HALL信号的时序与相位关系如图2所示。

由图2可知:BLDC转速可通过测量单个HALL信号的频率计算得出,BLDC转速(RPM,转/分钟)与HALL信号频率(fFO,Hz)、BLDC磁极对数(Poles)之间的关系式为:

3 NHET测速软件设计

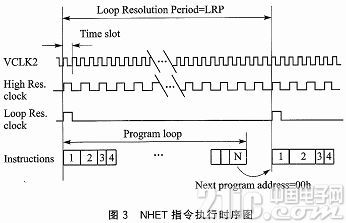

NHET测速软件的核心测速代码采用独立的指令结构和时序决议机制实现,NHET采用精简指令集(RISC)结构,包含22条指令,使用NHET汇编器将指令代码生成C语言结构的代码,需在运行之前由应用程序拷贝到NHET RAM中,NHET汇编器同时生成.h文件,由应用程序对测量数据进行访问,时序机制如图3所示。

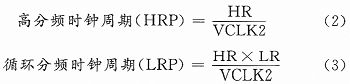

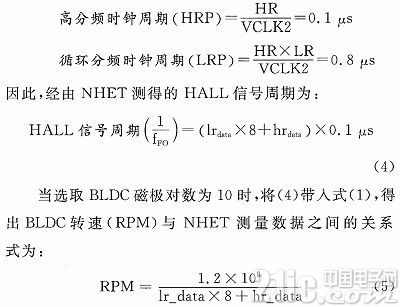

NHET时钟由VCLK2驱动,每个VCLK2周期称为一个“时隙”(Time slot),将VCLK2进行高分辨率分频(High Res.clock)和循环分频(Loop Res.clock)后得到高分频时钟、循环分频时钟,这两个时钟的周期为:

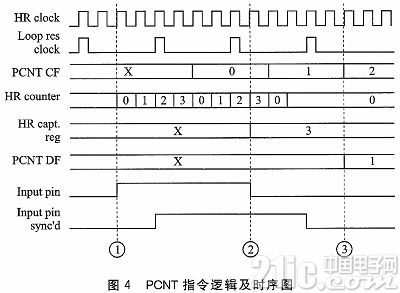

在此程序循环中包含1~N条NHET指令。由于不同的指令代码执行时间不同,在设计时应注意程序循环内所有代码执行时间的和不能超过一个循环分频时钟周期。由上文所述,利用BLDC的霍尔信号测量转速,即测量霍尔信号的周期,使用NHET指令集中的PCNT指令实现,PCNT指令捕捉NHET输入引脚信号的边沿并使用高分辨率时钟进行周期计数,将周期时间数据存储在内部寄存器中供应用程序读取,以PCNT指令捕获输入脉冲信号时间为例,指令执行逻辑及时序如图4所示。

图4中①~③含义如下:

①当检测到输入引脚的上升沿后,HR计数器开始由零进行加计数,当计数器满后,向指令数据区加1,并从0重新开始计数;

②当检测到输入引脚的下降沿后,将HR计数器内的数据存入捕获寄存器(HR capt.reg);

③PCNT指令在同步输入信号(Input pin sync’d)由低变高后开始执行,在该信号由高变低后,得到数据区数据(lr_data)和捕获寄存器内的数据(hr_data)之和即为脉冲时间。

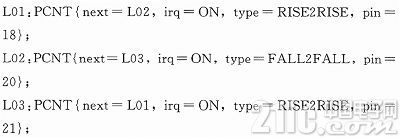

HALL信号的周期为HALL输入信号的上升沿到下降沿或下降沿到上升沿的时间,编写PCNT指令参数如下:

其中每一条指令对应一个通道的HALL输入信号,当指定引脚(pin)测量到一个完整的HALL周期后,产生一个NHET指令中断(irq=ON),信号触发的类型(type)包括上升沿到上升沿(RISE2 RISE)和下降沿到下降沿(FALL2FALL)两种,使用不同的信号触发类型测量HALL信号周期的目的是通过简单的软件代码异构保证测量结果的可靠性。

当VCLK2时钟为70 MHz时,选取高分频为7,循环分频为8,可得

为防止HALL信号因外界干扰产生的测量结果误差,除了使用NHET自身带有的硬件抑制滤波器外,在软件的设计过程中也应加入适当的滤波处理,保证测量结果的准确、可靠,使用一个系数为0.75的单极性I2R低通滤波器的C语言代码如下:

new_speed=((old_speed*3U)+new_speed)>>2U;

//新测得的速度占测量结果的1/4

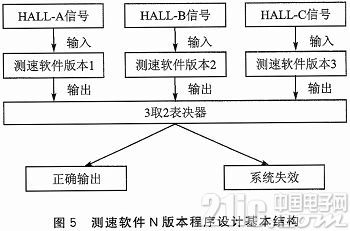

为提高测速软件的可靠性,软件采用结构容错的设计思路进行设计,由于测速硬件采用3通道冗余采集HALL输入信号,软件采用N版本程序设计方案。N版本程序设计是指对于一个给定的功能,由N(N>2)个不同的设计组独立编制出N个不同的程序,然后通过运行N个不同的程序得出结果并进行比较,输出正确的数据。基于TMS570 NHET功能测速软件N版本程序设计基本结构如图5所示。

结语

本文提出了一种基于TMS570系列处理器NHET功能的直流无刷电机测速软件设计方案,其中包括NHET测速原理介绍和代码实现、对测量结果的软件滤波算法设计、基于N版本软件容错设计方法提高软件可靠性。该测速方案已应用在采用TMS570LS20216处理器的自动门控制单元硬件之上,实际测试和应用的结果表明该方案切实可行。

上一篇:一种智能化吊舱地面检测系统

下一篇:基于CPCI图像采集器的制动片磨损检测系统设计

推荐阅读最新更新时间:2024-03-30 23:20

手把手教你学DSP:基于TMS320F28335

手把手教你学DSP:基于TMS320F28335 电机测速(有霍尔+磁钢或红外反射对管+黑白码盘做该实验)

电机测速(有霍尔+磁钢或红外反射对管+黑白码盘做该实验) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号