基本测试配置

图3给出了一种基本的C-V测量配置框图。由于C-V测量实际上是在交流频率下进行的,因此待测器件(DUT)的电容可以根据下列公式计算得到:

CDUT = IDUT / 2πfVac,其中

IDUT是通过DUT的交流电流幅值,

f是测试频率,

Vac是测得的交流电压的幅值和相位角。

换句话说,该测试是通过施加一个交流电压,测量电容两极之间的交流电流、电流电压和阻抗相位角,从而测得DUT的交流阻抗。

图3. C-V测量的基本测试配置

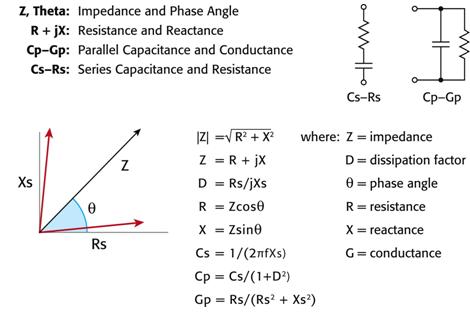

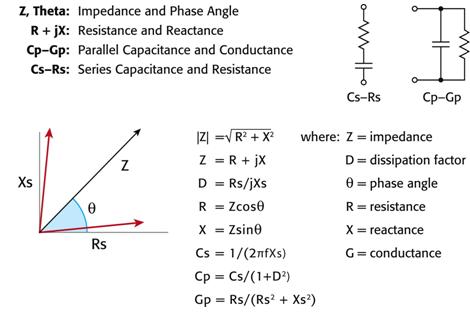

这些测量考虑了与电容串联和并联的电阻,以及损耗因数(泄漏)。图4给出了可以从这些测量中得到的主要电路变量。

Z,θ:阻抗与相位角

R+jX:电阻与电抗

Cp-Gp:并联电容与电导

Cs-Rs:串联电容与电阻

其中:Z=阻抗

D=损耗因数

θ=相位角

R=电阻

X=电抗

G=电导

图4. C-V测量得到的主要电气变量

成功C-V测量的挑战C-V测试配置的框图(图3)看起来似乎十分简单。但是,这种测试还存在着一定的挑战。一般而言,测试人员会在下列几个方面出现问题:

>低电容测量(皮法级和更小的电容值)

>C-V测量仪器与圆片器件的连接(通过探针)

>漏电容(高D)的测量

>使用硬件和软件采集数据

>参数提取

应对这些挑战需要特别注意与适当的硬件和软件一起使用的技术。

低电容测量。如果C较小,那么DUT的交流响应电流就较小并且很难测量。然而,在教高的频率下,DUT的阻抗就会降低,从而电流增大并更容易测量。半导体电容通常很低(小于1pF),低于很多LCR表的测量能力。即使那些声称能够测量这些小电容值的LCR表可能由于说明书模糊不清,也很难让人确定其最终的测量精度。如果没有明确说明处于仪器全量程之内的测量精度,那么用户就需要与制造商澄清这一问题。

高D(泄漏)电容。除了具有较低的C值之外,半导体电容可能还会产生泄漏。当等效的R与C并联值太低的时候就会出现这种情况。这会导致电阻性阻抗压倒电容性阻抗,C的大小被淹没在噪声中。对于采用超薄栅氧层的器件,D的大小可能会大于5。一般而言,随着D的增大,C的测量精度会迅速降低,因此高D值是C表在实际使用时的一个限制因素。此外,提高频率有助于解决这一问题。在较高的频率下,电容性阻抗较低,产生的C电流较大,比较容易测量。

C-V测量连接。在大多数测试环境中,DUT都是位于圆片上的某一测试结构:它通过探针、探针卡适配器和开关矩阵与C-V测量仪器相连接。即使不使用开关矩阵,也会用到探针和大量的连接线。在高频情况下,必须采用特殊校正和补偿技术。一般而言,这可以结合开路、短路或校正设备来实现。由于硬件结构、连线和补偿技术非常复杂,因此,实际测试之前最好与C-V测试应用工程师充分协商。他们使用过各种探测系统,对于解决各类互联问题富有经验。

获取有效数据。除了之前提到的精度问题之外,在采集C-V测量数据时实际需要考虑到问题还包括仪器测试参数的量程、参数提取软件的通用性以及硬件使用的方便性。一般的,C-V测试仅限于直流偏压30V和10mA左右。但是,很多应用,例如对LDMOS结构、低夹层电介质、MEM器件、有机TFT显示器和光电二极管进行特征分析,就需要测试更高的电压或电流。对于这类应用,需要单独的高压直流电源和C表;高达400V的分直流偏压和300mA的输出电流是非常有用的。如果能够将差分直流偏压加载到C-V测试仪的HI端和LO端,则能够更灵活地控制DUT内的电场,这对于新型器件(例如纳米级元件)的研究和建模是非常有帮助的。

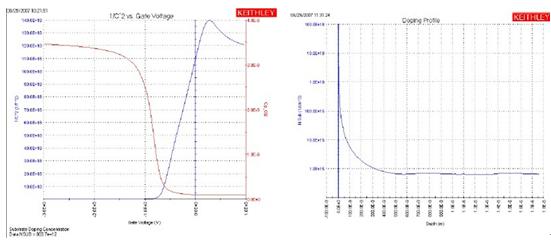

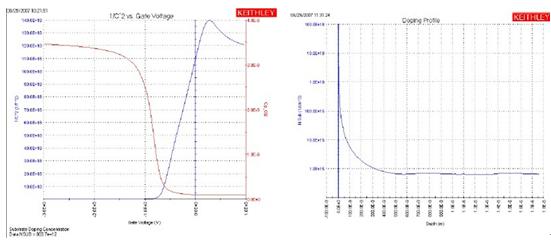

仪用软件应该能够直接运行测试例程,无需用户编程。这类软件应该适用于应用最广泛的器件技术和测试规程,正如本文前三段所提到的那样。有些研究人员可能还对一些不常见的测试感兴趣,例如对MIM(金属-绝缘层-金属)电容进行C-V和C-f扫描,测量圆片上的小互连电容,或者对双端纳米器件进行C-V扫描等。带自动绘图功能的参数提取工具应该容易获得。(如图5所示。)

图5.吉时利4200-SCS的参数提取实例给出了半导体的掺杂特征(左图中的蓝线),它与1/C2与Vg的关系曲线(红线)呈反相关系。右图给出了掺杂分布情况,即每立方厘米的载流子数量与衬底深度的函数关系。

通常,工程技术人员和研究人员都希望在测试仪器上不需要太多经验和培训就能够进行C-V测量,这就要求测试系统具有直观的用户界面和简单易用的特征。其中包括简单的测试配置、序列控制和数据分析。否则,用户在学习掌握系统上所花的时间就会超过采集和使用数据的时间。选择测试系统还应该考虑下列因素:

>紧密集成的源测量单元、数字示波器和C-V表;

>容易集成其他的外部仪器;

>探针尖具有高分辨率和精确测量能力(直流偏压低至毫伏,电容测量低至飞法);

>测试配置和库容易修改;

>能够帮助用户检查系统是否能够正常运行的诊断/故障排除工具。

关键字:半导体 C-V 测量入门

引用地址:半导体C-V测量入门(2)

图3给出了一种基本的C-V测量配置框图。由于C-V测量实际上是在交流频率下进行的,因此待测器件(DUT)的电容可以根据下列公式计算得到:

CDUT = IDUT / 2πfVac,其中

IDUT是通过DUT的交流电流幅值,

f是测试频率,

Vac是测得的交流电压的幅值和相位角。

换句话说,该测试是通过施加一个交流电压,测量电容两极之间的交流电流、电流电压和阻抗相位角,从而测得DUT的交流阻抗。

图3. C-V测量的基本测试配置

这些测量考虑了与电容串联和并联的电阻,以及损耗因数(泄漏)。图4给出了可以从这些测量中得到的主要电路变量。

Z,θ:阻抗与相位角

R+jX:电阻与电抗

Cp-Gp:并联电容与电导

Cs-Rs:串联电容与电阻

其中:Z=阻抗

D=损耗因数

θ=相位角

R=电阻

X=电抗

G=电导

图4. C-V测量得到的主要电气变量

成功C-V测量的挑战C-V测试配置的框图(图3)看起来似乎十分简单。但是,这种测试还存在着一定的挑战。一般而言,测试人员会在下列几个方面出现问题:

>低电容测量(皮法级和更小的电容值)

>C-V测量仪器与圆片器件的连接(通过探针)

>漏电容(高D)的测量

>使用硬件和软件采集数据

>参数提取

应对这些挑战需要特别注意与适当的硬件和软件一起使用的技术。

低电容测量。如果C较小,那么DUT的交流响应电流就较小并且很难测量。然而,在教高的频率下,DUT的阻抗就会降低,从而电流增大并更容易测量。半导体电容通常很低(小于1pF),低于很多LCR表的测量能力。即使那些声称能够测量这些小电容值的LCR表可能由于说明书模糊不清,也很难让人确定其最终的测量精度。如果没有明确说明处于仪器全量程之内的测量精度,那么用户就需要与制造商澄清这一问题。

高D(泄漏)电容。除了具有较低的C值之外,半导体电容可能还会产生泄漏。当等效的R与C并联值太低的时候就会出现这种情况。这会导致电阻性阻抗压倒电容性阻抗,C的大小被淹没在噪声中。对于采用超薄栅氧层的器件,D的大小可能会大于5。一般而言,随着D的增大,C的测量精度会迅速降低,因此高D值是C表在实际使用时的一个限制因素。此外,提高频率有助于解决这一问题。在较高的频率下,电容性阻抗较低,产生的C电流较大,比较容易测量。

C-V测量连接。在大多数测试环境中,DUT都是位于圆片上的某一测试结构:它通过探针、探针卡适配器和开关矩阵与C-V测量仪器相连接。即使不使用开关矩阵,也会用到探针和大量的连接线。在高频情况下,必须采用特殊校正和补偿技术。一般而言,这可以结合开路、短路或校正设备来实现。由于硬件结构、连线和补偿技术非常复杂,因此,实际测试之前最好与C-V测试应用工程师充分协商。他们使用过各种探测系统,对于解决各类互联问题富有经验。

获取有效数据。除了之前提到的精度问题之外,在采集C-V测量数据时实际需要考虑到问题还包括仪器测试参数的量程、参数提取软件的通用性以及硬件使用的方便性。一般的,C-V测试仅限于直流偏压30V和10mA左右。但是,很多应用,例如对LDMOS结构、低夹层电介质、MEM器件、有机TFT显示器和光电二极管进行特征分析,就需要测试更高的电压或电流。对于这类应用,需要单独的高压直流电源和C表;高达400V的分直流偏压和300mA的输出电流是非常有用的。如果能够将差分直流偏压加载到C-V测试仪的HI端和LO端,则能够更灵活地控制DUT内的电场,这对于新型器件(例如纳米级元件)的研究和建模是非常有帮助的。

仪用软件应该能够直接运行测试例程,无需用户编程。这类软件应该适用于应用最广泛的器件技术和测试规程,正如本文前三段所提到的那样。有些研究人员可能还对一些不常见的测试感兴趣,例如对MIM(金属-绝缘层-金属)电容进行C-V和C-f扫描,测量圆片上的小互连电容,或者对双端纳米器件进行C-V扫描等。带自动绘图功能的参数提取工具应该容易获得。(如图5所示。)

图5.吉时利4200-SCS的参数提取实例给出了半导体的掺杂特征(左图中的蓝线),它与1/C2与Vg的关系曲线(红线)呈反相关系。右图给出了掺杂分布情况,即每立方厘米的载流子数量与衬底深度的函数关系。

通常,工程技术人员和研究人员都希望在测试仪器上不需要太多经验和培训就能够进行C-V测量,这就要求测试系统具有直观的用户界面和简单易用的特征。其中包括简单的测试配置、序列控制和数据分析。否则,用户在学习掌握系统上所花的时间就会超过采集和使用数据的时间。选择测试系统还应该考虑下列因素:

>紧密集成的源测量单元、数字示波器和C-V表;

>容易集成其他的外部仪器;

>探针尖具有高分辨率和精确测量能力(直流偏压低至毫伏,电容测量低至飞法);

>测试配置和库容易修改;

>能够帮助用户检查系统是否能够正常运行的诊断/故障排除工具。

上一篇:找出影响低电压测量稳定性的误差源

下一篇:半导体C-V测量入门(1)

推荐阅读最新更新时间:2024-03-30 23:21

华引芯获得1.3亿元B1轮融资,聚焦高端半导体光源领域

近日,华引芯(武汉)科技有限公司(以下简称“华引芯”)宣布完成1.3亿元B1轮融资,投资方包括国中资本、天堂硅谷,德贵资本等。 华引芯官方消息显示,公司董事长孙雷蒙表示,本轮融资资金将主要用于华引芯自有研发实验室升级扩建,为客户提供芯片测试、封装检测、产品认证等一体化标准服务。华引芯将围绕高端半导体光源加大核心设备与材料的研发投入力度,提升产品性能及制造生产效率,并携手相关设备、材料供应商开拓创新高端半导体光源前沿技术,加码推进公司高端半导体光源的研发进程与量产化生产效能提升,助力公司稳步打开Mini/Micro LED商业化、特种光源、汽车光源市场战略布局。 华引芯成立于2017年,是一家专注于高端LED芯片与光器件研发、封

[手机便携]

欧洲半导体重建单靠砸钱是不够的

1450 亿欧元(约 1750 亿美元)是否足以重建到 2025 年能够制造领先制程(2nm)处理器的欧洲大陆半导体生态系统?来自欧洲17个国家的政治家们认为,用这种方式花钱也是一项至关重要的战略。 但是,单靠钱是不够的,需要文化变革。 在经历了数十年的全球竞争和全球化的下滑之后,重建欧洲半导体能力将具有战略意义。 首先,我们不应该低估手头的任务。因此,让我们将这项联合倡议的1450亿欧元(约1750亿美元)与三星计划用3nm技术赶上台积电(TSMC)进行比较。 据报道,三星计划花费1160亿美元。 这一家公司的预算几乎与欧洲的一样多,且7nm和5nm已经落后台积电了。与此同时,欧洲已经或多或少地放开了

[半导体设计/制造]

微软成立芯片设计部门 主攻语音识别XboxCPU

据美国《纽约时报》本周报道,全球最大的软件公司微软最近成立了芯片设计测试部门。业内专家认为,随着半导体“片上系统”的普及,软件和芯片行业必将出现更大程度的融合。 据报道,微软公司的这个部门目前暂定名“计算机架构集团”。该集团将分跨华盛顿州总部和作为美国半导体行业中心的加州硅谷地区。分别由两位在芯片行业有着丰富经验的技术高层领导。 计算机架构集团硅谷分部的领导人查尔斯·P·萨克尔对《纽约时报》表示,建立芯片设计部门的一个原因是为下一代的Xbox视频游戏机设计处理器,此外,语音时别芯片也是研发设计重点之一。其中,萨克尔表示:“语音是一个重大领域,你可以投入尽可能多的技术力量。” 在微软总部的芯片设计分部,另外一位资深科学家里奇·德

[焦点新闻]

政府扶植成效显现,中国半导体势力抬头

中国大陆半导体产业正快速崛起。受惠税率减免政策与庞大内需优势,中国大陆半导体产业不仅近年来总体产值与日俱增,且在晶圆制造设备和材料的投资金额也不断升高,并已开始迈入28奈米,甚至22/20奈米制程世代,成为全球半导体市场的新兴势力。 上海市集成电路行业协会高级顾问王龙兴指出,税赋优惠是中国大陆半导体产业蓬勃发展的重要助力。 上海市集成电路行业协会高级顾问王龙兴表示,中国大陆政府为全力扶持本土半导体产业,已祭出半导体设备、IC设计、晶片制造等企业获利前2年免税,及第3年税金减半的优惠措施,以减轻高科技产业在初期研发投资亏损的压力,因而让中国半导体产业得以向上发展。 除政策加持外,中国大陆对行动装置的需求愈来愈高,

[半导体设计/制造]

NI与中国本土伙伴加强合作,攻坚半导体测试市场

2019上半年,尽管全球半导体市场风起云涌,中国作为全球最大的半导体消费市场,仍然是全球半导体市场增长的引擎。从赛迪顾问发布的《全球半导体市场发展趋势白皮书》来看,2018年全球半导体市场规模达到4688亿美元,同比增长13.7%,市场规模创下历史新高,增速亦是2010年以来最快的年份之一。其中,中国占比最高,达到33.8%。 2019年,5G、AI等新兴技术将成为半导体市场增长的重要动力,驱动智能交通、智能制造、智慧医疗、智能家居、智慧生活等新应用,中国半导体市场将迎来重大发展机遇。终端应用的美好场景近在眼前,但全行业也必须面对终端应用对芯片提出的更高性能、更小尺寸、更低成本等的要求,这些无一不让从业者面临着更严峻的挑战。

[测试测量]

飞兆半导体举办第六届全球功率技术研讨会

飞兆半导体公司 (Fairchild Semiconductor) 将于9月起举办第六届全球技术研讨会,每个研讨会均为期一天,内容非常丰富,将为功率设计工程师提供开发 高能效 应用的设计技术、产品技术和行业发展趋势信息。 2008 至 2009年度 功率技术 研讨会的技术主题包括: · 通过修正的正弦脉宽调制 (PWM) 减小 BLDC 纹波扭矩 · PQFN封装的板级评测 · 不对称半桥转换器的设计考虑事项. · 高能效低待机功耗的辅助电源设计 · 从电源到变压器. · 在低输出电压的直流-直流转换器中,如何选择MOSFET 以减少损耗 · 错相式临界电流模式PFC转换器介绍

[电源管理]

意法半导体(ST)与ClevX扩大合作,推出面向安全设备的高安全性加密技术平台

横跨多重电子应用领域、全球领先的半导体供应商意法半导体和移动存储和移动设备知识产权技术创新开发企业ClevX,近日发布了符合FIPS 140-2 Level 3标准的面向安全应用的加密技术平台参考设计,这个基于STM32微控制器的加密平台采用商用芯片而非军用芯片,帮助设计企业和设备厂商研发符合FIPS标准的安全解决方案,适用于需要认证密码函数的安全应用。下面就随半导体小编一起来了解一下相关内容吧。 横跨多重电子应用领域、全球领先的半导体供应商 意法半导体 和移动存储和移动设备知识产权技术创新开发企业ClevX,近日发布了符合FIPS 140-2 Level 3标准的面向安全应用的加密技术平台参考设计,这个基于 STM32 微

[半导体设计/制造]

SEMI:九月半导体设备订单年成长率恢复正值

国际半导体设备材料产业协会(SEMI)最新发表的Book-to-Bill订单出货报告显示,2009年九月份北美半导体设备制造商三个月平均订单金额为7。328亿美元,订单出货比(Book-to-BillRatio,B/BRatio)为1。17。 该报告指出,北美半导体设备厂商九月份的三个月平均全球订单预估金额为7。328亿美元,较八月最终的6。145亿美元回升大幅回升19。3%,也比2008年同期成长12。8%。而在出货表现部分,九月份的三个月平均出货金额为6。246亿美元,较八月最终的5。8亿美元成长7。7%,但比去年同期的9。723亿美元少33%。 随着半导体产业景气好转,半导体相关设备的订单量也从今年第三季开始

[半导体设计/制造]

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号