1 引言

AD9833是ADI公司生产的一款低功耗,可编程波形发生器,能够产生正弦波、三角波、方波输出。波形发生器广泛应用于各种测量、激励和时域响应领域,AD9833无需外接元件,输出频率和相位都可通过软件编程,易于调节,频率寄存器是28位的,主频时钟为25MHz时,精度为0.1Hz,主频时钟为1MHz时,精度可以达到0.004Hz。

可以通过3个串行接口将数据写入AD9833,这3个串口的最高工作频率可以达到40MHz,易于与DSP和各种主流微控制器兼容。AD9833的工作电压范围为2.3V-5.5V。

AD9833还具有休眠功能,可使没被使用的部分休眠,减少该部分的电流损耗,例如,若利用AD9833输出作为时钟源,就可以让DAC休眠,以减小功耗,该电路采用10引脚MSOP型表面贴片封装,体积很小。

AD9833的主要特点如下:

频率和相位可数字编程;

工作电压为3V时,功耗仅为20mW;

输出频率范围为0MHz-12.5MHz;

频率寄存器为28位(在25MHz的参考时钟下,精度为0.1Hz);

可选择正弦波、三角波、方波输出;

无需外界元件;

3线SPI接口;

温度范围为-40℃-+105℃。

2 AD9833的结构及功能

2.1 电路结构

AD9833是一块完全集成的DDS(Direct Digital Frequency Synthesis)电路,仅需要1个外部参考时钟、1个低精度电阻器和一个解耦电容器就能产生高达12.5MHz的正弦波。除了产生射频信号外,该电路还广泛应外于各种调制解调方案。这些方案全都用在数字领域,采用DSP技术能够把复杂的调制解调算法简化,而且很精确。

AD9833的内部电路主要有数控振荡器(NCO)、频率和相位调节器、Sine ROM、数模转换器(DAC)、电压调整器,其功能框图如图1所示。

|

|---|

AD933的核心是28位的相位累加器,它由加法器和相位寄存器组成,每来1个时钟,相位寄存器以步长增加,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。正弦查询表包含1个周期正弦波的数字幅度信息,每个地址对应正弦波中0°-360°范围内的1个相位点。查询表把输入的地址相位信息映射成正弦波幅度的数字量信号,去DAC输出模拟量,相位寄存器每经过228/M个MCLK时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,这样就输出了一个正弦波。输出正弦波频率为:

fOUT=M(fMCLK/228) (1)

其中,M为频率控制字,由外部编程给定,其范围为0≤M≤228-1。

VDD引脚为AD9833的模拟部分和数字部分供电,供电电压为2.3V-5.5V。AD9833内部数字电路工作电压为2.5V,其板上的电压调节器可以从VDD产生2.5V稳定电压,注意:若VDD小于等于2.7V,引脚CAP/2.5V应直接连接至VDD。

2.2 功能描述

AD9833有3根串行接口线,与SPI、QSPI、MI-CROWIRE和DSP接口标准兼容,在串口时钟SCLK的作用下,数据是以16位的方式加载到设备上,时序图如图3所示,FSYNC引脚是使能引脚,电平触发方式,低电平有效。进行串行数据传输时,FSYNC引脚必须置低,要注意FSYNC有效到SCLK下降沿的建立时间t7的最小值。FSYNC置低后,在16个SCLK的下降沿数据被送到AD9833的输入移位寄存器,在第16个SCLK的下降沿FSYNC可以被置高,但要注意在SCLK下降沿到FSYNC上升沿的数据保持时间ts的最小和最大值。当然,也可以在FSYNC为低电平的时候,连续加载多个16位数据,仅在最后一个数据的第16个SCLK的下降沿的时将FSYNC置高,最后要注意的是,写数据时SCLK时钟为高低电平脉冲,但是,在FSYNC刚开始变为低时,(即将开始写数据时),SCLK必须为高电平(注意t11这个参数)。

当AD9833初始化时,为了避免DAC产生虚假输出,RESET必须置为1(RESET不会复位频率、相位和控制寄存器),直到配置完毕,需要输出时才将RESET置为0;RESET为0后的8-9个MCLK时钟周期可在DAC的输出端观察到波形。

AD9833写入数据到输出端得到响应,中间有一定的响应时间,每次给频率或相位寄存器加载新的数据,都会有7-8个MCLK时钟周期的延时之后,输出端的波形才会产生改变,有1个MCLK时钟周期的不确定性,因为数据加载到目的寄存器时,MCLK的上升沿位置不确定。

3 AD9833的引脚功能及时序

AD9833的引脚排列如图2所示,各个引脚的功能描述见表1。

|

|---|

|

|---|

AD9833的时序特性如图3、图4和表2所示。

|

|---|

|

|

4 AD9833的内部寄存器功能

AD9833内部有5个可编程寄存器,其中包括3个16位控制寄存器,2个28位频率寄存器和2个12位相位寄存器。

4.1 控制寄存器

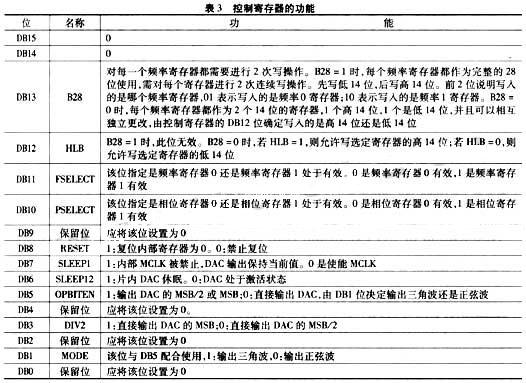

AD9833中的16位控制寄存器供用户设置所需的功能。除模式选择位外,其他所有控制位均在内部时钟MCLK的下沿被AD9833读取并动作,表3给出控制寄存器各位的功能,要更改AD9833控制寄存器的内容,D15和D14位必须均为0。

4.2 频率寄存器和相位寄存器

AD9833包含2个频率寄存器和2个相位寄存器,其模拟输出为

fMCLK/228×FREQEG (2)

其中:FREQEG为所选频率寄存器中的频率字,该信号会被移相:

2π/4096×PHASEREC (3)

其中,PHASEREC为所选相位寄存器中的相位字。

频率和相位寄存器的操作如表4所示。

|

|---|

|

5 应用设计

AD9833可应用在L15型飞机控制盒配套的检测盒中,利用AD9833产生频率可调的正弦波,以模拟机轮速度传感器的速度信号,从而对控制盒的刹车防滑通道能否正常的刹车防滑进行检测。

5.1 AD9833的硬件电路连接

检测盒设计以TI公司的TMS320LF2407A型DSP作为核心控制器,应用中需要2路速度信号,因此需要检测盒给出2路可独立调节的频率,图5示出TMS320LF2407A与AD9833的硬件连接。

|

|---|

外接有源晶体振荡器的输出送给2个AD9833作为主频时钟,DSP的SPI口采用主动工作方式,即用SPISIMO口发送数据,为了与AD9833的时序相配合,DSP的接口时钟(SPICLK信号)方式选择有延时的下降沿,IOPC3和IOPC5作为电路选通信号,IOPC3为低电平时U2被选通,此时对U1写数据无效;同理,IOPC53为低电平时U1被选通,此时对U2写数据无效。

5.2 软件程序

图6示出了AD9833的软件流程。

|

|---|

无论是写控制寄存器、频率寄存器还是相位寄存器、在写数据之前都需要把选通信号置为有效状态,这样写入的数据才会有效,否则无效。在DSP发送完1个数据字后将产生SPI中断请求,本设计中未使用中断方式,而且通过查询中断标志来跳出,并虚读DSP的接收缓冲器清除中断标志。

上一篇:MCF5282在电力系统监控中的应用

下一篇:ATMEGA48与DS1302组成的定时控制系统

推荐阅读最新更新时间:2024-05-13 18:13

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

- Melexis采用无磁芯技术缩小电流感测装置尺寸

- 千丘智能侍淳博:用数字疗法,点亮“孤独症”儿童的光

- 数药智能冯尚:ADHD数字疗法正为儿童“多动症”提供更有效便捷服务

- Vicor高性能电源模块助力低空航空电子设备和 EVTOL的发展

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

开关电源入门

开关电源入门 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号