提要

本应用指南介绍了在 VirtexTM-4 器件中实现存储器接口的直接时钟控制数据采集技术。直接时钟控制方案利用了 Virtex-4 系列所独有的某些架构特性(例如,每个 I/O 模块 (IOB) 中均具备一个 64-tap 的绝对延迟线)。

简介

大多数存储器接口都是源同步接口,从外部存储器器件传出的数据和时钟/ 选通脉冲是边沿对齐的。在 Virtex-4 器件采集这一数据,需要延迟时钟/ 选通脉冲或数据。利用直接时钟控制技术,数据经延迟,并与内部 FPGA 时钟实现中心对齐。在这个方案中,内部 FPGA 时钟采集传出的数据。存储器传出的时钟/ 选通脉冲用于决定与数据位相关的延迟值。因此,与选通脉冲相关的数据位的数量不受限制。由于无需将选通脉冲分配给相关数据位,所以不需要其他时钟资源。

时钟/ 选通脉冲和数据位使用的 Virtex-4 资源是一条 64-tap 绝对延迟线。该 64-tap 绝对延迟线可利用 IDELAY 和 IDELAYCTRL primitive 实现。时钟/ 选通脉冲和数据位均通过此 64-tap绝对延迟线来布线。虽然选通脉冲不用于采集数据,但它用于确定数据与内部 FPGA 时钟实现中心对齐所需的 tap 数量。以下部分将详细解释直接时钟控制技术方案的设计及实现。

选通脉冲边沿检测

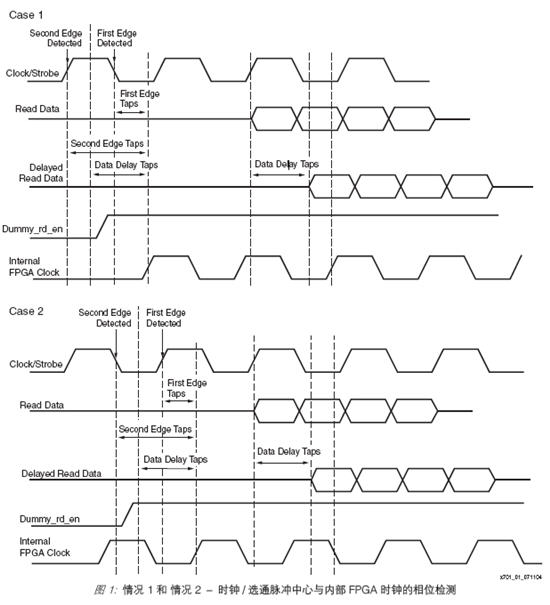

与时钟/ 选通脉冲相关的数据位的延迟值就是内部 FPGA 时钟上升沿与时钟/ 选通脉冲中心之间的相位差。假设时钟/ 选通脉冲和数据实现了边沿对齐。要确定这个相位差,时钟/ 选通脉冲通过 IOB 内的 64-tap 绝对延迟线输入,并利用内部 FPGA 时钟在增量 tap 输出端对其进行采样。

要确定时钟/ 选通脉冲的中心,至少需要检测到时钟/ 选通脉冲的两个边沿或转换。检测出第二次转换所需的 tap 数(即第二个边沿的 tap)和检测出第一次转换所需的 tap 数(即第一个边沿的 tap)之差,即为时钟/ 选通脉冲宽度。这个差值的二分之一就是脉冲中心(即脉冲中心的 tap)。从内部 FPGA 时钟上升沿到时钟/ 选通脉冲中心之间的 tap 数,即为第一个边沿的tap 数与脉冲中心的 tap 数之和。

表1 描述了各类 tap 数量。

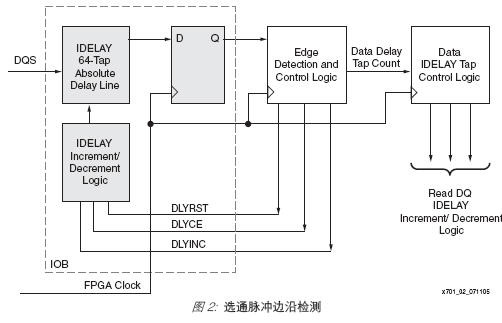

由于具有专用的 IDELAY 和 IDELAY_CTRL 电路,所以可以轻松地在 Virtex-4 器件中实现确定延迟值的电路。实现确定延迟值电路的结构图如图2 所示。

IDELAY 模块可用的 tap 总数为64。因此,当频率为 200 MHz 或以下时,将无法检测出两个边沿。如果在 64 tap 结束后仅检测出一个边沿,那么延迟数据所需的 tap 数应为,检测出第一个边沿所需的 tap 数减去 16 tap (约 1.25 ns,每个 tap 的延时约为 75 ps)。一个 200 MHz 时钟/ 选通脉冲周期的四分之一约为 16 tap。根据时序分析,该值也适用于更低的频率,最低可达 110 MHz。当频率低于 110 MHz 时,如果在 64 tap 结束后未检测出任何边沿,那么延迟数据所需的 tap 数应为 32 tap(约 2.5 ns,每个 tap 的延时约为 75 ps)。该值足以使内部 FPGA时钟边沿位于数据窗口内。

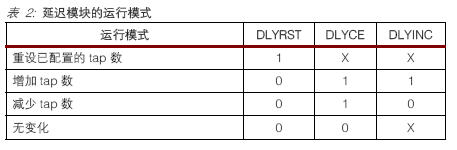

检测第一个和第二个边沿仅需一个小型状态机。只有在为确定数据延迟 tap 数而发出的虚读操作过程中,才启用该状态机。在正式工作之前,发送至外部存储器器件的虚读操作命令包含多条背靠背读命令。状态机将控制输入 IDELAY 电路的信号,即DLYRST、DLYCE 和 DLYINC。

DLYRST - 延迟线复位信号,将延迟线中的 tap 数重设为按 IOBDELAY_VALUE 属性设置的值。本设计中被设为 "0"。

DLYCE - 延迟线使能信号,确定何时激活延迟线递增/ 递减信号。

DLYINC - 延迟线递增/ 递减信号,可增加或减少延迟模块中的 tap 数。表2 描述了延迟线的运行模式。

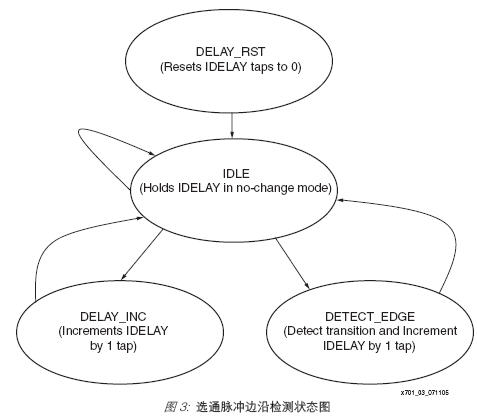

该状态是发起虚读操作时启用的状态机的第一个状态。在这种状态下,延迟模块被重设为“0”tap。该状态之后是多个 IDLE 状态。

IDLE

在这种状态下,延迟模块保持“无变化”运行模式。除 IDLE 状态之外,每种状态结束后都会出现数个 IDLE 状态,以便处理 tap 输出值。IDLE 状态之后是另一个 IDLE、DELAY_INC 或DETECT_EDGE 状态。

DELAY_INC

这个状态使延迟模块 tap 数加 1。该状态之后是数个 IDLE 状态。

DETECT_EDGE

在这种状态下,比较延迟模块的输出及其上一个值,用于检测信号边沿或转换,同时,延迟模块 tap 数加 1。该状态之后是数个 IDLE 状态。

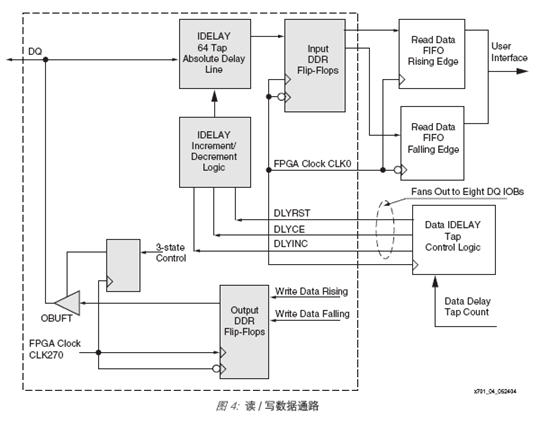

在确定了延迟数据所需的 tap 数后,将启用数据 IDELAY 电路,并增加到这一数值。按照所需的 tap 数,使数据 IDELAY 电路增加相同的时钟周期。数据 IDELAY 电路的读/ 写数据通路结构图如图4 所示。

如图4 所示,利用内部 FPGA 时钟,在输入 DDR 触发器中采集延迟数据。然后,把这些触发器的输出存储到两个 FIFO 中;一个代表上升沿数据,另一个代表下降沿数据。这些 FIFO 是利用 LUT RAM 实现的,其写使能操作由控制器生成的读使能信号提供,并在数据格式校准的基础上与采集的读取数据对齐。

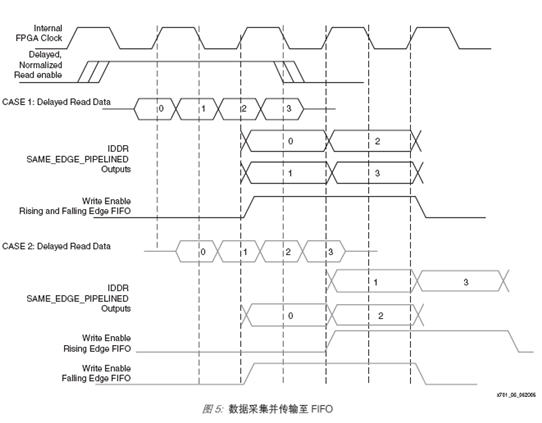

DDR2 SDRAM 器件并未随读取数据一同提供读有效或读使能信号。因此,控制器将根据 CAS延迟和突发长度,生成这个读使能信号。在开始执行读取操作时,必须令该读使能信号有效,并在选通脉冲的最后一个上升沿结束后使其无效。在 IDDR 触发器的输出端,该读使能信号必须与采集到的读取数据对齐。为了实现读使能对齐,在数据与 FPGA 时钟对齐后,将已知数据格式写入存储器。然后读回已知数据格式,并在读使能信号与采集到的读取数据对齐之前,利用移位寄存器延迟读使能信号。每字节数据都会生成一个读使能信号。图5 为读使能对齐的时序图。

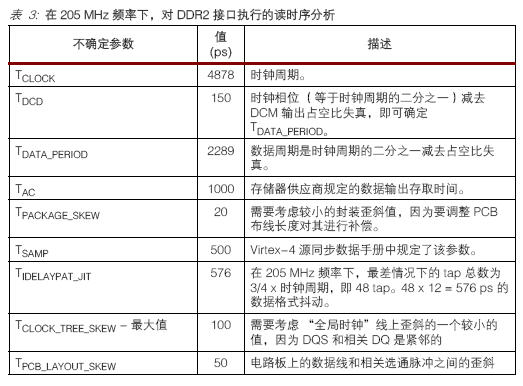

这一部分介绍了利用直接时钟控制技术实现的读时序分析。直接在 FPGA 时钟域内采集读取数据,因此,用于数据有效窗口分析的存储器参数就是存取时间 (TAC)。下面简要介绍了此时序分析中使用的各个参数。

此时序分析中考虑的外部存储器参数有:

TAC - 读取数据 (DQ) 的存取时间(以 FPGA 传递给存储器的时钟为参照)

TDCD - DCM 输出占空比失真

利用 FPGA 时钟而非存储器时钟/ 选通脉冲 (DQS),来采集读取数据 (DQ) ;因此,该分析考虑了 TAC (以时钟为参照的数据存取时间)。在此分析中,未考虑 DQS - DQ 存储器参数,如TDQSQ 和 TQHS,因为 TAC 比这两个参数更重要。

此时序分析中考虑的 FPGA 参数有:

TCLOCK_TREE-SKEW - 紧密放置在该组中的 IOB 触发器的全局时钟树歪斜

TPACKAGE_SKEW - 特定器件/ 封装的封装歪斜

TSAMP - Virtex-4 源同步数据手册中规定的采样窗口

TIDELAYPAT_JIT - Virtex-4 数据手册中规定的每个 IDELAY tap 的数据格式抖动

通过检测 DQS 边沿,计算出与 DQS 相关的数据位延迟。利用全局时钟在 I/O 触发器中采集DQS 来进行检测。因此,最终得到的数据延迟值已经包含了 I/O 触发器的建立时间和保持时间。在进行最差情况分析时,需要考虑 I/O 触发器固有的建立时间和保持时间。

此外,计算数据位和相关选通脉冲之间的歪斜也需要考虑 PCB 布局歪斜。

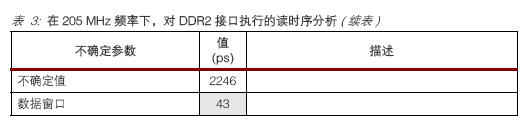

表3 所示为在205 MHz 频率下,对DDR2 接口执行的读时序分析。全部参数单位均为皮秒。

TDATA_PERIOD 是时钟周期的二分之一减去TMEM_DCD。TDATA_PERIOD 与不确定值之和的差,就是有效数据窗口 (43 ps)。因此,在 205 MHz 频率下,-11Virtex-4 器件将产生 43 ps 的余量。

存储器接口生成器 (MIG) 工具中集成了直接时钟控制数据采集技术的参考设计。该工具已被集成到 Xilinx Core Generator 工具中。最新版参考设计,可从 Xilinx 网站下载 IP 更新:http://www.xilinx.com/cn/xlnx/xil_sw_updates_home.jsp

结论

Virtex-4 I/O 架构增强了源同步存储器接口的实现。本应用指南及参考设计中使用的架构特性包括:

IDELAY 模块 - 连续校准的 tap 延时很小的延迟元件。

FIFO16 primitive - 用作 FIFO 的 Block RAM,无需使用生成状态标志所需的其他 CLB 资源。

高速差分全局时钟资源提供了更好的占空比。差分时钟减少了参考设计所需的全局时钟资源数量。

如欲了解更多赛灵思技术文档,请访问http://china.xilinx.com/china/documentation/

关键字:脉冲 延迟 采样 转换

引用地址:利用直接时钟控制技术实现存储器接口数据采集

本应用指南介绍了在 VirtexTM-4 器件中实现存储器接口的直接时钟控制数据采集技术。直接时钟控制方案利用了 Virtex-4 系列所独有的某些架构特性(例如,每个 I/O 模块 (IOB) 中均具备一个 64-tap 的绝对延迟线)。

简介

大多数存储器接口都是源同步接口,从外部存储器器件传出的数据和时钟/ 选通脉冲是边沿对齐的。在 Virtex-4 器件采集这一数据,需要延迟时钟/ 选通脉冲或数据。利用直接时钟控制技术,数据经延迟,并与内部 FPGA 时钟实现中心对齐。在这个方案中,内部 FPGA 时钟采集传出的数据。存储器传出的时钟/ 选通脉冲用于决定与数据位相关的延迟值。因此,与选通脉冲相关的数据位的数量不受限制。由于无需将选通脉冲分配给相关数据位,所以不需要其他时钟资源。

时钟/ 选通脉冲和数据位使用的 Virtex-4 资源是一条 64-tap 绝对延迟线。该 64-tap 绝对延迟线可利用 IDELAY 和 IDELAYCTRL primitive 实现。时钟/ 选通脉冲和数据位均通过此 64-tap绝对延迟线来布线。虽然选通脉冲不用于采集数据,但它用于确定数据与内部 FPGA 时钟实现中心对齐所需的 tap 数量。以下部分将详细解释直接时钟控制技术方案的设计及实现。

选通脉冲边沿检测

与时钟/ 选通脉冲相关的数据位的延迟值就是内部 FPGA 时钟上升沿与时钟/ 选通脉冲中心之间的相位差。假设时钟/ 选通脉冲和数据实现了边沿对齐。要确定这个相位差,时钟/ 选通脉冲通过 IOB 内的 64-tap 绝对延迟线输入,并利用内部 FPGA 时钟在增量 tap 输出端对其进行采样。

要确定时钟/ 选通脉冲的中心,至少需要检测到时钟/ 选通脉冲的两个边沿或转换。检测出第二次转换所需的 tap 数(即第二个边沿的 tap)和检测出第一次转换所需的 tap 数(即第一个边沿的 tap)之差,即为时钟/ 选通脉冲宽度。这个差值的二分之一就是脉冲中心(即脉冲中心的 tap)。从内部 FPGA 时钟上升沿到时钟/ 选通脉冲中心之间的 tap 数,即为第一个边沿的tap 数与脉冲中心的 tap 数之和。

表1 描述了各类 tap 数量。

由于具有专用的 IDELAY 和 IDELAY_CTRL 电路,所以可以轻松地在 Virtex-4 器件中实现确定延迟值的电路。实现确定延迟值电路的结构图如图2 所示。

IDELAY 模块可用的 tap 总数为64。因此,当频率为 200 MHz 或以下时,将无法检测出两个边沿。如果在 64 tap 结束后仅检测出一个边沿,那么延迟数据所需的 tap 数应为,检测出第一个边沿所需的 tap 数减去 16 tap (约 1.25 ns,每个 tap 的延时约为 75 ps)。一个 200 MHz 时钟/ 选通脉冲周期的四分之一约为 16 tap。根据时序分析,该值也适用于更低的频率,最低可达 110 MHz。当频率低于 110 MHz 时,如果在 64 tap 结束后未检测出任何边沿,那么延迟数据所需的 tap 数应为 32 tap(约 2.5 ns,每个 tap 的延时约为 75 ps)。该值足以使内部 FPGA时钟边沿位于数据窗口内。

检测第一个和第二个边沿仅需一个小型状态机。只有在为确定数据延迟 tap 数而发出的虚读操作过程中,才启用该状态机。在正式工作之前,发送至外部存储器器件的虚读操作命令包含多条背靠背读命令。状态机将控制输入 IDELAY 电路的信号,即DLYRST、DLYCE 和 DLYINC。

DLYRST - 延迟线复位信号,将延迟线中的 tap 数重设为按 IOBDELAY_VALUE 属性设置的值。本设计中被设为 "0"。

DLYCE - 延迟线使能信号,确定何时激活延迟线递增/ 递减信号。

DLYINC - 延迟线递增/ 递减信号,可增加或减少延迟模块中的 tap 数。表2 描述了延迟线的运行模式。

该状态是发起虚读操作时启用的状态机的第一个状态。在这种状态下,延迟模块被重设为“0”tap。该状态之后是多个 IDLE 状态。

IDLE

在这种状态下,延迟模块保持“无变化”运行模式。除 IDLE 状态之外,每种状态结束后都会出现数个 IDLE 状态,以便处理 tap 输出值。IDLE 状态之后是另一个 IDLE、DELAY_INC 或DETECT_EDGE 状态。

DELAY_INC

这个状态使延迟模块 tap 数加 1。该状态之后是数个 IDLE 状态。

DETECT_EDGE

在这种状态下,比较延迟模块的输出及其上一个值,用于检测信号边沿或转换,同时,延迟模块 tap 数加 1。该状态之后是数个 IDLE 状态。

在确定了延迟数据所需的 tap 数后,将启用数据 IDELAY 电路,并增加到这一数值。按照所需的 tap 数,使数据 IDELAY 电路增加相同的时钟周期。数据 IDELAY 电路的读/ 写数据通路结构图如图4 所示。

如图4 所示,利用内部 FPGA 时钟,在输入 DDR 触发器中采集延迟数据。然后,把这些触发器的输出存储到两个 FIFO 中;一个代表上升沿数据,另一个代表下降沿数据。这些 FIFO 是利用 LUT RAM 实现的,其写使能操作由控制器生成的读使能信号提供,并在数据格式校准的基础上与采集的读取数据对齐。

DDR2 SDRAM 器件并未随读取数据一同提供读有效或读使能信号。因此,控制器将根据 CAS延迟和突发长度,生成这个读使能信号。在开始执行读取操作时,必须令该读使能信号有效,并在选通脉冲的最后一个上升沿结束后使其无效。在 IDDR 触发器的输出端,该读使能信号必须与采集到的读取数据对齐。为了实现读使能对齐,在数据与 FPGA 时钟对齐后,将已知数据格式写入存储器。然后读回已知数据格式,并在读使能信号与采集到的读取数据对齐之前,利用移位寄存器延迟读使能信号。每字节数据都会生成一个读使能信号。图5 为读使能对齐的时序图。

这一部分介绍了利用直接时钟控制技术实现的读时序分析。直接在 FPGA 时钟域内采集读取数据,因此,用于数据有效窗口分析的存储器参数就是存取时间 (TAC)。下面简要介绍了此时序分析中使用的各个参数。

此时序分析中考虑的外部存储器参数有:

TAC - 读取数据 (DQ) 的存取时间(以 FPGA 传递给存储器的时钟为参照)

TDCD - DCM 输出占空比失真

利用 FPGA 时钟而非存储器时钟/ 选通脉冲 (DQS),来采集读取数据 (DQ) ;因此,该分析考虑了 TAC (以时钟为参照的数据存取时间)。在此分析中,未考虑 DQS - DQ 存储器参数,如TDQSQ 和 TQHS,因为 TAC 比这两个参数更重要。

此时序分析中考虑的 FPGA 参数有:

TCLOCK_TREE-SKEW - 紧密放置在该组中的 IOB 触发器的全局时钟树歪斜

TPACKAGE_SKEW - 特定器件/ 封装的封装歪斜

TSAMP - Virtex-4 源同步数据手册中规定的采样窗口

TIDELAYPAT_JIT - Virtex-4 数据手册中规定的每个 IDELAY tap 的数据格式抖动

通过检测 DQS 边沿,计算出与 DQS 相关的数据位延迟。利用全局时钟在 I/O 触发器中采集DQS 来进行检测。因此,最终得到的数据延迟值已经包含了 I/O 触发器的建立时间和保持时间。在进行最差情况分析时,需要考虑 I/O 触发器固有的建立时间和保持时间。

此外,计算数据位和相关选通脉冲之间的歪斜也需要考虑 PCB 布局歪斜。

表3 所示为在205 MHz 频率下,对DDR2 接口执行的读时序分析。全部参数单位均为皮秒。

TDATA_PERIOD 是时钟周期的二分之一减去TMEM_DCD。TDATA_PERIOD 与不确定值之和的差,就是有效数据窗口 (43 ps)。因此,在 205 MHz 频率下,-11Virtex-4 器件将产生 43 ps 的余量。

存储器接口生成器 (MIG) 工具中集成了直接时钟控制数据采集技术的参考设计。该工具已被集成到 Xilinx Core Generator 工具中。最新版参考设计,可从 Xilinx 网站下载 IP 更新:http://www.xilinx.com/cn/xlnx/xil_sw_updates_home.jsp

结论

Virtex-4 I/O 架构增强了源同步存储器接口的实现。本应用指南及参考设计中使用的架构特性包括:

IDELAY 模块 - 连续校准的 tap 延时很小的延迟元件。

FIFO16 primitive - 用作 FIFO 的 Block RAM,无需使用生成状态标志所需的其他 CLB 资源。

高速差分全局时钟资源提供了更好的占空比。差分时钟减少了参考设计所需的全局时钟资源数量。

如欲了解更多赛灵思技术文档,请访问http://china.xilinx.com/china/documentation/

上一篇:基于ARM的高速数据采集卡

下一篇:AMD四核处理器巴塞罗那的深度分析

推荐阅读最新更新时间:2024-05-13 18:38

精确的温度至比特转换器解决了温度传感器测量难题

温度,所有人都很熟悉,但却难以准确测量。在现代电子产品时代到来之前,伽利略(Galileo)发明了能够检测温度变化的基本温度计。两百年后,席贝克(Seebeck)发现了热电偶,这种器件能够产生以不同金属的温度变化率为函数的电压。如今,利用热电偶以及受温度影响的电阻元件(RTD和热敏电阻器)和半导体元件(二极管)以电子方式测量温度已较普遍。尽管从这些组件获取温度的方法已为大家熟知,但是以好于0.5℃或0.1℃的准确度测量温度依然富有挑战性。 要数字化这些基本传感器元件, 就需要专门的模拟电路设计、数字电路设计和固件开发技术。LTC2983将这些专门技术整合到单一IC中,解决了与热电偶、RTD、热敏电阻器以及二极管有关的每一种独特挑

[电源管理]

准谐振和谐振转换-两种提高电源效率的技术

全球对能源成本上涨、环保和能源可持续性的关注正在推动欧盟、美国加州等地的相关机构相继推出降低 电子 设备能耗的规范。交流输入 电源 ,不论是独立式的还是集成在电子设备中的,都会造成一定的能源浪费。首先,电源的效率不可能是100% 的,部分能量在电源大负载工作时被浪费掉。其次,当负载未被使用时,连接交流线的电源会以待机功耗的形式消耗能量。

近年来,对电源效率等级的要求日趋严格。最近,80% 以上的效率已成为了基本标准。新倡议的能效标准更是要求效率达到87%及以上。此外,只在满负载下测量效率的老办法已被淘汰。目前的新标准涉及了额定负载的25%、50%、75% 和 100% 这四个点的四点平均水平。同样地,最大允许待机功耗也

[电源管理]

示波器的采样率和存储深度

带宽、采样率和存储深度是数字示波器的三大关键指标。相对于工程师们对示波器带宽的熟悉和重视,采样率和存储深度往往在示波器的选型、评估和测试中为大家所忽视。这篇文章的目的是通过简单介绍采样率和存储深度的相关理论结合常见的应用帮助工程师更好的理解采样率和存储深度这两个指标的重要特征及对实际测试的影响,同时有助于我们掌握选择示波器的权衡方法,树立正确的使用示波器的观念。 在开始了解采样和存储的相关概念前,我们先回顾一下数字存储示波器的工作原理。 输入的电压信号经耦合电路后送至前端放大器,前端放大器将信号放大,以提高示波器的灵敏度和动态范围。放大器输出的信号由取样/保持电路进行取样,并由A/D转换器数字化,经过A/D转换后,信号变成

[测试测量]

飞思卡尔为太阳能应用展示电源转换技术新突破

模拟和电源管理集成电路的供应商飞思卡尔半导体将在本周召开的应用电力电子会议及展览(APEC)上演示用于光电(PV)应用的电源转换技术新突破。

飞思卡尔已开发了先进的超低电压DC-to-DC 转换器技术,实现了行业领先的太阳能电池启动和运行性能,启动电压只有0.32 V,而运行电压更是低至0.25 V。如果没有外部协助,大多数 IC都不能在电压低于晶体管典型启动电压(约0.7 V)时启动。这种限制减少了系统设计选项,增加了涉及超低电压的电源转换和能量恢复应用的复杂性。

飞思卡尔的电源转换技术使IC启动阈值降至0.32 V,效率达到将近90%。这种技术突破能够让开发人员经济高效地开发各种单

[模拟电子]

proteus与keil Cx51的单片机仿真(测量脉冲宽度)

利用门控位测试INT0引脚上出现的脉冲的宽度,并以机器周期数的形式通过发光二极管显示。 电路图: U1源程序: #include reg51.h sbit P1_1=P1^1; void main(void) { TMOD=0x02; EA=1; ET0=1; TH0=256-250; TL0=256-250; TR0=1; while(1); } void Time0(void)interrupt 1 using 0 {P1_1=~P1_1;} U2源程序: #include reg51.h #include intrins.h void main(void) { TMOD=0x0a; EA=1; ET0

[单片机]

派睿电子在华业务激增,推出新服务发展计划

2007年11月19日, 北京―― 国内领先的小批量、高品质电子元器件分销商派睿电子(Premier Electronics)日前宣布:自2007年4月推出引发中国电子设计业革命、颠覆性的“翌日到货”和“一站式” 现货采购新模式以来,其本土客户的数量实现了成倍的增长,货物的准确交付率屡创新高,从而实现了开拓中国小批量电子元器件分销市场的初期战略目标。 为更大程度上推进国内小批量电子元器件采购的发展,派睿电子携手国际顶级布线专家Molex,打造其在中国大陆地区规模最大的“产品集中营” ,即Molex为中国本土的工程师精选了1000余种最受本地欢迎的产品,翌日交付使用,创立了满足工程师需求的新服务模式。预计在不久的将来,国际顶级的电

[焦点新闻]

关于STM32F0系列多路ADC单独采样数据相同问题的处理

先看一下,大家认为“正确”的代码 void MYADC_init(void) { //时钟使能 RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOA, ENABLE); RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1, ENABLE); //GPIO配置 GPIO_InitTypeDef PORT_ADC; PORT_ADC.GPIO_Pin = GPIO_Pin_1 | GPIO_Pin_2 | GPIO_Pin_3; PORT_ADC.GPIO_Mode = GPIO_Mode_AN; PORT_ADC.GPIO_PuPd = GPIO

[单片机]

S3C2410 普通AD转换

一、AD转换基本原理 AD(Analog to Digital) 意思是:模—数转换,它是外部世界模拟信号和计算机之间联系的接口。它将连续变化的模拟信号转换为数字信号,以便计算机和数字系统进行处理、存储、控制和显示。 AD转换器是用来通过一定的电路将模拟量转变为数字量。模拟量可以是电压、电流等电信号,也可以是压力、温度、湿度、位移、声音等非电信号。但在AD转换前,输入到AD转换器的输入信号必须经各种传感器把各种物理量转换成电压信号。AD转换后,输出的数字信号可以有8位、10位、12位、14位、16位等。 S3C2410/S3C2440的CMOS模数转换器可以接收8个通道的模拟信号输入,并将它们转换为10位的二进制数据。

[单片机]

- 热门资源推荐

- 热门放大器推荐

-

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐 -

ICCV2023论文汇总:Faces and Gestures(人脸和手势识别)

ICCV2023论文汇总:Faces and Gestures(人脸和手势识别) -

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉)

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉) -

ICCV2023论文汇总:Document Analysis and Understanding(文档分析与理解)

ICCV2023论文汇总:Document Analysis and Understanding(文档分析与理解) -

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 -

微机原理与接口技术 第3版

微机原理与接口技术 第3版 -

随机信号分析(第二版)

随机信号分析(第二版) -

开关电容电路:从入门到精通

开关电容电路:从入门到精通

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

- 芯启源(上海)将持续发力,“做深做精”EDA及IP产品

- 本田严厉警告日产:若与鸿海合作,那么本田与日产的合作将终止

- Microchip推出新款交钥匙电容式触摸控制器产品 MTCH2120

- Matter对AIoT的意义:连接AIoT设备开发人员指南

- 我国科学家建立生成式模型为医学AI训练提供技术支持

- Diodes 推出符合车用标准的电流分流监测器,通过高精度电压感测快速检测系统故障

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 NE532N

NE532N

京公网安备 11010802033920号

京公网安备 11010802033920号